고온 동작용 SiC CMOS 소자/공정 및 집적회로 기술동향

Technology Trend of SiC CMOS Device/Process and Integrated Circuit for Extreme High-Temperature Applications

- 저자

-

원종일융합부품기술센터 moseho@etri.re.kr 정동윤융합부품기술센터 dyjung14@etri.re.kr 조두형융합부품기술센터 cdhengud@etri.re.kr 장현규융합부품기술센터 janghg@etri.re.kr 박건식융합부품기술센터 kunsik@etri.re.kr 김상기융합부품기술센터 sgkim@etri.re.kr 박종문융합부품기술센터 jmpark@etri.re.kr

- 권호

- 33권 6호 (통권 174)

- 논문구분

- 최신 반도체, 하드웨어 기술 동향 특집

- 페이지

- 1-11

- 발행일자

- 2018.12.21

- DOI

- 10.22648/ETRI.2018.J.330601

본 저작물은 공공누리 제4유형: 출처표시 + 상업적이용금지 + 변경금지 조건에 따라 이용할 수 있습니다.

본 저작물은 공공누리 제4유형: 출처표시 + 상업적이용금지 + 변경금지 조건에 따라 이용할 수 있습니다.- 초록

- Several industrial applications such as space exploration, aerospace, automotive, the downhole oil and gas industry, and geothermal power plants require specific electronic systems under extremely high temperatures. For the majority of such applications, silicon-based technologies (bulk silicon, silicon-on-insulator) are limited by their maximum operating temperature. Silicon carbide (SiC) has been recognized as one of the prime candidates for providing the desired semiconductor in extremely high-temperature applications. In addition, it has become particularly interesting owing to a Si-compatible process technology for dedicated devices and integrated circuits. This paper briefly introduces a variety of SiC-based integrated circuits for use under extremely high temperatures and covers the technology trend of SiC CMOS devices and processes including the useful implementation of SiC ICs.

Share

Ⅰ. 서론

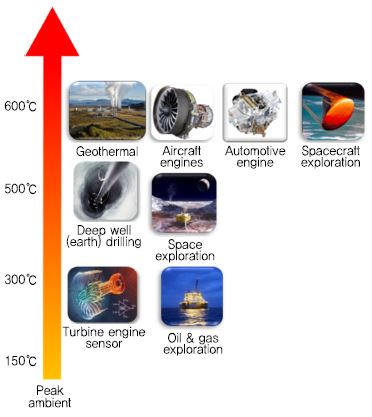

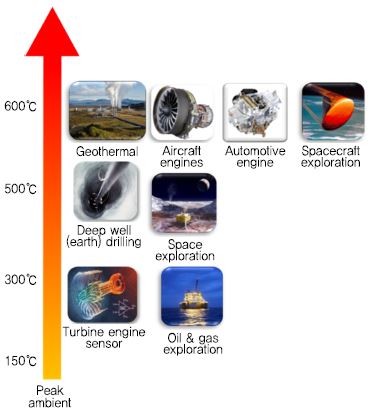

모든 전자/전기기기는 고온에서의 안정성 및 신뢰성 확보를 위해 산업용 85℃, 군수용 125℃ 이상의 온도 조건에서 동작이 요구되며, 항공전자, 자동차, 지구시추, 우주탐사 등 특정 분야에서는 온도범위가 250℃에서 최대 600℃이상까지 매우 높은 동작 온도가 요구되고 있다[(그림 1) 참조], [1]-[5].

현재 Si(Silicon) Bulk 기반의 CMOS(Complemen-tary Metal Oxide Semiconductor) 소자 공정기술은 집적회로를 구현하는데 가장 일반적인 기술로 125℃까지의 온도에서 안정성과 신뢰성이 높지만, 그 이상의 온도 에서는 캐리어 밀도 증가 및 캐리어 이동도, 전류밀도, 누설전류, 문턱전압 등의 성능에 직접적인 영향을 받아 트랜지스터가 큰 손상을 입기 때문에 정상적인 회로 동작이 어렵게 된다[5].

고온동작을 위한 Si Bulk CMOS 기술의 대안으로 SOI(Silicon on Insulator) CMOS기술을 이용한 제품들이 상용화되어 고온동작응용분야인 군수/항공우주산업의 마이크로프로세서, 메모리, 휴대통신 분야에 적용되고 있다. SOI CMOS는 일반적인 Bulk CMOS기술과 비교하여 고온에서의 누설전류를 궁극적으로 감소시킬 수 있어 225℃이하의 온도에서 동작특성이 검증되었다. 또한, 드레인 유도장벽감소특성(DIBL: Drain Induced Barrier Lowering)을 완화 시킬 수 있고, 전계분산효과가 우수하여 Short Channel CMOS기술에 적합한 웨이퍼로 알려져 있다[6], [7]. 그러나 225℃ 이상의 온도에서는 Si Bulk, SOI CMOS 역시 물리적인 제약이 따른다.

이에 따라, 300℃ 이상의 극한의 고온에서는 물리적 한계를 넘어서는 새로운 물질을 이용한 반도체기술이 필요하다. 이러한 극한의 고온환경에서 동작을 위한 대안 물질 중 하나로 SiC(Silicon Carbide)가 주목 받고 있다[2]-[5], [8].

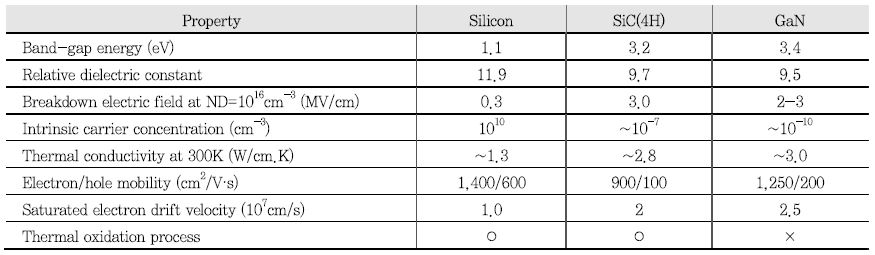

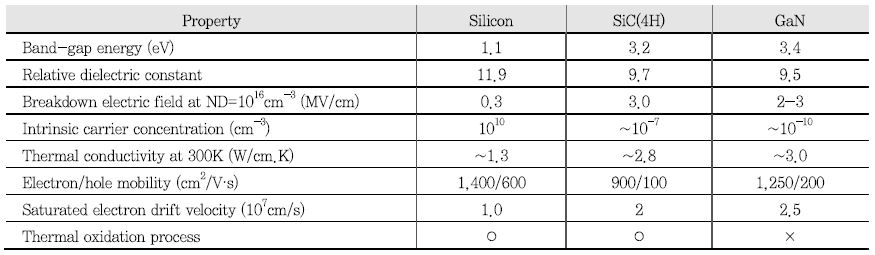

SiC는 화학적으로 Silicon 50%, Carbon 50%로 이루어졌으며, 약 200개 이상 많은 종류의 결정구조가 존재한다. 그 중에서 4H-SiC, 6H-SiC, 3C-SiC가 일반적인 반도체 소자로 제작하기에 적합한 재현성 있는 구조로 알려져 있다. <표 1>은 기판 재료에 따른 반도체 물성을 보여준다. SiC는 기존 Si 대비 높은 항복임계전계(Breakdown Electric Field), 넓은 밴드갭 에너지(Wide Band-gap Energy) 및 낮은 진성캐리어농도(Intrinsic Carrier Concentration) 특성으로 인해 고온 동작에 매우 유리한 물성을 가졌다[4], [5], [8]. 특히, Si 의 경우 고온에서는 높은 진성캐리어 농도로 300℃ 이상의 접합온도에서 동작이 제한되지만, 매우 낮은 진성캐리어를 갖는 SiC는 이론적으로 800℃ 이상의 동작이 가능하고, 실험적인 결과로는 600℃까지 동작이 검증되었다[3], [9]. 또한, SiC는 높은 열전도도와 접합 온도, 높은 항복임계전계의 특성을 갖고 있기 때문에 높은 전력밀도의 고효율 소자개발이 가능하다. 이러한 물성을 갖는 SiC로 전력변환기를 제작 했을 때 고속 스위칭 구현이 가능하기 때문에 부품(변압기, 인덕터, 캐패시터 등)의 크기와 변환기에서 발생되는 열과 에너지 손실을 획기적으로 줄일 수 있다. 따라서, SiC를 기반으로 고온동작이 가능한 소자 및 이를 구성으로 하는 집적회로의 개발이 끊임없이 이루어져 왔다. 본 고에서는 고온용 SiC기반의 소자/공정 및 집적회로(Integrated Circuit)에 대한 최신 기술을 소개하고, ETRI를 포함한 국내 기술동향에 대해 소개하고자 한다.

Ⅱ. 본론

1. SiC CMOS 소자/공정 기술동향

현재 반도체 집적회로의 대다수는 MOSFET(Metal Oxide Semiconductor Field Effect Transistor)소자로 이루어져 있으며, Si에서 MOSFET기반 집적회로의 큰 활용성과 성공을 감안했을 때 SiC 기판을 이용한 MOSFET 기반 집적회로를 구현하는 것은 전 세계적인 기술 트렌드로 인식되고 있다. SiC는 Si과 동일하게 열적산화막 성장이 가능하기 때문에 Si CMOS기술과 유사하지만, 극복해야 하는 가장 큰 2가지 이슈가 있다. 첫째, 게이트산화막 성장 후 잔류 탄소(Carbon)와 SiO2/SiC 계면에서의 높은 계면결함밀도 영향에 따른 낮은 채널 이동도와 낮은 신뢰성이다. 이러한 불완전한 게이트 산화막은 고온동작 시 결함을 더 악화 시켜 집적회로에 악영향을 미치게 된다. 둘째, 오믹 접촉(Ohmic Contact)은 SiC CMOS소자를 위한 필수 공정으로서 고온에서의 신뢰성 확보가 필수적이다. 소자동작온도가 Si, GaAs와 같이 재료의 물성에 의해 결정되는 것과 달리 SiC는 오믹접촉의 안정성에 동작온도가 제한되고 SiC 집적회로의 응답시간, 출력, 전력 등은 고온동작에서 오믹접촉의 신뢰성과 밀접하게 연관성이 있다. SiC 오믹접촉기술은 고온동작 집적회로의 성능을 결정짓는 중요한 요소 중 하나라고 말할 수 있다.

따라서, 본 장에서는 SiC CMOS 핵심 소자/공정의 최신 기술과 위에서 언급한 문제점들을 극복하기 위한 연구 및 현재까지의 기술수준에 대해 소개하고자 한다.

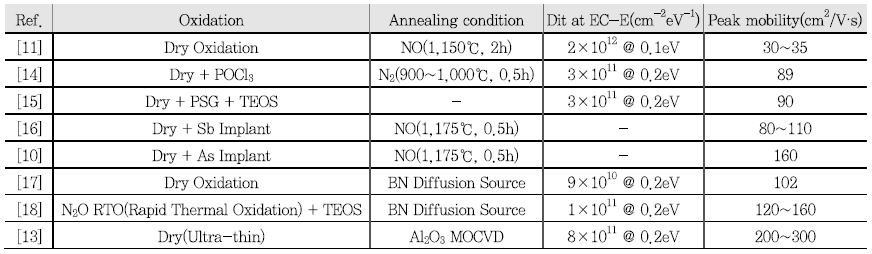

가. 계면 특성 및 채널 이동도 향상기술

SiC MOS 구조는 SiC/SiO2 계면에서의 결함들로 인해 오랜 시간 동안 문제를 겪어 왔다. 이들 결함은 계면 포획 밀도(Dit: Interface Trapped Density)로 나타내는데, 높은 계면 포획 밀도는 MOSFET의 이동도 저하, 불안정한 문턱전압(Vth shift) 등을 야기하여 소자의 성능을 저하시킨다. 따라서 이를 효과적으로 감소시키기 위한 연구들이 진행 중에 있다[10]-[18]. 본 절에서는 높은 채널 이동도를 달성하기 위한 절연막 성장 및 전후처리 기술에 중점을 둔 연구결과들에 대해 기술하였다.

• Nitridation

N2O(Nitrous) 및 NO(Nitric) 계열의 가스를 이용한 게이트 산화막 성장 및 후처리(POA: Post Oxidation Annealing) 공정이 Dit 감소를 위한 가장 일반적인 방법이다. 미국의 Auburn 대학에서는 건식 산화막 성장공정 이후 NO 분위기에서 열처리(1,175℃, 2시간)를 통해 약 35cm2/V·s의 이동도 특성을 보였고, N2O annealing을 통해 약 26cm2/V·s까지의 이동도가 달성되었다[11].

• Doped Gate Oxide

Nitridation process(NO or N2O)는 상용화된 SiC Power MOSFET에 적용 될 정도로 성숙된 공정 기술이지만, 여전히 채널이동도는 bulk 이동도의 5%일 정도로 매우 낮다. 따라서 Nitridation 방법 외에 게이트 산화막에 불순물을 도핑하는 기술도 매우 효과적인 SiC/SiO2 계면 passivation 방법으로 알려졌다. 그 중에서 가장 널리 알려진 기술인 인(P: Phosphorus)과 붕소(B: Boron)를 도핑에 이용하는 방법이다. 일본의 NAIST에서는 산화막 성장 후, POCl3 공정을 이용해 게이트 산화막에 P를 도핑하여 일반적인 NO 방법보다 높은 89cm2/V·s의 이동도 특성이 나타났다[14]. 이외에도 Phosphosilicate Glass(PSG)를 이용한 연구 결과도 보고 되고 있으며, 미국의 Auburn 대학에서는 PSG를 이용하여 3×1011cm-2eV-1 의 낮은 Dit와 약 90cm2/V·s의 이동도 특성을 얻었다[15]. 또한, 산화막 성장 전에 Counter Doping을 이용하여 효과적으로 Dit를 낮추는 연구도 보고되었으며, 대표적인 도핑불순물로는 Antimony [16], 비소(Arsenic)가 사용되어 최대 이동도가 각각 80~110cm2/V·s와 160cm2/V·s의 특성이 검증되었다.

또 다른 불순물로 도핑 된 산화막 기술로는 붕소(B: Boron)를 이용한 Passivation 방법이 있으며, 일본의 AIST에서 BN(Boron Nitride) 확산소스를 사용하여 Boron Passivation을 통해 약 102cm2/V·s 의 이동도 특성을 얻었다[17]. 스페인의 IMB-CNM에서는 N2O 산화막과 Boron Passivation의 조합으로 낮은 게이트 전압 영역뿐만 아니라 높은 전압에서의 이동도도 개선시켜 각각 7.5V의 비교적 낮은 게이트 전압에서 평균 160cm2/V·s의 이동도, 높은 게이트 전압(30V) 에서 120cm2/V·s의 이동도가 달성되었다[18].

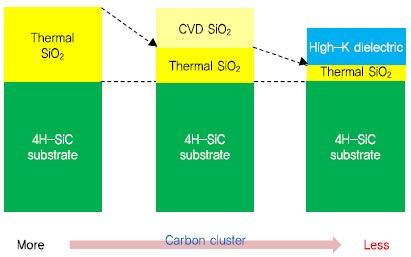

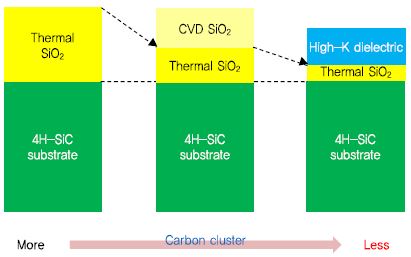

• High-k

산화막(SiO2)의 유전상수(k)는 4H-SiC에 비해 약 2.5배 낮기 때문에 산화막에 인가되는 전계(Electric Field)가 SiC보다 크다. 따라서 SiC와 비슷하거나 더 큰 유전상수 값을 갖는 물질을 게이트 절연막(Gate Dielectric Layer)으로 적용한다면 전계에 의한 스트레스를 감소 시킬 수 있다. 일반적으로 High-k 물질을 단독으로 사용하지 않고 수 nm의 얇은 산화막과 함께 구성되며 주로 High-k/SiO2/SiC 형태로 사용한다[(그림 2) 참조]. 대표적으로 High-k 물질 중 하나인, Al2O3는 SiC 결정과의 격자정합(Lattice Matching)이 매우 우수하고, 열 안정성과 밴드갭이 산화막과 유사하여 SiC MOSFET 게이트 절연막으로 사용하기 위한 대체 물질로서 많은 연구가 진행 중이다.

일본의 미쓰비시 연구팀은 Al2O3의 절연막을 이용하여 n-type의 SiC MOSFET을 제작한 결과 최대 300cm2/V·s의 높은 이동도를 검증했다. 그러나 높은 게이트 전압에서는 이동도가 약 40cm2/V·s까지 떨어지는 특성이 나타나 기존의 SiO2 기반의 MOSFET과 비슷한 이동도를 보였다[13]. 이 외에도 MgO, ZrO2, HfAlO, La2O3등 SiC 게이트 절연막의 대체를 위한 연구가 활발히 진행 중이다.

높은 채널 이동도를 달성하기 위한 절연막 성장 및 전후처리 기술에 대해 언급 된 내용을 <표 2>에 요약하여 나타내었다.

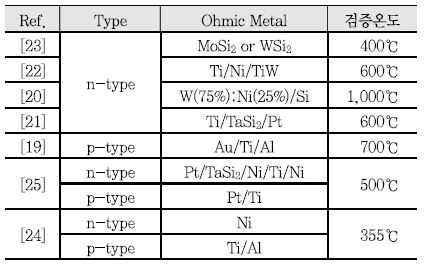

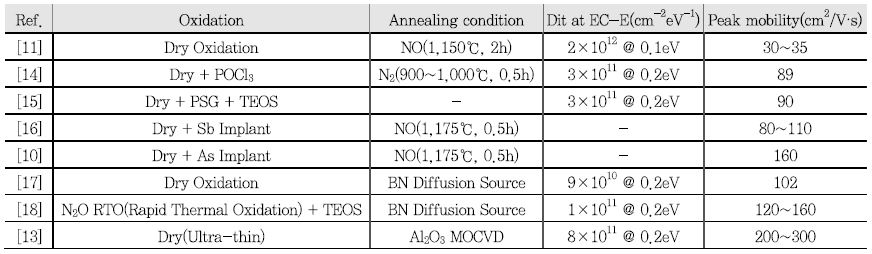

나. 오믹 접촉 형성 기술

고온동작을 위한 SiC 오믹접촉 기술개발은 니켈(Ni), 알루미늄(Al), 타이타늄(Ti)기반으로 활발한 연구가 이루어지고 있다. Ni과 Al기반의 오믹접촉은 각각 n-type과 p-type SiC에서 주로 사용되는 금속으로 고온안정성을 위해 다층의 금속을 합금으로 구성하여 사용하고 있다.

불가리아 응용물리연구소는 Al 기반으로 p-type SiC위에 Au/Ti/Al의 오믹금속 증착 후 합금(900℃에서 열처리)을 통해 2.3×10-5Ωcm2의 접촉저항 특성을 얻었고, 700℃에서 100시간 동안 접촉저항의 변화 없이 안정적인 특성을 보였다[19].

NASA의 Glenn 연구소는 W(75%):Ni(25%)/Si의 합금을 이용하여 1,000℃, 15시간동안 평균 2.3×10-5Ωcm2의 n-type 오믹접촉 저항으로 안정적인 특성이 검증되었다[20].

또한, Ti/TaSi2/Pt로 구성되는 멀티층의 합금을 통해 n-type 오믹접촉 1-6×10-5Ωcm2의 접촉저항 범위에서 600℃에서 1,000시간 동안의 안정성이 검증되었다[21]. 이 외에도 고온에서 동작하는 SiC 소자에 적용 되는 다양한 오믹접촉 형성기술 있으며 이를 <표 3>에 나타내었다.

다. SiC CMOS 소자 및 공정기술

SiC MOSFET소자의 낮은 이동도에 의한 특성저하를 개선하기 위한 방법으로 게이트 산화막을 언급했다. 그 외에도 이동도 향상을 위해 접근할 수 있는 방법 중 하나는 단채널(Short Channel)을 이용한 채널저항 감소 방법이다. 일본의 교토대학은 Sub-Micrometer(약 0.69μm)의 채널길이를 갖는 SiC NMOSFET 소자를 제작하여 SiC 결정면에 따라 최고 71cm2/V·s의 이동도를 얻었고, 채널길이 변화에 따른 Short Channel Effects 및 고온특성을 분석했다[26].

채널길이가 짧아지면서 SiC CMOS도 Si CMOS와 마찬가지로 Scale Down에 영향을 미치는 Punch-Through를 해결하는 기술이 필요하다. 미국의 모토로라 반도체 팀과 코넬대학에서 실험한 결과[27]에 의하면 PMOS의 채널길이는 0.8μm 이하에서 Punch-Through 특성이 나타났으며 Punch-Through Stop 이온주입을 통해 300℃에서 안정적인 문턱전압과 낮은 누설전류 특성을 확보했다. 또한, NMOS는 약 0.3μm 이하의 채널길이에서 Punch-Through 특성이 나타났으며 LDD(Lightly-Doped Drain)을 적용하여 Punch-Through를 억제 시켰다. 더욱이 N+ Source/Drain사이의 Charge Sharing Effect에 의해 온도에 따라서 문턱전압의 변화폭이 장채널(Long Channel) NMOS보다 더 작았다. 이 또한 300℃에서 특성을 검증했다.

한편, SiC 공정기술이 안정화되고 반도체 소자들의 성능 제어가 가능해지면서 고온 동작이 가능한 SiC Lateral MOSFET소자가 집적화 된 파운드리 형태의 SiC CMOS공정이 개발되고 있다. TI(Texas Instruments)는 CREE(현 Wolfspeed)의 2.0μm 4H-SiC 1,200V 전력 MOSFET 공정라인에서 제작된 저전압 (15~20V) Lateral MOSFET소자를 이용하여 Linear Voltage Regulator를 300℃에서 성능을 검증했다. CREE 공정라인은 PMOS없이 NMOS으로만 이루어졌기 때문에 Depletion mode NMOS를 이용했다[28].

Raytheon은 고온동작용 혼성신호 집적회로에 적합 한 1.2μm 15V SiC CMOS 공정(HiTSiC: High Tem-perature Silicon Carbide Process)을 개발했다. PMOS를 구현하기 위해 n+ 4H-SiC 기판위에 에피를 성장하고 p-Well과 n-Well 이온주입을 통해 접합을 형성하여 NMOS와 PMOS를 같은 기판에 집적화 했다[29]. 또한, 2개의 Polysilicon 박막을 사용하여 CMOS소자 외에도 Poly저항과 Poly to poly capacitor를 집적화 했고, 패키지 본딩을 위한 Gold 금속을 마지막(Finish Metal)으로 사용했다[30].

2. SiC 집적회로 기술동향

대표적인 SiC 집적회로의 단일소자는 MOSFET, JFET(Junction Field Effect Transistor), BJT(Bipolar Junction Transistor)로 분류 될 수 있다[3], [5], [8]. SiC BJT는 스웨덴의 왕립공과대학(KTH: Royal Institute of Technology)[31]-[34], JFET 및 MESFET은 미국의 Rutgers 대학[35], NASA(National Aeronautics and Space Administration)[36], 스페인의 IMB-CNM[37] 에서 연구 개발을 진행 중에 있으나, 본 고에서는 집적도, 소비 전력 등에서 장점을 가지는 CMOS 기반의 집적회로 기술에 대해 다루고자 한다.

가. 미국 Arkansas 대학, Ozark IC

미국 Arkansas 대학으로부터 spin-off한 Ozark IC사는 팹리스 기업으로써 Arkansas 대학과 협력하여 고온 동작용 all-SiC system 설계에 대해 활발히 연구개발을 진행 중이며, 영국 Raytheon사의 1.2μm SiC CMOS 공정(HiTSiC process)을 이용하여 제작하고 있다. 소자는 Berkeley Short-channel Insulated-gate field-effect transistor Models(BSIM)을 기본으로 SiC 특성에 맞춰 수정한 모델링을 사용했다.

2017년에 게재한 논문[38]에 의하면 3mm×0.8mm 크기로 고온 동작용 8-bit Digital-to-Analog Converter (DAC)을 개발하였으며, 8-bit DAC과 comparator, successive approximation register(SAR) logic block을 포함한 8-bit Analog-to-Digital Converter(ADC)를 3mm×2mm 크기로 개발하였다.

고온 테스트는 참고문헌[38]의 (그림 6c)와 같이 ceramic leaded chip carrier package와 rogers-45 PCB에 마운팅하여 테스트를 진행하였으며, 400℃의 온도에서 측정한 결과, differential nonlinearity(DNL)는 1.2LSB(least significant bit), integral nonlinearity (INL)은 2.7LSB를 얻었으며, offset error와 gain error도 2.7LSB와 4.9LSB의 성능을 얻었다. 이는 SiC CMOS 공정을 이용한 세계 최초의 DAC 결과라는 것에 의미가 있다.

ADC도 DAC과 동일한 측정 환경에서 평가를 진행하였으며, 그 결과, 400℃의 온도에서 DNL과 INL은 각각 3.6LSB와 -2.9LSB의 성능을 보였고, offset error와 gain error는 각각 -7.0LSB와 -2.6LSB의 성능을 얻었다. 또한 300℃에서 signal to noise and distortion ratio(SNDR)와 effective number of bits(ENOB)의 측정 결과, 각각 32.15dB와 5.05bit의 성능을 얻었으며, 이는 세계 최초로 300℃에서 SNDR과 ENOB의 성능을 평가했다는 것에 의미가 있다.

2017년에 게재한 논문[39] 및 2016년에 발표한 논문[40]에 의하면, 500℃ 이상에서도 SiC 전력소자를 구동시킬 수 있는 gate driver를 control logic과 4-stage buffer를 포함하여 5mm×4.5mm 크기로 개발하였으며, 측정 결과 500℃에서 rising time 과 falling time이 각각 74.2ns와 36.8ns였다.

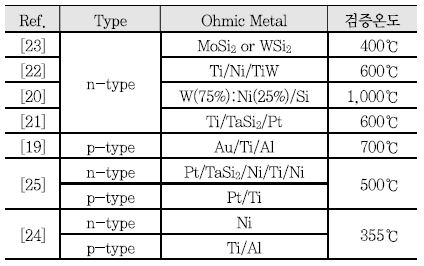

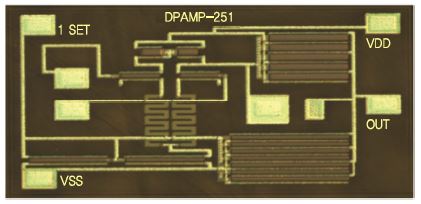

(그림 3)는 입력 전압 20~30V의 넓은 범위에서 15V의 전압을 출력하는 linear regulator로써, 400℃에서 100mA의 전류소모로 line regulation 및 load regulation은 각각 4mV/V와 420mV/A의 우수한 성능을 보여주었다.

(그림 3)

SiC CMOS 기반 linear voltage regulator

[출처] Reprinted from H.A. Mantooth et al., “Emerging Trends in Silicon Carbide Power Electronics Design,” CPSS Trans. Power Electron. Applicat., vol. 2, no. 3, Sept. 2017, pp. 161-169.

이 외에도 4-bit logic counter, Boolean finite state machine(FSM), Boolean ripple carry adder(RCA), ring oscillator(RO), Boolean shift register(SR) 등을 포함한 16종의 집적회로를 개발하여 2016년 IEEE Transactions on Device and Materials Reliability 에 게재한 바 있다[41].

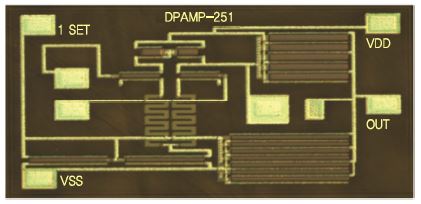

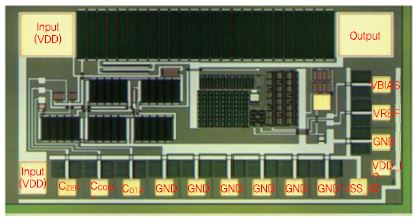

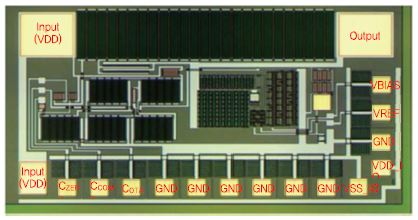

나. 일본 Hitachi 제작소

일본의 히타치 제작소는 자동차 산업 분야 및 원자력발전, 항공우주 산업 등 열악한 환경에서 센싱 데이터의 신호처리를 위해 고온과 방사선에 강한 SiC 기반의 CMOS 집적회로를 이용하여 (그림 4)와 같이 operational amplifier(OP amp.)를 개발했다[42]. 기존의 Si 기반의 CMOS 집적회로는 고온과 방사선에 영향을 받기가 쉬워 거친 환경이나 고온 방사선을 차폐하는 구조, 장거리 전송에 따른 데이터의 열화 및 설치 환경의 제한 등 문제를 해결 가능하게 되었다. 일반적으로 CMOS는 n형과 p형의 MOS로 구성되지만, SiC 기반의 PMOS는 NMOS에 비해 데이터 처리 성능이 낮은 이유 등으로 개발이 잘 진행되지 않았으나, 히타치는 SiC에 불순물 주입 및 열처리 가공 기술을 활용해 데이터 처리 성능을 향상시킨 NMOS를 개발하여 집적회로에 적용했다. 또한 방사선에 대한 저항력을 향상시키기 위해 집적 회로를 전기적으로 보호하는 절연막에 방사선의 영향을 완화하는 보호 전극을 삽입한 장치 구조를 채용했다. 이 기술을 이용하여 센서로부터의 신호를 증폭 처리하는 OP amp.의 신호 처리 성능을 유지하면서 기존 Si 기반의 OP amp. 대비 100배에 해당하는 성능을 보였다.

3. 국내 SiC 집적화 기술

본 절에서는 국내에서 진행된 SiC 집적화 기술에 대한 동향에 대해서 소개하고자 한다.

국내에서는 2000년대 초 충북대학교에서 최초로 6H-SiC기판을 이용하여 몰리브덴(Mo: Molybedenum) 게이트 SiC CMOS소자를 제작했고, 이를 통해 인버터회로를 고온에서 검증했다[43]. 고온환경(300℃)에서의 로직(Logic)회로 검증은 SiC PMOS의 낮은 이동도 및 높은 문턱전압으로 PMOS 대신 부하저항을 이용하여 특성을 확인했다.

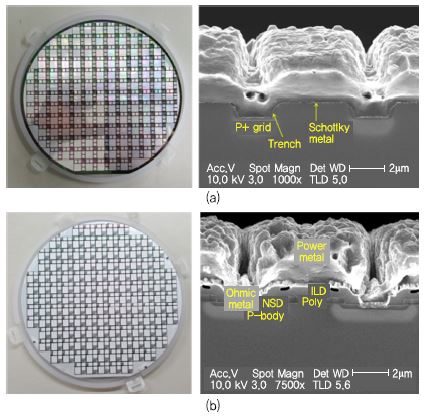

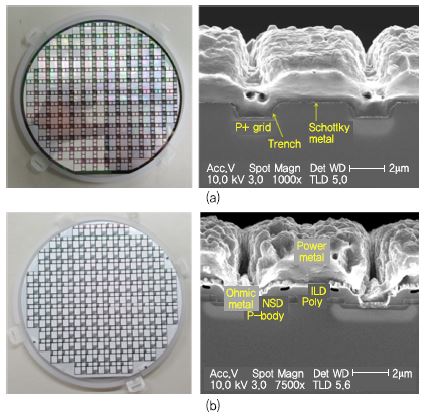

ETRI는 2015년부터 6인치 기반의 Trench형 SiC 전력소자(SBD: Schottky Barrier Diode, MOSFET)개발을 시작으로 현재까지 SiC 소자공정 관련 연구를 수행 중에 있다[(그림 5) 참조], [44].

(그림 5)

ETRI의 6인치 기반 SiC 전력소자 (a) SBD, (b) MOSFET 제작 웨이퍼 및 SEM단면도

[출처] 한국전자통신연구원, “SiC기반 트렌치형 차세대 전력소자 핵심기술개발 2017 연구보고서,” 2017.

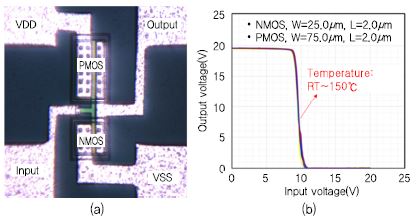

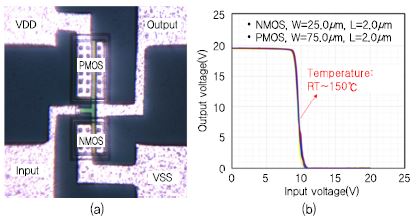

최근에는 CMOS 일괄공정이 가능한 ETRI 융합부품실험실 활용하여 SiC CMOS 소자 설계 및 공정기술을 개발 중에 있으며, 개발된 CMOS 인버터가 150℃에서 안정적으로 동작함을 확인하였다. 기존 국내기술과 다르게 PMOS를 동작시켜 인버터를 구동시킨 것에 의미가 있으며, 현재 300℃이상의 고온 동작 시험을 평가 중에 있다[(그림 6) 참조].

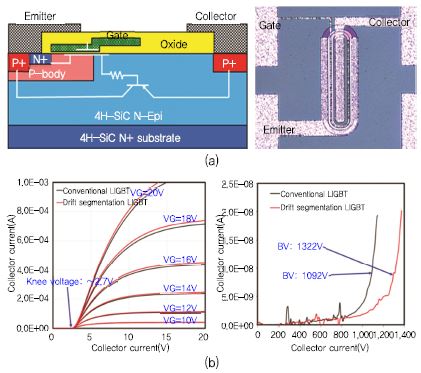

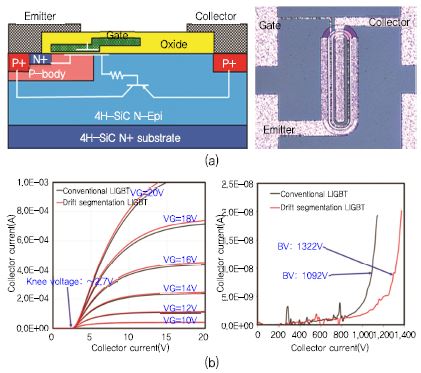

또한, 저전압의 SiC CMOS와 고전압소자를 집적화하기 위해 SiC LIGBT(Lateral Insulated Gate Bipolar Transistor) 소자를 제작하여 전기적 특성을 확인했으며, 이는 (그림 7)에 나타냈다. 1,000V 이상의 항복전압 특성이 나타나는 LIGBT소자는 SiC CMOS 소자와 함께 집적화 할 수 있어 고전압과 대전력이 요구되는 회로 구성이 가능하다[45].

Ⅲ. 결론

최근 항공전자, 자동차, 전력전자, 지구시추, 우주탐사 등 특정분야에서는 매우 높은 동작 온도가 요구되고 있어 물리적 한계를 넘어서는 새로운 물질을 이용한 반도체기술에 대한 필요성이 증가하고 있다. 따라서, 본고에서는 Si 또는 SOI의 대안으로 급 부상되고 있는 SiC 기반의 기술동향에 대해 기술하였다.

게이트 절연막 품질, 소자의 고온 신뢰성 문제, SiC 웨이퍼의 대구경화와 품질향상이 이루어 진다면 우수한 물성적 특성을 기반으로 낮은 전력소비 및 고효율의 집적회로 구현이 가능하다. 그러므로 SiC CMOS는 궁극적으로 가장 광범위하게 사용될 수 있는 잠재력을 갖고 있다. 하지만, 전 세계적으로 일부 선진기관에서만 연구가 진행 중이며, Si과 비교했을 때 기술의 성숙도는 아직 초기단계이다. 그러나, 2018년 가트너 자료[46]에 의하면 고온환경 응용분야의 시장은 17년 기준으로 전체 반도체 시장의 20.3%를 점유하고 있고, 약 12.5%의 높은 시장 성장률을 예측하고 있다. 또한 고온 신뢰성을 요구하는 다양한 응용분야에서는 현재의 Si CMOS IC를 SiC CMOS IC로 대체할 수 있는 가능성이 있는 바, 국내에서도 이를 대비한 원천기술확보가 절실히 필요한 시점이다.

약어 정리

ADC

Analog to Digital Converter

AIST

National Institute of Advanced Industrial Science and Technology

CMOS

Complementary Metal Oxide Semiconductor

DAC

Digital to Analog Converter

Dit

Interface Trapped Density

DNL

Differential Nonlinearity

ENOB

Effective Number of Bits

FSM

Finite State Machine

HiTSiC

High Temperature Silicon Carbide Process

INL

Integral Non-Linearity

LIGBT

Lateral Insulated Gate Bipolar Transistor

LSB

Least Significant Bit

MOSFET

Metal Oxide Semiconductor Field Effect Transistor

NAIST

Nara Institute of Science and Technology

NASA

National Aeronautics and Space Administration

POA

Post Oxidation Anneal

RCA

Ripple Carry Adder

RO

Ring Oscillator

SAR

Successive Approximation Register

SBD

Schottky Barrier Diode

SiC

Silicon Carbide

SNDR

Signal to Noise and Distortion Ratio

SOI

Silicon on Insulator

SR

Shift Register

TI

Texas Instruments

J.A. Pellish and L.M. Cohn, “Technology Option for Extreme Environment Electronics,” in Extreme Environment Electronics, Boca Raton, FL, USA: CRC Press, 2013, pp. 49-58.

P.G. Neudeck, “SiC Integrated Circuit Platforms for High Temperature Applications,” in Extreme Environment Electronics, Boca Raton, FL, USA: CRC Press, 2013, pp. 225-232.

M.R. Werner and W.R. Fahrner, “Review on Materials, Microsensors, Systems, and Devices for High-Temperature and Harsh-Environment Applications,” IEEE Trans. Ind. Electron., vol. 48, no. 2, 2001, pp. 249-257.

A. Hassan, Y. Savaria, and M. Sawan, “Electronics and Packaging Intended for Emerging Harsh Environment Applications: A Review,” IEEE Trans. Very Large Scale Integr. (VLSI) Syst., vol. 26, no. 10, Oct. 2018, pp. 1-14

Valle-Mayorga, Javier, et al., “High-Temperature Silicon-on-Insulator Gate Driver for SiC-FET Power Modules,” IEEE Trans. Power Electron., vol. 27, no. 11, 2012, pp. 4417-4424.

T. Kimoto, “Material Science and Device Physics in SiC Technology for High-Voltage Power Devices,” Jpn. J. Appl. Phys., vol. 54, 2015, pp. 0401302:1-0401302:27.

W.C. Lien et al., “4H-SiC N-Channel JFET for Operation in High-Temperature Environments,” IEEE J. Electron Devices Soc., vol. 2, no. 6, 2014, pp. 164-167.

M. Cabello et al., “Advanced Processing for Mobility Improvement in 4H-SiC MOSFETs: A Review,” Materials Sci. Semiconductor Process., vol. 78, 2018, pp. 22-31/

G.Y. Chung et al., “Improved Inversion Channel Mobility for 4H-SiC MOSFETs Following High Temperature Anneals in Nitric Oxide,” IEEE Electr. Device Lett., vol. 22, no. 4, 2001, pp. 176–178.

E.Ö. Sveinbjörnsson et al., “Sodium Enhanced Oxidation of Si-face 4H-SiC a Method to Remove Near Interface Traps,” Mater. Sci. Forum, vol. 556–557, 2007, pp. 487–492.

T. Hatayama et al., “Remarkable Increase in the Channel Mobility of SiC MOSFETs by Controlling the Interfacial SiO2 Layer Between Al2O3 and SiC,” IEEE Trans. Electron Devices, vol. 55, no. 8, 2008, pp. 2041–2045.

D. Okamoto et al., “Improved Inversion Channel Mobility in 4H-SiC MOSFET on Si Face Utilizing Phosphorus-Doped Gate Oxide,” IEEE Electron Devices Lett., vol. 31, no. 7, 2010, pp. 710–712.

Y.K. Sharma et al., “Stable Phosphorus Passivated SiO2/4H-SiC Interface Using Thin Oxides,” Materials Science Forum., vol. 806, 2014, pp. 139-142

A. Modic et al., “High Channel Mobility 4H-SiC MOSFETs by Anitmony Counter-Doping,” IEEE Electron Device Lett., vol. 35, no. 9, 2014, pp. 894–896.

D. Okamoto et al., “Improved Channel Mobility in 4H-SiC MOSFETs by Boron Passivation,” IEEE Electron Device Lett., vol. 35, no. 12, 2014, pp. 1176–1178.

Y.K. Sharma et al., “Stable Phosphorus Passivated SiO2/4H-SiC Interface Using Thin Oxides,” Materials Science Forum., vol. 806, 2014, pp. 139-142

L. Kolaklieva et al., “Au/Ti/Al Contacts to SiC for Power Applications: Electrical, Chemical and Thermal Properties,” In Int. Conf. Microelectron., Nis, Serbia, May 16-19, 2004, pp. 421-424

L.J. Evans et al., “Development of an Extreme High Temperature n-Type Ohmic Contact to Silicon Carbide,” Materials Sci. Forum, vol. 717, 2012, pp. 841-844.

R.S. Okojie et al., “Reliability Assessment of Ti/TaSi2/Pt Ohmic Contacts on SiC after 1000 h at 600℃,” J. Appl. Phys., vol. 91, no. 10, 2002, pp. 6553-6559.

W.C. Lien et al., “4H-SiC N-Channel JFET for Operation in High-Temperature Environments,” IEEE J. Electron Devices Soc., vol. 2, no. 6, 2014, pp. 164-167.

K. Gottfried et al., “High Temperature Stable metallization Schemes for SiC-Technology Operating in Air,” In High-Temperature Electronic Materials, Devices Sensors Conf., San Diego, CA, USA, Feb. 22-27, 1998, pp. 153-158

S. Shakti, and A.C. James, “Bipolar Integrated Circuits in 4H-SiC,” IEEE Trans. Electron Devices, vol. 58, no. 4, 2011, pp. 1084-1090.

Y. Zhang et al., “Thermal Stability Study of n-Type and p-Type Ohmic Contacts Simultaneously Formed on 4H-SiC,” J. Alloys Compounds, vol. 731, 2018, pp. 1267–1274.

N. Masato et al., “Experimental and Theoretical Investigations on Short-Channel Effects in 4H-SiC MOSFETs,” IEEE Trans. Electron Devices, vol. 52, no. 9, 2005, pp. 1954–1962.

M.P. Lam et al., “Punchthrough Behavior in Short Channel NMOS and PMOS 6H-Silicon Carbide Transistors at Elevated Temperatures,” IEEE Trans. Electron Devices, vol. 22, no. 3, 1999, pp. 433–438.

J.A. Valle-Mayorga et al., “A SiC NMOS Linear Voltage Regulator for High-Temperature Applications,” IEEE Trans. Power Electron., vol. 29, no. 5, 2014, pp. 2321-2328.

D.T. Clark et al., “High Temperature Silicon Carbide CMOS Integrated Circuits,” Mater. Sci. Forum, vol. 679–680, 2011, pp. 726–729.

R.A.R. Young et al., “High Temperature Digital and Analogue Integrated Circuits in Silicon Carbide,” Materials Science Forum, vol. 740, 2013, pp. 1065-1068.

C.-M. Zetterling et al., “Future High Temperature Applications for SiC Integrated Circuits,” Phys. Status Solidi C, vol. 9, no. 7, 2012, pp. 1647-1650.

S. Kargarrazi et al., “A monolithic SiC drive circuit for SiC Power BJTs,” Int. Symp. Power Semiconductor Devices IC's, Hong Kong, China, May 10-14, 2015, pp. 285-288.

H. Elahipanah et al., “500℃ High Current 4H-SiC Lateral BJTs for High-Temperature Integrated Circuits,” IEEE Electron Device Lett., vol. 38, no. 10, Oct. 2017, pp. 1429-1432.

C.-M. Zetterling et al., “Bipolar Integrated Circuits in SiC for Extreme Environment Operation,” Semicond. Sci. Technol., vol. 32, 2017, pp. 1-11.

Y. Zhang et al., “Development of 4H-SiC LJFET-Based Power IC,” IEEE Trans. Electron Devices, vol. 55, no. 8, Aug. 2008, pp. 1934-1945.

P.G. Neudeck et al., “Demonstration of 4H-SiC Digital Integrated Circuits Above 800℃,” IEEE Electron Device Lett., vol. 38, no.8, Aug. 2017, pp. 1082-1085.

M. Alexandru et al., “SiC Integrated Circuit Control Electronics for High-Temperature Operation,” IEEE Trans. Ind. Electron., vol. 62, no. 5, May 2015, pp. 3182-3191.

A. Rahman et al., “High Temperature Data Converters in Silicon Carbide CMOS,” IEEE Trans. Electron Devices, vol. 64, no.4, Apr. 2017, pp. 1426-1432.

H.A. Mantooth et al., “Emerging Trends in Silicon Carbide Power Electronics Design,” CPSS Trans. Power Electron. Applicat., vol. 2, no. 3, Sept. 2017, pp. 161-169.

J. Barlow et al., “An Integrated SiC CMOS Gate Driver,” IEEE Appl. Power Electron. Conf. Exposition (APEC), Long Beach, CA, USA, Mar. 20-24, 2016, pp. 1646-1649.

N. Kuhns et al., “Complex High-Temperature CMOS Silicon Carbide Digital Circuit Designs,” IEEE Trans. Device Materials Reliability, vol. 16, no. 2, June 2016, pp. 105-111.

J.I. Won et al., “Design and Fabrication of 4H-SiC Lateral IGBT with Drift Segmentation using Trench Process,” The 25th KCS, Jungsung, Rep. of Korea, 2018, p. 896.

(그림 3)

SiC CMOS 기반 linear voltage regulator

[출처] Reprinted from H.A. Mantooth et al., “Emerging Trends in Silicon Carbide Power Electronics Design,” CPSS Trans. Power Electron. Applicat., vol. 2, no. 3, Sept. 2017, pp. 161-169.

(그림 4)

SiC CMOS 기반 OP amplifier

[출처] Reprinted from 43 Hitachi, Sept. 14, 2017. http://www. hitachi.com/New/cnews/month/2017/09/170914.pdf

(그림 5)

ETRI의 6인치 기반 SiC 전력소자 (a) SBD, (b) MOSFET 제작 웨이퍼 및 SEM단면도

[출처] 한국전자통신연구원, “SiC기반 트렌치형 차세대 전력소자 핵심기술개발 2017 연구보고서,” 2017.

- Sign Up

- 전자통신동향분석 이메일 전자저널 구독을 원하시는 경우 정확한 이메일 주소를 입력하시기 바랍니다.