김용희 (Kim Y.H.) 시냅스소자창의연구센터 선임연구원

백남섭 (Baek N.S.) 시냅스소자창의연구센터 선임연구원

I. 서론

컴퓨터 과학의 출연과 함께 뇌 정보처리를 컴퓨터 과학과 연결하려는 시도는 뉴로컴퓨팅(neuro-computing) 분야의 발전과 더불어 집적회로 기술을 기반으로 하드웨어적으로 뇌의 신경 정보처리와 감각-운동 신경계를 구현하려는 뉴로모픽(neuromorphic) 분야가 1990년 태동되었다. CMOS(Complementary Metal-Oxide-Semiconductor)를 기반으로 뇌를 모방하는 것은 집적도의 한계에 부딪히게 되었는데, 그 가운데 하나는 학습의 기본요소인 시냅스의 모방에 있다. 2008년 기억과 스위칭을 동시에 수행할 수 있는 레지스터 구조의 소자가 해석된 이 후 뉴로모픽 분야는 제2의 성장기를 맞이하게 되었다. 시냅스 모방 소자는 기존 기억소자를 대신할 수 있을 뿐만 아니라 CMOS 트랜지스터와의 하이브리드 또는 그 자체의 조합만으로도 뇌 세포의 기능을 모방할 수 있는 잠재력을 가지고 있다. 본문은 시냅스 모방 소자의 연구개발 동향과 더불어 뇌 모방 집적회로의 연구개발 동향 조사 및 기술적 분석에 관한 것으로, 기술적 문제점 파악과 그 해결책을 구하기 위한 단초를 제공하는 데에 그 목적이 있다.

II. 시냅스 개요

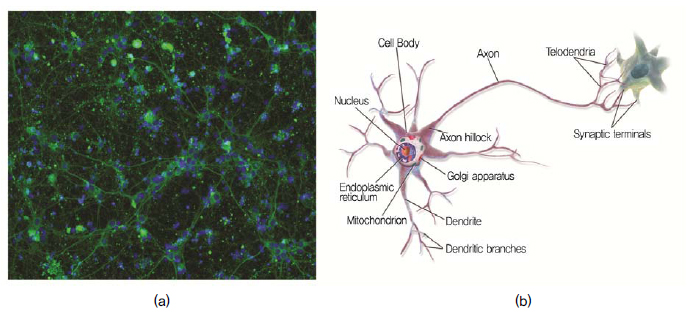

뇌에 있는 신경세포로 알려진 뉴런(neuron)은 신체 감각기관을 통하여 습득된 정보를 인지하고 처리하며 운동기관에 명령을 주는 휴먼 활동에 있어서 치명적인 역할을 한다. 뉴런은 (그림 1의 (b))과 같이 해부학적으로 소마(soma)로 일컫는 세포 체, 수상돌기(dendrite), 그리고 축삭(axon)으로 구성된다. 뉴런들은 축삭과 수상돌기 혹은 축삭과 세포 체 간의 연결을 통해서 (그림 1의 (a))과 같이 네트워크 구조를 형성하는데, 축삭과 수상돌기와의 연결은 시냅스(synapse) 또는 시냅스 단말 구조에 의해 이루어진다. 무게가 1.3-1.4Kg 나가는 성인 뇌에는 약 1011개의 뉴런이 존재하며[1], 하나의 뉴런은 103-104개의 시냅스를 통해서 다른 뉴런들과 연결을 하고 있다. 뇌는 약 20W 수준의 전력[2]으로 생명유지, 기억, 연산, 추론, 상상 그리고 학습 등을 동시에 그리고 실시간으로 수행하는데, 이러한 뇌의 기능을 디지털적으로 모사하기 위해서는 현존 슈퍼컴퓨터 대비 약 1,000배 빠른 속도가 요구된다. 참고로 2013년 11월 기준 슈퍼컴퓨팅 연산속도 세계 3위(16.32Petaflops/s)인 Sequoia는 7.89MW의 전력을 소비한다[3]. 이와 같이 에너지 측면에서 효율적이고 실시간 적인 뇌의 정보처리 능력은 신경망으로 모사되는 뉴런 네트워크를 기반으로 하는 병렬처리와 학습기능으로 표현된다. 특정한 기능을 수행하는 프로세서가 병렬적으로 연결되는 반도체 집적회로 시스템과 다르게 뉴런세포들은 병렬적으로 연결되어 정보처리를 수행한다. 디지털 컴퓨터의 경우 연산과 메모리는 서로 분리되어 있으며, 매 순차 연산 스텝마다 메모리로부터 데이터버스를 통하여 이진 값을 검색 및 저장하는 과정을 거치게 되는데, CPU(Central Processing Unit) 싸이클의 70-80%는 이 과정에 소요된다. 이러한 시간 손실 문제는 ‘0’으로 나누는 것과 같은 비선형 문제 그리고 소자 또는 소프트웨어 오류에 의한 연산 결함 등과 함께 디지털 컴퓨팅 속도를 제한하는 디지털 컴퓨팅의 한계 가운데 하나로 열거된다. 생물학적 신경망은 연산의 정확도나 반복도 측면보다는 잡음이 있고 변화하는 환경에서 적은 에너지 소모로 대용량 고속 연산에 있어서 탁월하다.

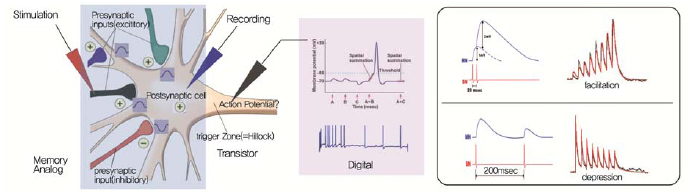

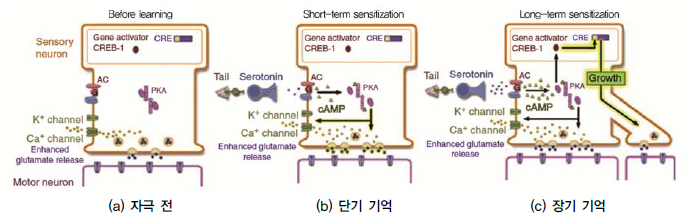

(그림 2)와 같이 다수의 시냅스를 경유하는 서로 다른 극성(흥분성 및 억제성에 해당)을 가지는 미세한 아날로그 전기신호가 세포체내에 집적되고 그 신호들의 합이 특정한 임계 값 보다 커지면 약 1ms의 폭을 가지며 거의 일정한 세기를 가지는 활동전위(action potential) 또는 스파이크로 일컫는 디지털 개념의 펄스신호가 발생된다. 스파이크 세기와 무관하게 단위시간당 펄스 수 등에 의미 있는 정보가 포함되어 있으며, 스파이크 신호의 디코딩은 현재 뇌-제어 기반 사지기능 장애인의 보철 재활에 활발하게 적용되고 있다. 이와 같이 뉴런은 하나의 세포에 아날로그와 디지털 신호처리 기능을 가지고 있을 뿐만 아니라 메모리와 프로세서의 기능을 가지고 있는데, 메모리 저장은 시냅스에서 이루어진다. 전시냅스(presynapse)에 빈번하게 자극을 주면 후시냅스(post-synapse)의 전류가 증가, 즉 전도도가 증가하게 되어 자극에 대해 민감하게 된다. 반면에 자극이 드물게 가해지는 경우 전류가 감소, 즉 전도도가 감소하여 자극에 대한 민감도가 감소하게 된다. 시냅스는 이와 같은 과정을 통해서 자극에 대한 기억을 가지게 된다. 감각 뉴런을 통해 작은 크기의 자극이 빈번하게 가해지면 감각 뉴런과 연결된 운동 뉴런(motor neuron)의 자극에 대한 민감도가 급격하게 증가하는데, 이 과정은 (그림 3)과 같이 감각 뉴런과 운동 뉴런을 연결하는 시냅스 구조 변화를 수반한다. 단기적인 그리고 장기적인 민감도 향상에는 이온채널의 수적 증가와 새로운 시냅스의 형성을 각각 수반한다는 것이 제안되었으며, 전기 생리학적으로, 신경 해부학적으로 그리고 분자생물학적으로 많은 실험적 측정과 관찰 그리고 기작 규명이 이루어졌다[4]. 시냅스의 변화는 현재 기억과 이를 기반으로 하는 학습, 즉 지능에 관한 세포 수준의 기작으로 받아들여지고 있다. 시냅스의 변화는 시냅스 세기 변화, 시냅스 효용 또는 시냅스 가중치의 변화, 그리고 시냅스 가소성으로 표현된다.

III. 멤리스터

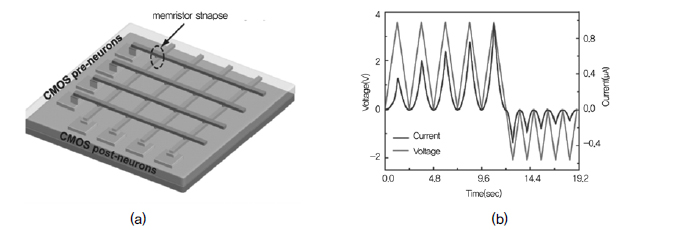

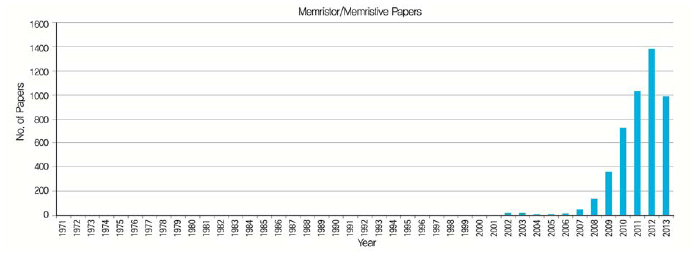

2008년 Strukov 등[5]이 전류-전압 평면에서 핀치 이력 특성을 보이는 금속/절연체/금속 구조에서 저항 값이 일정하지 않고 통과한 전류의 역사에 좌우되는 특성을 멤리스터로 해석하였으며, 주기적인 전압 인가에 의해 정점 전류 값이 증가하는 양상((그림 4) 참조)이 반복 자극에 의해 시냅스 세기가 증가하는 생물학적 시냅스의 거동((그림 2) 참조)과 유사하다는 것을 제시하였다. 멤리스터(memristor)는 메모리(memory)와 레지스터(resistor)의 합성어로 전기 저항이 일정하지 않고 소자를 통과하는 전류 또는 전하량의 시간에 대한 적분 값, 즉 통과한 전류의 역사에 좌우되는 특성을 가지는 수동 2-단자 전기 소자를 나타내며, 메모리와 스위칭 기능을 모두 가지고 있다. 멤리스터는 AC(Alternating Current) 소자로 에너지를 저장하지 않으며, I-V 평면에서 핀치 이력 루프를 보이고, 양 및 음 미분저항, 저주파 특성을 보인다[7]. 멤리스터는 1971년 Chua[8]가 이론적으로 예측한 기본 소자로 비선형 전하(charge)-자기 유동(magnetic flux) 관계를 보인다. 멤리스터 특성에 관한 실험적인 보고는 1960년대부터 종종 있어왔지만 멤리스터로 설명되지 않았다[9]-[11]. Srtukov 등의 발표는 스위칭 및 메모리 특성을 멤리스터로 해석을 시도한 첫 번째 보고이며, 이로 말미암아 관련 분야 연구개발이 급격하게 촉진되었다((그림 5) 참조).

저항 스위칭 현상을 보이는 다양한 소재들이 멤리스터 제작에 적용이 가능한데 주로 금속산화물(MOx), 희토류 금속산화물, 강유전체, 칼코게니드, 금속 주입된 폴리실리콘, 고체전해질, 금속-절연체 전이 특성을 가지는 소재 등이 적용되고 있다[13]. 멤리스터의 구조는 대부분 2-단자 수직 크로스바 구조인데 이 구조는 3차원 적층이 용이한 장점을 가지고 있다. 수평 2-단자 또는 트랜지스터와 같은 3-단자 구조가 제작되기도 하지만 소자의 면적이 증가하기 때문에 불리하며, 연구용으로만 사용된다[14]. 대부분의 멤리스터는 나노크기로 제작되는데 이는 회로 집적도 및 전력 방출 측면에서 장점이 있으며, 기술적으로 10 nm 크기 구현에는 문제가 없다.

멤리스터는 비휘발성 메모리 특성을 가지고 있기 때문에 HP(Hewlett-Packard)는 플래쉬 메모리와 DRAM을 대체할 것으로 기대하고 있다. HP와 하이닉스를 비롯하여 많은 기업들이 ReRAM 양산 프로젝트를 수행하고 있는데, 2013년 8월 파나소닉은 마이크로컴퓨터에 최초로 ReRAM(Resistive Random Access Memory)을 탑재하였다[15]. HP는 2018년 100TB 드라이브의 공급 계획을 발표하였다[16].

2차원 멤리스터는 대부분 필라멘트 형성을 수반하는데, 아직까지 필라멘트가 형성되는 위치와 길이 등을 제어하는 기술은 개발되지 않고 있다. 면적이 작아지면 필라멘트 형성 가능성이 작아지지만 부정합(mismatch) 문제가 커지는 문제가 수반된다. 필라멘트 형성 문제를 해결하기 위한 방안으로 나노선과 같은 1차원 구조를 활용하는 방법이 시도되고 있다. 나노선 멤리스터 제작에는 Si[17], ZnO[18], TiO2[19], CuO[20], CoO[21] 등의 소재가 활용되고 있으며, 가장 최근 Trinity College의 Boland 그룹에서는 나노선과 멤리스터를 결합하는 시도를 하고 있는데, 나노선은 나노선들이 서로 겹쳐지는 부분에서 전기, 광, 화학적인 자극에 의해서 멤리스터 교차점이 형성되는 원리에 기초한다[22]. 멤리스터 기반의 센서, 즉, 멤센서(memsensor)는 감지하는 변수들에 대한 반응에 대한 역사를 지니고 있기 때문에 실제 환경에 노출될 경우 환경 변화에 대한 적응성이 예상된다. 나노선 멤리스터를 항원-항체 반응을 이용한 바이오센싱에 적용한 시도가 최근에 보고되었다[23].

IV. 차세대 뉴로모픽 시스템

임계 게이트 전압 이하에서 전류모드로 동작하는 CMOS 트랜지스터 회로가 뉴런의 핵심 구성 요소인 이온 채널의 S자형 전류-전압 특성과 유사하다는 1989년 Mead[24]의 언급 이후 CMOS 트랜지스터 회로로 뉴런의 점화를 모사하는 뉴로모픽 또는 실리콘 뉴런 분야의 연구가 활발하게 진행되고 있다. 근래 뉴런의 점화(firing)뿐만 아니라 이온 채널과 뉴런 내부 이온의 동특성도 모사되고 있다[25]-[27]. 실리콘 뉴런의 가장 큰 도전과제는 고집적화인데, 이에 대한 장애 요소는 낮은 입력 전압 동특성 범위(<100mV)이다[28]. 공정 등에 의해 기인하는 부정합 오차 최악의 경우 100mV를 초과할 수 있다. 근래 광대역 미분쌍(differential pair) 회로 등의 도입으로 입력 전압 동특성 범위가 1V 이상 증가하였다[26]. 최근, 휴대용 전자기기를 위한 저 전력 구동 SoC(System on Chip) 기술이 발달함에 따라 구동전압이 0.45V까지 감소하고 있기 때문에 입력 전압 동특성 범위는 더 이상 제한 요소가 되지 않을 것으로 예상된다. 또한 3차원 집적회로 공정 기술은 실리콘 뉴런의 크기를 현저하게 줄이는데 기여할 것으로 예상된다.

결정과 무정형 상태로 가역적으로 변환되는 상변환 소재는 Ovshinsky에 의해 거칠게 제안된 ‘cognitive’ 컴퓨팅 구현이 가능한 소재로 간주되어 왔다. 상변환 소재는 0과 1사이에 안정된 여러 개의 에너지 상태가 존재하며 입력 펄스에 따라 에너지 상태가 변화하는 소위 ‘Ovonic 소재’로 멤리스터와 같이 2차원 크로스바 구조 및 3차원 적층이 가능하여 적응성이 있는 거동을 하는 집적회로의 구현이 제안되었지만, 이론적으로 확장되지 못하였다[29].

CMOS 뉴로모픽 시스템에서 CMOS 뉴런의 네트워크 연결도 향상과 메모리 운용의 한계를 극복하기 위하여 CMOS 뉴런과 나노선이 crossbar 네트워크 구조로 배열되고 나노선이 겹쳐지는 부분이 시냅스 기능을 가지는 나노소자와의 하이브리드 구조가 하이브리드 반도체/나노선/분자 (“CMOL”) 집적회로의 한 종류로 2003년 Likharev 등[30]에 의해 제안되었다. 나노선이 겹쳐지는 부분에 멤리스터가 적용되어 시냅스 기능이 구체화된 CrossNets 구조가 제안되었는데[31], CrossNets은 멤리스터와 함께 SyNAPSE(Systems of Neuromorphic Adaptive Plastic Scalable Electronics) 프로젝트[32]의 근간이 되는 하드웨어적 요소로 3D로 확장이 용이한 특징을 가지고 있다. 100nm 피치를 가지는 2차원 멤리스터 어레이는 1010 시냅스/cm2 시냅스 밀도에 해당되며, 뉴런 당 104개의 시냅스를 유지하고 CMOS 뉴런의 피치가 10m로 가정할 때 106뉴런/cm2 밀도의 구현이 가능하다. 멤리스터의 저항값은 성능, 신뢰성, 혼선 및 전체 시스템의 전력소실에 크게 영향을 준다[33]. 특히, 발열 측면에서 1V 구동과 106뉴런/cm2을 가정할 때 적어도 100MΩ 수준이 요구되는데, 현재는 kΩ 정도로 집적회로 적용 시 소자들이 용융이 될 수준이다. 멤리스터의 경우도 실리콘 뉴런과 마찬가지로 부정합 오차에 의한 영향을 받지만 멤리스터의 학습 기능에 의해 부정합에 적응할 수 있을 가능성이 있기 때문에 그 영향은 덜할 것으로 분석된다.

2013년 6월 파나소닉은 CMOS 디지털 회로에 강유전체 멤리스터를 제작하여 이미지를 아날로그 방식으로 처리할 수 있는 영상 시스템의 개발을 발표하였는데, 소비 전력이 기존 디지털 시스템에 비해 1/10 정도이며, 강유전체 성장기술과 디지털-아날로그 혼성 신호처리기술이 핵심이다[34]. 미시간 대학의 Lu 그룹은 현존하는 영상처리 시스템에 비해 1,000배 빠르고 10,000배 적은 전력을 소비하는 멤리스터 기반 신경 영상 프로세서를 DARPA(Defense Advanced Research Projects Agency)의 지원으로 개발 중에 있다[35].

뉴리스터는 뉴런의 거동이 모델화되어 전기 신호를 처리할 수 있는 전자 부품으로 정의되는데[36], 즉 Hodgkin-Huxley 축삭과 유사한 특성을 가지는 선 형태의 전자소자로 1960년에 제안되고 개발이 되었었는데, 이러한 형태의 소자는 규모확장에 적합하지 않았다. 2012년 12월 Pickett 등[37]은 Mott 절연체인 Nb2O5로 제작된 두 개의 Mott 멤리스터로 구성된 회로를 제작하여 활동 전위를 발화하는 뉴런 모방 뉴리스터 특성을 보임을 실험적으로 증명하였다. 충분한 전류가 흐를 때 발생되는 열에 의해 전기전도성 채널이 형성되어 금속-절연체 전환 특성을 가지는 Mott 절연체로 제작된 Mott 멤리스터는 뉴런의 활동전위 발생을 이해하는 데에 있어서 강력한 Hodgkin-Huxley 모델의 핵심 요소인 이온채널의 역할을 한다. Mott 멤리스터는 통상적인 멤리스터와 동일한 교차구조를 가지고 있기 때문에 규모를 확대하는 것이 용이하고 기존 실리콘 뉴런과 이종 결합이 가능하며, 특히 모두 멤리스터로 스파이크 기반의 뉴런 모방 집적회로의 구현이 가능하다. 발열 관점에서 한층 더 낮은 온도에서 금속-절연체 전이 특성을 보이는 소재의 개발과 이의 Mott 멤리스터 적용이 문제점으로 남아 있지만 적응하는 집적회로 구현을 앞당기는 강력한 접근 방법이라고 판단된다. Hodgkin과 Huxley는 그들의 모델에서는 표현되지 않았지만 활동 전위가 이온채널의 역사-의존적인 전기전도도를 가질 것임을 실험적으로 보였다[38][39]. Chua[40]는 이온 채널의 전기전도도가 시간과 전압에 좌우된다는 생물학적 실험결과를 기반으로 이온채널이 엄밀하게 저항성이 아니고 멤리스터적인 동작을 한다는 것을 규명하였으며, 이를 기반으로 수정된 멤리스터 Hodgkin-Huxley 모델을 제시하였다. Mott 멤리스터로 구현된 뉴리스터는 이러한 Chua의 제안을 실제적으로 구현한 것으로 의미가 있으며, 조만간 CMOS 회로와 집적되어 스파이크-디지털 혼합 연산 및 논리의 구성이 가능할 것으로 예상되고 있다[41].

V. 결론

멤리스터는 기억과 스위칭 기능을 가지고 있어서 시냅스와 이온채널의 모방에 적합하여 멤리스터 만으로도 뉴런세포를 모방하는 것이 가능한 장점을 가지고 있다. 나노스케일의 멤리스터는 인공적으로 시냅스 거동을 현상학적으로 모사하지만 생물학적인 완성도와 강건함에 있어서 여전히 부족하다. 또한 아직까지 뇌의 학습과 기억 운영에 관한 이해가 부족하여 완벽한 멤리스터가 제작이 되더라도 이의 훈련 등의 많은 숙제가 남아있다. 휴머노이드 로봇과 같은 물리적인 신체와 인터페이스를 이루러 실시간적으로 환경과 상호작용하는 신경모방 집적회로 기반 인지 시스템을 구현하기 위해서는 3D VLSI, 나노규모 공정 기술 및 소재, 새로운 로봇 액튜에이터와 액티브 센서, 스파이크 기반의 학습 기작과 대뇌 피질 발생, 고차 인지 아키텍처 등 신경과학 등과의 융합연구가 필수적이다.

약어 정리

AC alternating current

CMOS complementary metal-oxidesemiconductor

CPU central processing unit

DARPA defense advanced research projects agency

HP Hewlett-Packard

ReRAM resistive random access memory

SyNAPSE systems of Neuromorphic adaptive plastic scalable electronics

VLSI very large scale integration