비동기 회로기술 동향분석

Trends of Asynchronous Circuit Design Technology

- 저자

- 신지호, 브룩크, 오명훈, 김학영 / 서버플랫폼연구실 / UST 컴퓨터소프트웨어 전공

- 권호

- 30권 6호 (통권 156)

- 논문구분

- 일반 논문

- 페이지

- 90-98

- 발행일자

- 2015.12.01

- DOI

- 10.22648/ETRI.2015.J.300610

- 초록

- 본 논문에서는 비동기식 회로기술의 최근 동향을 분석하기 위해 관련 분야의 가장 저명한 학회인 비동기식 회로 및 시스템 학회(International Symposium on Asynchronous Circuits and Systems: ASYNC)에 투고된 논문과 기존의 동향분석 자료를 비교 분석하여 제시하고, 관련 업체의 상용화 사례를 통한 비동기식 회로 기술전망을 제시한다. 조사된 논문은 2011년부터 2015년까지 투고된 총 90편의 논문을 각 기준에 따라 분류하고, 연도별, 국가별, 기관별 동향을 분석함으로 최근 관련 기술의 연구동향을 통계화하여 제시하였다. 분석 결과, 지난 최근 3년 내 Low Power 분야가 주목할 만한 성장세를 보였고, 상용화 사례로는 Intel의 비동기식 설계를 통한 네트워크 칩, IBM의 Brain inspired processor인 TrueNorth 프로세서 등이 주목할 만하다.

Share

Ⅰ. 서론

1. 비동기 회로기술의 필요성

현대 사회는 스마트폰부터 스마트 TV, 사물인터넷 등과 같은 스마트 기기들로 대변되는 사회이다. 나아가 사용자들은 여러 휴대용 기기들이 더욱더 다양한 서비스를 지원할 것을 기대하고, 이런 기대에 부응하기 위해 기기들은 각기 다른 시스템과 여러 기술을 통해 사용자의 요구를 충족하려 한다. 하지만 이러한 기능 구현을 위해 기기는 점점 더 복잡해져 가고, 소비전력 또한 많아지고 있다.

고성능, 저전력 시스템을 요구하는 현시대는 개발자들로 하여금 새로운 기술개발의 필요성을 끊임없이 요구하였고, 이는 기존의 기기들이 사용하는 동기식 회로(Synch-ronous Circuit)의 한계점을 다시금 생각하도록 하였다.

기존 동기식 회로의 경우 하나의 전역클록(Global Clock)을 사용함으로 인하여 불필요한 전력소비 문제, 클럭 스큐와 같은 동기화 신호문제, 타 기기들의 각기 다른 클록 사용으로 인한 타임 도메인 문제와 같이 여러 문제가 존재하였고, 이러한 문제들은 연구자들로 하여금 기존의 동기식 회로설계에서 비동기식 회로(Asynchronous Circuit)설계로 디지털 회로설계의 패러다임 전환이 요구되고 있다[1].

비동기식 회로의 경우 기존 동기식 회로가 일반적으로 사용하던 전역클록이 아닌 핸드쉐이크 프로토콜(Handshake Protocol)을 사용함으로 전역클록을 전체 시스템에서 제거하는 것을 기본으로 고성능 시스템 구현, 높은 전력 효율을 기반으로 한 저전력 시스템 구현이 용이하다는 장점과 기존 동기회로와는 달리 주변 환경 변화에 대한 강한 내구성 등을 장점으로 갖고 있다.

이러한 장점이 있는 비동기식 회로설계에 있어 국제 비동기식 회로 및 시스템 학회(International Symposium on Asynchronous Circuits and Systems: ASYNC) [2]-[6]의 경우 매년 개최되는 관련 분야 가장 저명한 학회로 최신 비동기 회로설계 기술에 대한 소개 및 여러 설계 방법론들에 대한 소개가 꾸준히 이루어지고 있다.

본 논문에서는 2011년부터 2015년까지 ASYNC학회에 투고된 20개국, 69개의 기관이 투고한 90편의 논문을 분석, 정리하여 비동기식 회로설계 최신동향에 대한 통계를 제시하고, 비동기식 회로설계 관련 회사와 툴, 상용화 사례를 조사함으로 산업체 적용현황과 향후 비동기식 회로기술 전망을 알아보고자 한다.

Ⅱ. 비동기 회로기술 연구동향분석

1. 연구주제별 분석

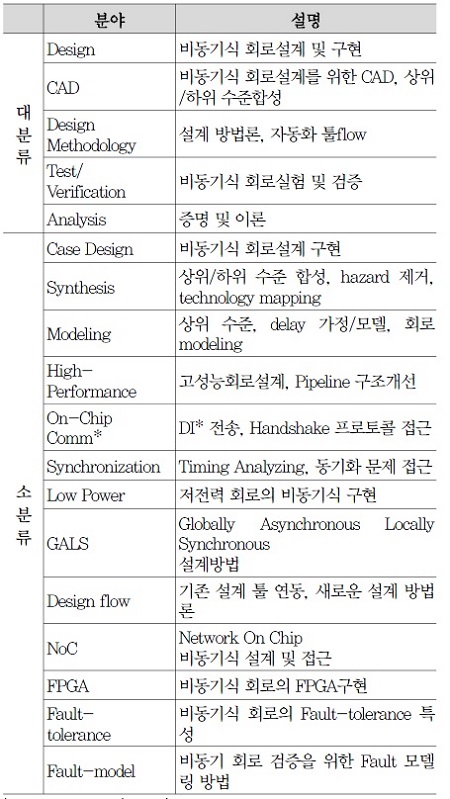

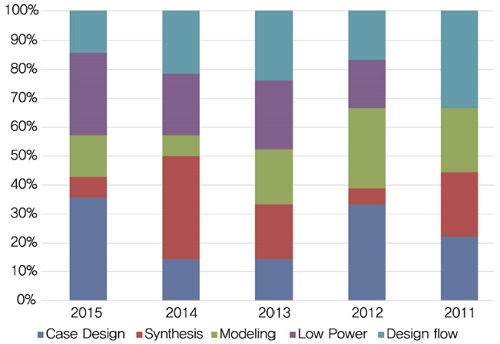

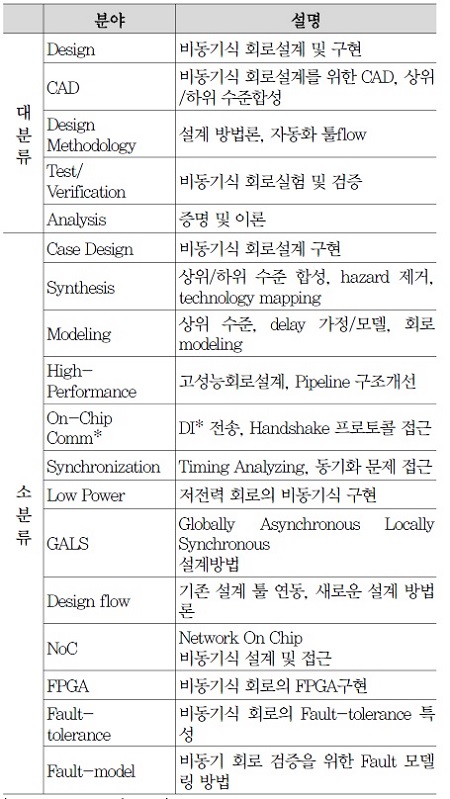

ASYNC학회에서 매년 다루는 논문의 주제를 대분류와 소분류로 분류하여 해마다 어떠한 주제가 다뤄지고, 이슈가 되고 있는 기술에 대해 알아보았다. 분류에 사용된 기준은 대분류 4가지와 소분류 13가지로 나누었으며 분류 기준은 기존 동향분석 논문의 분류를 이용하여 비교분석이 용이하도록 하였다[7]. 하나의 논문이 여러 내용을 담을 수 있기에 분류에 있어 필요의 경우 중복을 허용하여 분류하였다.

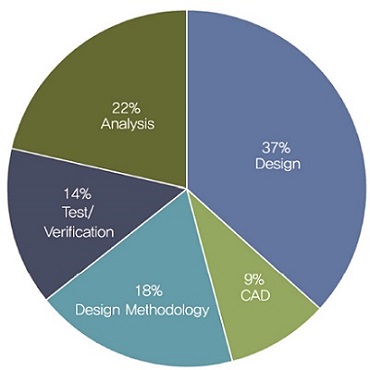

대분류는 Design, Computer Aided Design(CAD), Design Methodology, Test/Verification, Analysis로 나누어 전반적인 VLSI 시스템 관련 기술을 분류하는 데 어려움이 없도록 하였고, 소분류의 경우 동기 회로와 차별된 비동기 회로설계 특성들을 반영한 13가지 항목으로 나누어 분류하였다. <표 1>은 각각의 분류 기준을 설명한다.

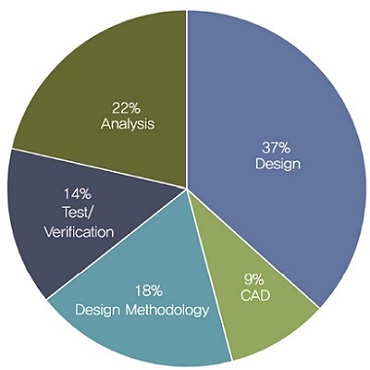

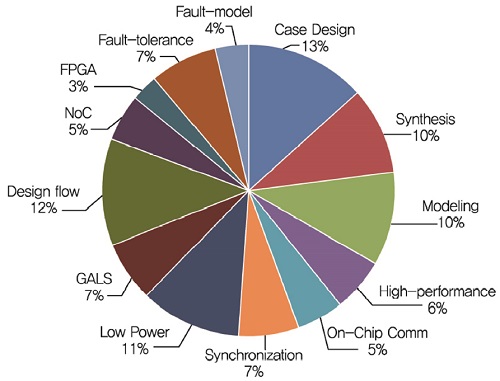

(그림 1, 2)는 각 논문의 대분류 및 소분류별 분포도를 도식화하여 나타냈다.

분류 기준의 중복성을 고려, 90건의 투고논문을 대분류 기준에 의하여 분류하면 총 98건으로 그중 36건의 논문이 비동기식 회로설계 및 구현을 다룬 Design 분야로 전체 37%를 차지하며 전체 투고논문의 주를 이루었다. 뒤를 이어 새로운 이론이나 증명방법에 대한 Analysis가 21건, 회로설계 방법론과 자동화 툴 flow에 대한 Design Methodology가 18건을 보이며 다소 높은 분포도를 보였다.

반면 회로설계 자동화를 위한 CAD알고리즘 관련 주제와 회로 실험과 검증에 관련된 논문은 상대적으로 낮은 분포를 보였는데, 이 결과는 현재까지 비동기 회로설계에 있어 상용화된 CAD툴 적용의 어려움과 비동기 회로설계에 최적화된 CAD알고리즘 개발의 어려움, 동기회로에 특화된 회로 검증방법의 비동기적 해석에 대한 어려움이 통계결과에 직접적으로 나타난 것이라 생각된다.

투고된 논문을 소분류 기준으로 보았을 때 133건의 논문이 투고되었다. 투고 분야별로는 비동기식으로 설계된 작은 규모의 회로부터 큰 규모의 회로까지 다룬 Case Design이 전체 투고논문의 13%를 차지하며 가장 높은 비중을 보였고, 기존 상용화 툴 연동방법론과 새로운 설계 방법론에 대하여 다룬 Design flow가 12%로 뒤를 이었다.

주목할 만한 논문의 주제로는 저전력 회로의 비동기식 구현을 다룬 Low Power에 대한 논문이 전체 11%를 보이며 상당히 높은 비중을 차지하였는데 이는 기존 비동기식 회로설계 연구동향이 저전력 설계보다 고성능에 집중했던 반면, 현시대의 패러다임이 저전력 시스템을 요구하고 비동기식 회로설계방법이 하나의 해법이 될 수 있음을 보이는 결과라고 생각된다.

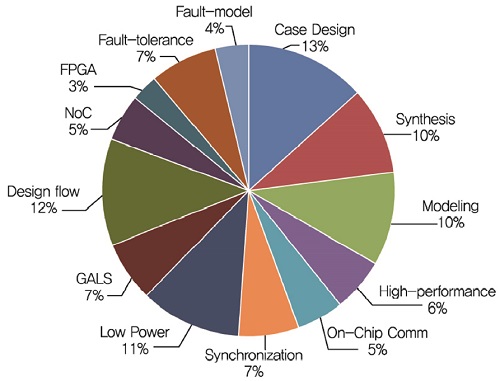

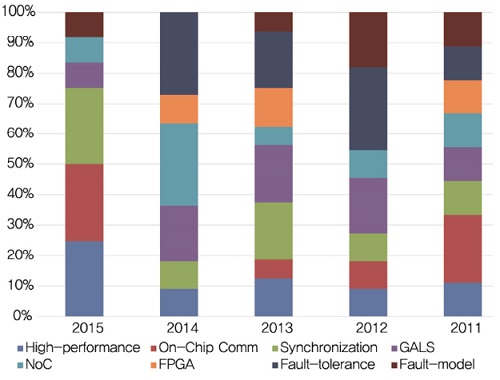

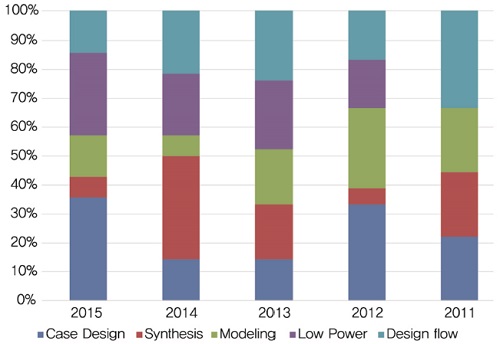

또한, Modeling과 Synthesis를 다룬 논문은 각각 10%를 차지하며 지난 동향분석과 비교하였을 때 꾸준한 연구가 진행되고 있음을 알 수 있다. 다음 (그림 3)은 연도별 상위 5개 소분류 분야별 투고논문 비율을 그래프로 표현하였다. 도표에서도 알 수 있듯 저전력 시스템 구현에 대한 이슈는 2012년부터 투고되기 시작하여 꾸준히 성장하고 있는 분야로 보인다.

반면, 다른 4개의 분야는 투고율이 성장과 하락을 반복하며 꾸준한 연구는 지속되고 있지만, 저전력 회로설계와 같이 눈에 띄게 성장하고 있는 분야는 없었다.

설계 방법론과 기존 설계 툴과의 연동에 대한 Design flow에 대한 연구와 상위 수준 언어, 회로의 모델링, formal method modeling을 다루는 Modeling 분야들은 새로운 툴 개발보다는 기존 툴과의 연동에 조금 더 집중되고 있었으나, 기존 툴과의 연동을 위한 새로운 설계구성과 방법, 비동기식 회로설계 방식의 메모리 분야, 전력분야 적용 등에 대한 논의는 꾸준히 이루어지고 있어, 관심을 가지고 지켜보아야 할 분야로 생각된다.

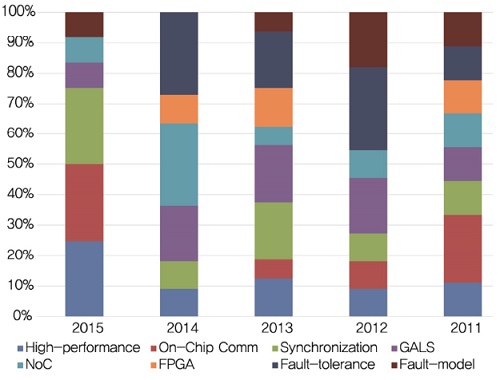

(그림 4)의 경우 상위 5개 분야를 제외한 나머지 8개 분야의 연도별 투고비율을 정리하여 표시하였다.

1994년부터 2010년까지의 기존 동향과 비교하였을 때 흥미로운 사실은 비교적 관련 연구활동이 미비하던 Fault-tolerance 분야의 성장이라 할 수 있다. 이는 기존의 동기식 회로의 단점이었던 주변환경(Process, Voltage and Temperature: PVT)변화에 의존성이 비동기식 회로설계를 통해 극복될 수 있다는 점으로 해석되며, 이러한 PVT Variation 안정성은 비교적 환경변화의 폭이 심한 웨어러블 디바이스, 사물인터넷(Internet of the Things: IoT)디바이스 등에 비동기식 회로설계 방식을 적용하여 고신뢰성 프로세서, 혹은 고신뢰성 플랫폼을 제공할 수 있을 것으로 생각된다.

Network on Chip(NoC)의 경우 2000년대 중반부터 꾸준히 성장해 오던 연구분야로 패킷 전송방식에 비동기식 회로의 핸드쉐이크 프로코톨을 적용하여 고속, 고성능 칩 설계를 구현해 왔다. 특히, 2014년 Intel에서 이 기술을 바탕으로 비동기식 고성능 이더넷(Ethernet)스위치-라우터 관련 논문을 발표, 설계된 칩을 상용화하였고, 비동기식 회로설계를 통한 기존 기술의 한계극복이 가능하다는 것을 보여주는 좋은 사례가 되고 있다.

기타 Globally Asynchronous Locally Synchronous (GALS)와 GALS연관 기술이라 할 수 있는 Synchronization, On-Chip Comm 분야의 경우, 기존의 동기식 회로와의 호환, 비동기식 회로의 장점과 동기식 회로의 장점을 상호보완 관계로 적용하려는 움직임이 꾸준히 지속되고 있고, High-performance역시 매년 관련 논문이 투고되며 고성능 시스템에 비동기식 회로설계를 적용하는 연구 역시 지속되고 있음을 알 수 있다.

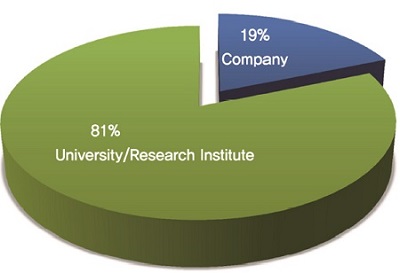

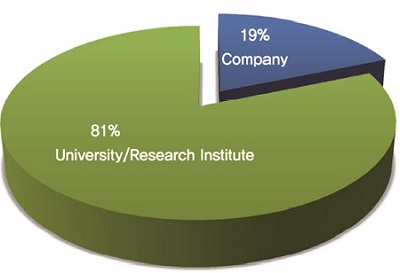

2. 기관 및 국가별 연구주제 분석

논문 투고기관 역시 앞서 분류했던 방식과 같이 2, 3 저자가 포함된 기관을 중복하여 분류하여 전체 90편의 논문보다 많은 수인 137편의 논문으로 분류되었다. 2011년부터 2015년까지 ASYNC학회에 논문을 투고한 기관은 대학을 포함한 연구기관이 56곳으로 전체의 81%, 일반 기업의 연구소 및 기업이 13곳으로 19%로 총 69기관에서 다양한 논문이 투고 되었다[(그림 5) 참조]. 통계에서도 알 수 있듯 비동기식 회로설계 방식은 현재까지는 기업체보다 대학이나 연구기관에서 조금 더 활발하게 연구를 진행하는 분야임을 알 수 있다.

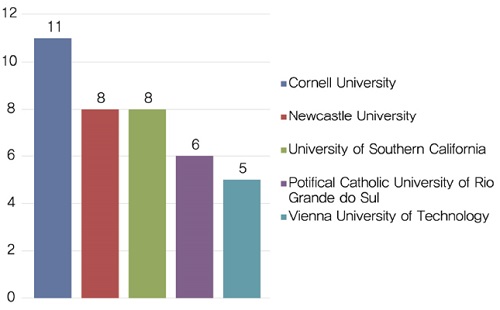

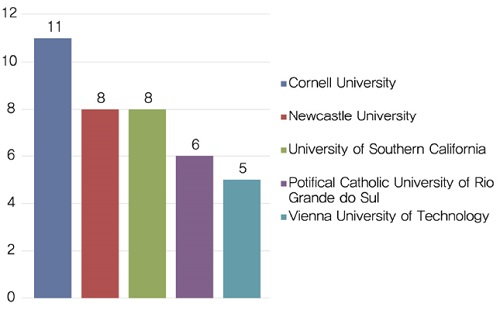

(그림 6)은 상위 5기관을 도식화하여 표시하였다. Cornell University의 경우 전체 137편의 논문 중 11편을 투고하여 가장 높은 투고율을 보였고 Newcastle University와 University of Southern California가 각 8편씩 투고하며 뒤를 이었다. 브라질의 Potifical Catholic University of Rio Grande do Sul의 경우 최근 2년 사이에 3편과 2편을 투고하며 활발한 연구를 진행하고 있으며, 오스트리아 Vienna University of Technology는 2014년 한해 4편을 투고하였다.

흥미로운 점은 지난 1994년부터 2010년까지 활발하던 기관들의 연구는 주춤해지고 새로운 기관들로부터 활발한 연구가 시작되었다는 점이다.

지난 10여 년간 가장 활발하게 연구를 진행하였던 University of Manchester의 경우 본 논문이 조사를 진행한 2011년부터 2015년간 3편의 논문만 투고하였고, 활발한 연구활동을 보이던 기업체인 Philips의 경우는 지난 5년간 한 건의 논문도 투고하지 않았다.

반면, 상위 투고기관이었던 Cornell University와 Newcastle University, University of Southern Cali-fornia의 경우 여전히 높은 투고 비중을 보이며 최근까지도 활발하게 비동기식 회로설계에 대하여 연구를 진행하고 있음을 확인할 수 있다.

상위 5개 기관의 경우 최근 이슈가 되고 있는 저전력 관련 연구 역시 비교적 높은 투고 비율을 보이며 연구가 진행되고 있음을 알 수 있었다.

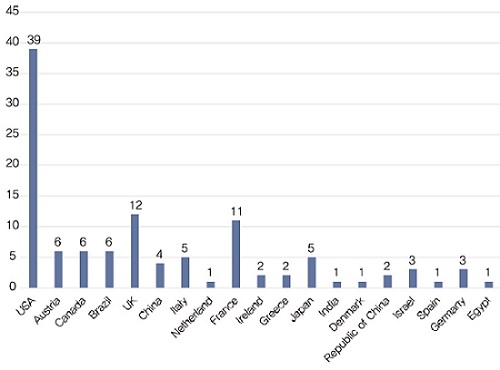

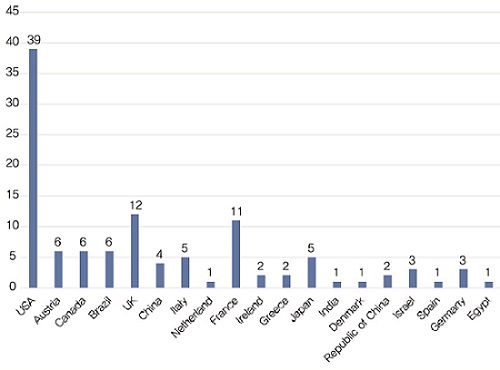

논문 투고 국가의 경우 총 20개국, 114편의 논문이 투고되었다(2, 3저자의 국가가 다른 경우 중복을 허용하여 분류하였다). 상위 투고 국가로는 미국이 39편의 논문을 투고하며 전체 투고논문의 34%를 차지하였고, 영국과 프랑스가 각 12편, 11편으로 뒤를 이었다.

(그림 7)은 국가별 논문 투고율을 도식화하여 나타내었다. (그림 8)은 상위 5개 투고 국가의 연도별 투고논문을 표시하였다. 상위 5개국의 투고논문 수는 총 80편으로 전체 114편 중 70%를 웃도는 높은 비중으로 지난 5년간 ASYNC학회의 주류를 이루었다고 할 수 있다.

주목할 만한 부분은 과거 활발한 연구활동을 보였던 영국의 관련 학회 활동이 감소하였다는 사실과 과거 연구활동이 미비하던 오스트리아, 브라질이 투고율 상위 5개국에 포함이 되었다는 점이다.

이러한 연구활동의 변화는 관련 동향에 영향을 미칠 수 있는 부분으로 꾸준히 지켜볼 필요가 있을 것으로 생각된다.

Ⅲ. 비동기 회로기술 상용화 사례

비동기 회로기술은 기술적으로 기존의 동기식 회로가 해결하지 못하는 많은 문제를 해결할 수 있는 대안임에는 분명하다. 하지만 비동기식 회로설계와 관련된 부족한 툴로 인한 설계의 어려움은 연구자들과 일반 산업체의 접근을 어렵게 하고 있다. 본 장에서는 비동기식 회로설계 기술을 활용한 상용 기술 사례와 상용화 툴에 대해 기존의 동향분석과 비교하여 보고 관련 기술의 전망을 알아보고자 한다[8].

지난 2005년, Handshake Solutions사의 저전력, 낮은 자기장 방출 특성의 비동기식 8bit 마이크로프로세서인 HT80C51과 32bit ARM996HS의 상용화를 시작으로 같은 해 Handshake Solutions사는 상위수준 비동기식 회로설계 툴인 CAD TiDE를 출시하였다.

2008년, Tiempo사의 상용 16bit 비동기식 프로세서 TAM16이 출시되었고, 이듬해 Silistix사에서 상용 동기/비동기 혼합방식 NoC 인터페이스 설계 툴인 CHAIN works를 출시하였다. 이 외, Elastix사는 동기 회로를 비동기식으로 합성해주는 CAD 툴을 상용화하였다.

또한, 전 세계 E-passport 내에 집적된 임베디드 core 시장의 80% 이상이 비동기식 기술을 체택하여 비동기식 회로설계의 특성이 보안 솔루션으로의 적용 가능하다는 것을 알려주고 있다.

하지만 현재 기존 활발한 활동을 진행하였던 많은 업체가 대기업에 인수 혹은 합병되거나 새로운 업체로 재도약 하는 경우들로 인하여 다수의 업체가 사라졌음을 확인하였다.

Sun Microsystems의 경우 Oracle에 인수되어 기존의 활발하던 비동기식 회로설계 관련 연구가 주춤해진 경향을 보였고, Philips 역시 최근 5년간 ASYNC 학회에서의 활동이 없었다.

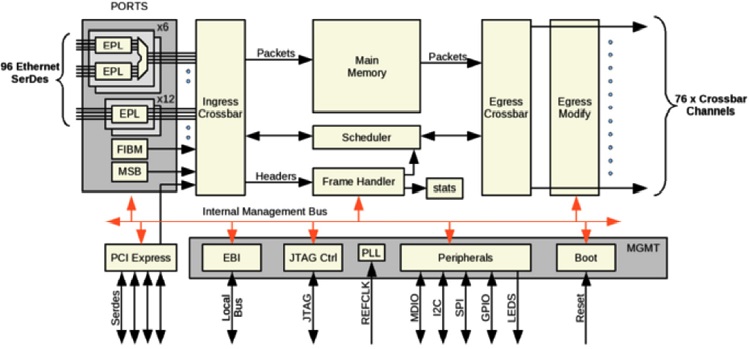

반면, 꾸준히 연구를 진행하며 논문 투고율이 상위권인 Intel의 경우, NoC관련 연구를 활발히 진행하던 Fulcrum Microsystems를 2011년 인수하며[9] 2014년 비동기 회로설계 방식으로 개발된 네트워크 스위치-라우터인 Alta Chip을 개발 FM6000시리즈로 상용화하여 고성능 이더넷 스위치-라우터 시장에서 두각을 나타내고 있다. (그림 9)는 Intel의 네트워크 칩의 구조로 비동기식 회로설계 방식이 데이터 전송과 동기식 이더넷 포트(Ethernet Port Logic: EPL) 인터페이스 간에 적용되었다. 또한, Packet Pipeline에 비동기 회로 구조인 Quasi-Delay-Insensitive(QDI)를 적용, 설계함으로 전체 시스템의 90% 이상 비동기식 회로로 설계, 고성능 시스템을 구현하였다.

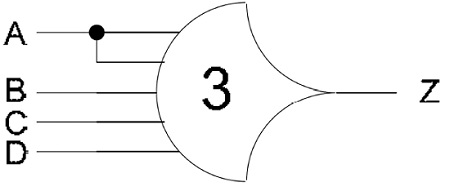

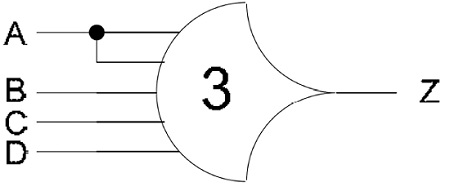

Null Convention Logic(NCL)을 개발하였던 Theseus Research Incorporate(TRI)의 경우 회사가 사라지지는 않았지만, 설립자인 Karl Fant가 Wave Semiconductor[11]라는 새로운 회사를 시작하며 비동기식 회로설계의 아이디어를 지닌 저전력 로직 회로, ASIC (Codename: Azure)과 같은 영역으로 사업을 확장하고 있다. (그림 10)은 기본적인 NCL gate의 형태로 출력값 Z는 AB+AC+AD+BCD로 표현되며 출력의 특성상 NCL gate를 Threshold gate라 한다.

최근 NCL을 이용한 회로설계가 주목받는 이유로, NCL 자체가 기본적으로 DI 특성을 보이고 있어 NCL을 이용함으로 손쉽게 DI특성의 회로설계가 가능하다는 장점이 있기 때문으로 생각된다.

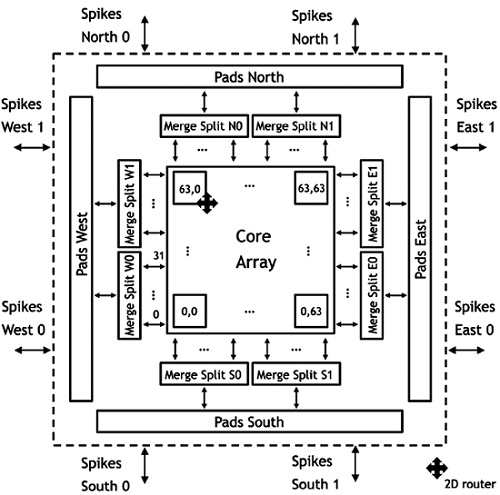

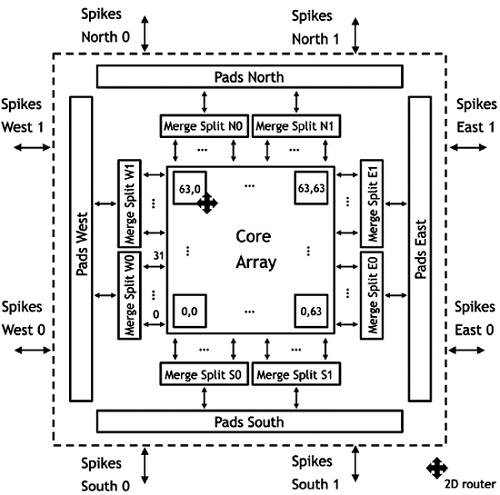

또한, IBM은 최근 생체과학인 뇌를 모방한 인공 신경망 프로세서(Brain inspired chip: TrueNorth)[13]를 개발하였다. (그림 11)은 TrueNorth의 구조로 Spike로 표시된 통신방식이 기존 비동기식 회로설계에서 쓰이던 핸드쉐이크 프로토콜을 모방한 통신방식으로써, 인공신경망 컴퓨터의 기본적인 개념인 Event driven processor의 설계를 가능하도록 하였다.

이는 차세대 기술인 신경망 컴퓨터에 비동기식 회로설계가 필요하며, 비동기 회로에서 사용하는 핸드쉐이크 프로토콜이 차세대 컴퓨팅의 대안이 될 수 있음을 시사하고 있다.

이 외에도 프랑스의 보안 업체인 Tiempo Secure의 경우 비동기식 회로의 특성인 비주기적인 신호처리가 암호화된 정보의 암호 해독이 어렵다는 특징과 PVT변화에 대한 안정성, 높은 신뢰성을 이용, 다양한 보안 관련 회로와 솔루션을 설계, 개발하여 신용카드, 전자여권 등의 보안솔루션으로 적용 상용화하고 있다. 나아가 Tiempo의 경우 자체적으로 개발한 비동기식 회로설계 CAD툴을 개발 상용화하여 기존 동기식 회로설계 CAD를 이용한 비동기식 회로설계의 어려움을 해소하였고, 고속 FPGA와 비동기식 회로설계를 위한 CAD툴 ACE의 개발업체인 Achronix[15], 고성능, 저전력 멀티코어 DSP를 비동기식 회로설계 방식으로 설계하여 상용화 중인 Octasic[16] 등 다수의 업체가 비동기식 회로설계 방식을 통해 사업영역을 확대해 가고 있음을 확인할 수 있었다.

Ⅳ. 결론

2011년부터 2015년까지 ASYNC학회에 투고된 논문들을 중심으로 비동기식 회로설계 기술동향에 대하여 조사하여 기존의 동향분석 자료와 비교하였다.

1994년부터 2010년까지의 동향과 유사하게 지난 5년간 Case design, Synthesis 등의 분야가 높은 투고율을 보였다. 또한, 기존 툴과의 연동에 대한 고민과 새로운 설계 방법론을 다룬 Design flow 분야 연구가 전체 12%를 차지하며 현재까지도 부족한 비동기식 회로설계를 위한 특화된 설계 방법론, 설계 툴에 대한 연구가 꾸준히 진행되고 있었다.

주목할 만한 연구분야로는 저전력 시스템의 비동기식 회로설계 방식 적용을 다룬 Low Power 분야로 2012년부터 연구가 활발해지기 시작하여 현재까지 성장하고 있는 연구분야로 연구자들의 주목을 받고 있으며, 비동기식 회로설계의 장점인 Fault-tolerance, Fault-model 특성과 융합한 회로설계 역시 꾸준한 연구가 진행되고 있음을 확인할 수 있었다.

지난 5년간 투고된 90편의 논문, 69개의 기관의 참여 중 기업체 비중이 19%로 낮은 연구 참여율을 보였고, 상위 5개국의 전체 논문 비중이 70%를 웃도는 높은 비중으로 연구그룹이 특정 기관과 국가에 치우쳐져 있음을 확인할 수 있었다.

관련 분야의 주목 할만한 사례로, 최근 Intel의 비동기 방식 네트워크 칩의 상용화, IBM의 TrueNorth칩 개발과 같이 세계 유수 업체의 비동기식 회로 기법으로 설계된 칩의 상용화와 비동기식 회로설계 기법을 이용한 새로운 설계 패러다임 전환 시도가 좋은 성과를 보였다.

또한, Achronix(ACE), Tiempo-Secure, Octasic와 같은 기업의 비동기식 회로설계에 특화된 개발툴과 상용IP(Intellectual Property), 칩의 개발은 앞으로 비동기식 회로설계 방식이 성장할 수 있는 좋은 성공사례이다.

약어 정리

ASYNC

International Symposium on Asynchronous Circuits and Systems

CAD

Computer Aided Design

Comm

Communication

DI

Delay Insensitive

EPL

Ethernet Port Logic

GALS

Globally Asynchronous Locally Synchronous

IoT

Internet of the Things

IP

Intellectual Property

NCL

Null Convention Logic

NoC

Network on Chip

PVT

Process, Voltage and Temperature

QDI

Quasi-Delay Insensitive

TRI

Theseus Research Incorporate

A. Davis and S.M. Nowick, “An Introduction to Asynchronous Circuit Design,” UUCS, 1997, pp. 2-10.

IEEE Computer Society, “roceedings of 17th IEEE International Symposium on Asynchronous Circuits and Systems,” ASYNC, New York, Apr. 2011.

IEEE Computer Society, “roceedings of 18th IEEE International Symposium on Asynchronous Circuits and Systems,” ASYNC,Copenhagen, May, 2012.

IEEE Computer Society, “roceedings of 19th IEEE International Symposium on Asynchronous Circuits and Systems,” ASYNC,Copenhagen, May, 2013.

IEEE Computer Society, “roceedings of 20th IEEE International Symposium on Asynchronous Circuits and Systems,” ASYNC,Potsdam, May, 2013.

IEEE Computer Society, “Proceedings of 21st IEEE International Symposium on Asynchronous Circuits and Systems,” ASYNC,Mountain View, California, May, 2013.

김성남 외, “비동기식 연구개발 동향 및 전망 - ETRI 연구개발 내용을 중심으로,” 대한전자공학회 하계종합학술대회, 제34권, 1호, 2011. 6, pp. 1626-1629.

Intel, “Intel to Acquire Fulcurm Microsystems,” 2011, http://newsroom.intel.com/community/intel_newsroom/blog/2011/07/19/intel-to-acquire-fulcrum-microsystems

Intel, “Intel Ethernet Switch FM5000/FM6000 Data-sheet,” Intel Networking Division(ND), 2014, pp. 13-20.

North Dakota State University, “Overview of NULL Convention Logic(NCL),” https://www.ndsu.edu/pubweb/~scotsmit/NCL_intro.pdf

IBM Research, “Introducing a Brain-Inspired Computer,” http://www.research.ibm.com/articles/brain-chip.shtml

F. Akopyan et al., “TrueNorth: Design and Tool Flow of 65mW 1Million Neuron Programmable Neurosynaptic Chip,”IEEE Transaction on Computer-Aided Design of Integrated Circuits and Systems, vol. 34, no. 10, 2015, pp. 1537-1557.

- Sign Up

- 전자통신동향분석 이메일 전자저널 구독을 원하시는 경우 정확한 이메일 주소를 입력하시기 바랍니다.