실리콘 포토닉스 테크놀로지-미래컴퓨팅, 데이터 통신을 위한 광I/O 플랫폼

Silicon Photonics Technology—The optical I/O platform for future computing and data communication

- 저자

- 김경옥 / 나노인터페이스소자연구실

- 권호

- 31권 6호 (통권 162)

- 논문구분

- ICT 미래 핵심 소재부품 기술특집

- 페이지

- 13-20

- 발행일자

- 2016.12.01

- DOI

- 10.22648/ETRI.2016.J.310602

- 초록

- 실리콘 포토닉스 기술은 컴퓨터를 비롯한 여러 전자, 통신 기기들이 광 정보를 송수신하는 데 표준 실리콘을 이용하는 기술로, 기존 실리콘 반도체 기술과 호환될 수 있는 기술이다. 전자와 광의 융합기술로 실리콘 칩 사이, 또는 칩 내에서 빛으로 데이터를 주고받아, 데이터 전송속도를 획기적으로 올리면서도 전력 소모량을 크게 줄일 수 있는 것이 가능하다. 고성능, 저 생산비용과 낮은 소비전력 등의 장점 때문에, 전 세계적으로 실리콘 포토닉스 핵심기술/실용적 플랫폼 연구개발 및 상용화 경쟁이 이루어지고 있다. 본지에서는 실리콘 포토닉스 기술의 간략한 개요, 현재 동향 및 기술 이슈, 그리고 ETRI에서 연구개발된 실리콘 포토닉스 기술과 더불어 그 발전 전망에 대해 기술한다.

Share

Ⅰ. 서론

실리콘 전자회로 칩들이 빛으로 데이터를 주고받을 수 있다면, 즉, 실리콘 광 집적회로(silicon photonic integrated circuits(PICs))들이 CPU, Memory 등, 주요 실리콘 전자 회로칩(silicon electronic chips)에 칩-레벨(chip-level) 광 I/Os(Inputs/Outputs)로서 모노리식 집적되어(monolithic-integrated), 칩들 사이, 또는 칩 내에서 빛으로 데이터를 주고받으면, 미래 컴퓨팅과 데이터 통신에 혁신적인 변화(innovative changes)가 예상된다.

추후에, 실리콘 포토닉스(광) 기술이 성공적으로 미래 컴퓨터나 통신 시스템에 적용되어, 실리콘 전자 칩들에 모노리식(단일)-집적된 광 I/O가 전기적 I/O를 대체할 경우, 실리콘 포토닉스/Complementary Metal–Oxide–Semiconductor(CMOS) 플랫폼에 기반한, 저비용, 고성능, 전례 없는 대역폭 등을 제공하여 새로운 차원을 열어 줄 수 있다[1]. 즉, 실리콘 전자 칩들에서의 전자-광 융합(electronic-photonic convergence)의 실현은 컴퓨터 아키텍쳐(computer architecture), 데이터 커뮤니케이션(data communication), 텔레커뮤니케이션(tele-communication)에 있어서 혁신적 변화를 가져 올 수 있다.

따라서, 빛의 힘으로 움직이는 차세대 고성능 컴퓨터, 광컴퓨터 기술을 위한 데이터 송수신용 실리콘 포토닉 칩 기술의 개발이 요구되고 있다.

이러한 미래 선도기술의 개발은 컴퓨터에서 인터커넥션 병목현상, 속도문제, 열 문제 등을 해결하고 컴퓨터 장벽을 해소함으로써, 컴퓨팅 전자기기 및 IT 기기 전반에 걸쳐 성능을 향상시켜, 전자 정보 통신 분야를 한 단계 upgrade시킬 수 있는 기술이다. 또한, 반도체 및 전자, 광통신 전반에 적용 가능하여, 그 시장이 광범위하게 정의 될 수 있으며, 컴퓨터, 네트워크, 휴대기기, 로봇, 센서, 자동차, 디스플레이, 항공우주 등에 폭넓게 활용, 다양한 응용 분야 시장 창출이 예상된다.

또한, 이는 국내 반도체산업의 미래 컴퓨터 경쟁력 확보 환경 조성에 유리하다. 실리콘 기반 광소자 기술은 국내 우수한 반도체 관련 인프라를 바탕으로 신기술 및 핵심기술을 확보함으로써, 가깝게는 네트워크 광통신부품, 장기적으로 CMOS-compatible 실리콘-광기술 기반의 컴퓨터 부품, 휴대기기, 칩/전자 시스템 전반에 적용 가능하여[(그림 1) 참조], 거대한 Telecom/Infor-mation processing 관련 부품시장이 예상되며, 그 경제적 파급효과가 매우 클 것으로 예상된다.

실리콘 포토닉스 기술은 2004년 미국 인텔의 1Gbps급 실리콘 광모듈레이터를 비롯한 실리콘 포토닉스 관련 연구 논문들이 Nature지에 연달아 발표되어 전 세계적 주목을 크게 받게 되었으며[1]-[5], 특히, 2005년 미국 캘리포니아에 위치한 Luxtera사가 최초로 Silicon on Insulator (SOI)기판에 10 Gbps급 실리콘 능동/수동 (active/passive) 광소자들과 CMOS 인터페이스 전자회로들을 모노리식 집적한 칩(CMOS Photonics chip)을 발표하며, 실리콘 포토닉스 기술을 크게 선도하였다[6][7].

전 세계적으로 실리콘 포토닉스 핵심기술을 확보하기 위해, 미국정부, 인텔, IBM, Luxtera/Freescale, Oracle, HP, Micron사, MIT대, 코넬대, 싱가폴 IME, 유럽연합, IMEC, CEA-LETI, ST Microelectronics, 일본 NEC, PETRA 등 세계 유수기관에서 기술개발 경쟁 및 실용화 경쟁이 이루어져 왔으며[5]-[10], 현재, IME, IMEC, ST Microelectronics, Global foundry 등은 제한적인 실리콘 포토닉스 파운드리 서비스를 제공하고 있다[10].

국내에서는 한국전자통신연구원[11]-[19]과 삼성전자[20]에 의해, 각자 보유한 실리콘 팹(fab.)들을 기반으로, 독자적인 실리콘 포토닉스 연구개발들이 이루어져 왔다.

Ⅱ. 기술개요

실리콘 포토닉스 기술은 실리콘 칩에서 고성능 광통신을 가능케 하여, 궁극적으로, 컴퓨터 주요 실리콘 칩에 보편적으로 적용될 수 있는 것을 연구개발의 궁극 목표로 하고 있다[9].

실리콘 칩에 광통신의 building block들인 초소형 사이즈의 고성능(high-performance) 광소자들을 집적하여, 저가격, 초고속, 초저전력, 초소형을 지향하는 기술로, 집적 스케일과 칩당 functionality를 매우 크게 할 수 있다.

실리콘 칩 기반 광통신(광연결) 기술은, 초고속, 대용량 광통신을 가능케 하는 실리콘 능동 광소자군 및 수동 광소자군 기술 및 실리콘 기판상에서 모노리식 집적화(monolithic-integration)기술, 칩 패캐징 기술 등을 주요 구성 요소기술로 하며[1], 여기에, 실리콘 칩-레벨에서, 전기신호 회로(Electronic IC) 도메인과 광신호 회로(Photonic IC) 도메인을 연결해 주는 역할을 하는 광/전기신호의 인터페이스(interface)를 담당하는 초고속, 저전력 CMOS 회로기술을 포함한다.

전 세계적으로 이루어지는 종래 대부분의 실리콘 포토닉스 기술은 SOI 기판에서 정의되는 광 도파로형(optical waveguide type) 수평적(lateral) 소자들을 기본으로 하고 있다[1]-[9]. 주요 실리콘 포토닉(광) 소자로는, 실리콘 칩에서 전기신호를 광신호로, 또는 광신호를 전기신호로 바꾸어 처리하게 하는 실리콘 광변조기와 게르마늄-온-실리콘 광수신 소자 등의 빛을 능동적으로 제어할 수 있는 실리콘 포토닉 능동 광소자군 기술, 온-칩(on-chip) 광원기술 및 광신호 다중화(MUX)/역다중화(DeMUX) 실리콘 소자, 광커플러 소자 등의 수동 광소자군 기술, 실리콘 모노리식-집적화 기술(광집적화/광전집적화), 칩 패키징 기술, 광스위치 기술 등이다[1].

실리콘 광변조기(광모듈레이터)는 실리콘 반도체 칩 외부로 또는 실리콘 반도체 칩 내부에서의 신호 전송에서, 전기 신호를 디지털 빛 신호로 바꾸어 주는 전광변환(electric to photonic conversion) 기능의 소자로, CMOS 구동 driver IC와 광원들과 함께 칩-레벨 광 송신부를 이루는 핵심소자이다. 게르마늄-온-실리콘 광수신 소자는 실리콘 반도체 칩 외부에서 또는 칩 내부에서의 전송된 디지털 빛 신호를 전기신호로 바꾸어 주는 광전변환(photonic to electric conversion) 기능의 소자로, CMOS 전치증폭기 IC와 함께 칩-레벨 광수신부를 이루는 핵심소자이며, 초고속, 저전압, 고감도 소자 제작기술 및 게르마늄 에피탁시 기술을 포함한다. 실리콘 파장분할 다중화 광필터 기술은 실리콘 AWG, 실리콘 다채널 링공진기 필터 등을 포함하고, 다채널 도파로의 광신호를 외부와 연결하는 초정밀 저손실 광커플링 기술은, 저손실의 실리콘 그레이팅(grating) 커플러 및 저가, 고효율의 광커넥터 기술로 구성되며, 수동정렬(passive alignment), 집적도를 높일 수 있는 다채널 구조개발, 고정밀 및 양산 패키징 공정기술을 포함한다. 실리콘 포토닉 집적화 기술은, 칩 레벨의, 광 송수신이 가능한 실리콘 능동 광소자군 및 수동 광소자군의 실리콘 포토닉 모노리식 집적 칩 기술(Photonic Integrated Circuit: PIC)과 실리콘 포토닉 소자군과 CMOS 인터페이스 IC와의 광전집적 회로(Electronic- Photonic IC: EPIC)의 집적기술을 포함한다. 또한 실리콘 칩-레벨에서, 전기신호 회로도메인과 광신호 회로 도메인을 연결해 주는 CMOS 인터페이스 회로 기술은 초고속 저전력 광변조기 구동회로(Driving Circuitry), 광원 구동회로와 Transimpedence Amplifier (TIA), Limiting Amplifier (LA)등의 고속 광수신 전류증폭 회로(Amplifying Circuitry)와 전기신호를 시간 축에서 다중화하는(SERDES) 회로를 포함한다.

III. 현재 동향

그동안, 전 세계적으로, SOI 기판 기반의 실리콘 포토닉스 소자들의 성능이나, 집적화 수준에서 괄목할만한 발전을 보여주어 왔으며, 칩 레벨의 모노리식 광전-집적에 기반한 광연결(optical interconnects)을 목표로, 실리콘 광소자들의 성능 및 더 높은 집적도 달성을 위한 계속적인 연구개발이 진행되고 있다[1]-[15].

그러나 20년 가까운 연구에도 불구하고, 실리콘 포토닉스 기술의 현주소는 아직 전자 칩에 들어갈 수 있는 정도의 기술력과는 거리가 먼 상태이다. 실리콘 포토닉스 소자들을 전자 칩에서 실제 광I/O로 사용하고자 하는 노력은, 아직도 소자들의 큰 사이즈, 저 성능, 고 전력 소모, 기존의 microelectronics와의 기판(substrate) 불일치, 온-칩(on-chip) 모노리식 집적 광원의 부재 등, 주요 난제들로 심각한 난관에 직면하고 있다[13][19].

현재 전세계적으로, 이제까지의 대부분 연구 성과들을, 우선, 네트워크 광통신, 데이터 센터 등을 타깃 (target)으로 그 적용시장을 찾고 있다. 실리콘 포토닉스 기술을 선도하는 Luxtera는 Freescale 제작공정 기반으로, 4~5년 전부터 각종 상용 CMOS 포토닉 광송수신기를 내놓고 있으며(Molex사)[6][7], Mellanox사, 인텔[5] 등도 최근 100Gbps급(25Gbps×4channel) 광송수신기 상용제품 등을 선보이고, SiFotonics사가 게르마늄(Ge) 아발란치 광수신소자(Avalanche Photodetector: APD) 등의 상용제품을 내놓고 있다. 현재, IME, IMEC, ST Microelectronics, Global foundry 등이 일반에 제공하는 제한적인 실리콘 포토닉스 파운드리 서비스는 상용수준과는 거리가 있다[10].

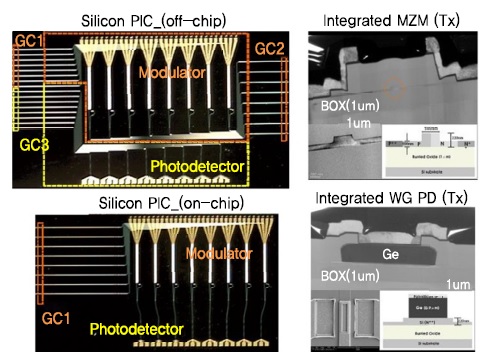

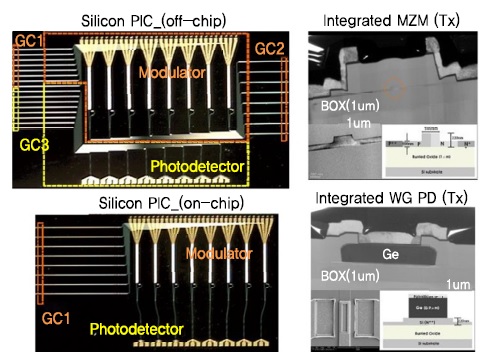

국내에서는, ETRI가 보유한 고유의 silicon fab. 기반으로 독자적으로 연구 개발하여 확보한, 세계적 수준의 SOI 기판 기반 실리콘 포토닉스 성과로는[11]-[18], 40Gbps급 모노리식-집적 실리콘 광송수신 광집적회로(Si-PIC) [(그림 2) 참조][11][12][17], 실리콘 하이브리드 집적 광전회로(Si Electronic-Photonic IC, EPIC) [11][12][17], 40/50 Gbps급 초고속 실리콘 MZ 광변조기, Ge 광수신소자 등의 능동 광소자들[11][15][17], 그리고 벌크-실리콘 (bulk-silicon) 기판 기반의 초고속, 고성능 게르마늄 광수신 소자[16][17], 10/25Gbps 고감도 게르마늄 아발란치 광수신소자(Ge APD)[18] 등, 핵심 실리콘 광소자들이 실용수준으로 확보되어, 기존의 상용 제품에 버금가거나, 능가하는 성능들을 보유하고 있어, 우선, 네트워크 광통신, 데이터 센터시장을 타깃으로 하는, 기술이전을 통한 상용화가 기대되고 있다.

IV. 현재 이슈

앞서 이야기했듯이, 전 세계적으로 대부분의 실리콘 포토닉스 테크놀로지는 SOI 기판에서 정의되는 광 도파로형(optical WaveGuide type) 수평적(lateral) 소자들을 기본으로 하고 있다[1]. 이는 실리콘 전자 칩에 실용적인 실리콘 광I/O 구도를 적용하기 되기에는 주요 장애 요소들을 근본적으로 포함하고 있다[13][19].

그 주요 장애요소로, 첫째, 소자 측면에서는 현재까지소자의 큰 사이즈, 낮은 동작효율(low operational efficiency), 고전력 소모(high power consumption) 등이 있다. 둘째, 실리콘 전자 칩에 실용적인 실리콘 광I/O 구도를 적용하기 위한 소형 온-칩(on-chip) 광원(light source)의 구현이 용이하지 않은 것이 매우 심각한 문제이다. 셋째, 칩-레벨 광 연결을 적용하는데 방해가 되는 핵심 기판(substrate) 이슈로, 기존의 통상적인 전자 칩들과의 기판 불일치(substrate incompatibility)이다. 즉, 대부분 전자 칩들은(electronic chips) 벌크 실리콘 웨이퍼 기판을(bulk silicon substrate/wafer) 사용한다. 반면에, 대부분의 주요 실리콘 포토닉 소자들은 광도파로 타입(waveguide-type)으로 SOI 기판 같은 빛을 국한시킬 수 있는 환경이 필수적이다. 따라서 SOI 기판 기반의 광전 융합(electronic-photonic convergence)은 현재로는 실용적이지도, 현실적이지도 않은 실정이다. 일부에서, 벌크-실리콘 기판에 국소적 SOI 형태의 영역을 형성하고 수평적(lateral) 광도파로 타입의 소자들을 집적하는 시도가 되고 있거나, 광 인터포져(optical interposer)를 활용하여 분리된 전기회로 칩과 광회로 칩을 분리하여 광연결 시도가 이루어지고 있는 실정이다. 여기에 더해서, 현재 Ⅳ족 원소들에 기반한 실용적 칩-레벨 광원이 가능하지 않은 관계로, Ⅲ-V족 화합물 반도체 기반의 제작된 레이저 칩들이 외부광원으로써, SOI 칩에 플립칩 형태로 본딩되거나 패키지되어서, SOI 기판 위에 집적된 고속 실리콘 포토닉 변조기에 CW(연속발진, continuous wave)빛을 공급함으로써 송신기가 완성되고 있다. 따라서 모노리식 집적화 기반의 자족형(self-contained) 칩-레벨 광 I/O set를 완성할 수가 없는 실정이다. 실리콘 on-chip광원의 한 솔루션으로 인텔에서는, SOI 기판 위에 웨이퍼 본딩을 이용하여, III-V 화합물 레이저 에피(epi)의 활성층(active layers)을 이식한 후, on-chip 레이저를 공정하여 완성한 silicon hybrid laser를 연구 개발하여 발표하였으며[4], 현재 상용 실리콘 포토닉 광송수신기에 적용하고 있다[5]. 그러나 칩-레벨 광I/O 적용으로는 아직 크기 및 전력소모 등이 작아져야 하며, 또한 SOI 기판 사용이 필수적이라, 여전히 근본적인 기판 불일치 문제는 안고 있다.

따라서, 위의 주요한 문제점들을 극복하고 실리콘 칩 레벨에서의 광전 집적화를 용이하게 하는 새로운 광I/O 구도가(new photonic I/O scheme) 주요한 관심사이다[19].

V. ETRI 실리콘포토닉스 테크놀로지

ETRI에서는, 종래의 주요 흐름인 SOI 기판 기반의 실리콘 포토닉스의 세계적 수준의 기술력 확보 [11][12][15][17]와 더불어, 벌크 실리콘(Bulk-silicon) 기판 기반의 실리콘 포토닉스 연구개발도 진행되었다[11][16]-[19].

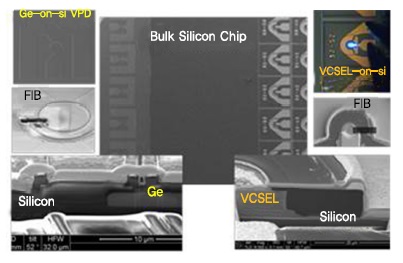

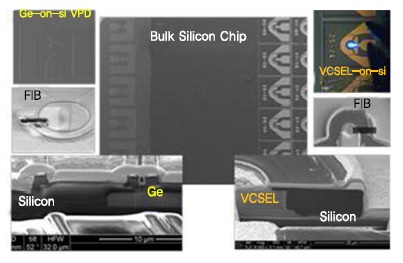

앞 장에서 서술한 바와 같이, 현재 전 세계적으로, 실리콘 포토닉스 기술의 실질적 전자 칩 적용을 어렵게 하는 3대 주요 이슈인, 기판문제, 소자 크기/성능문제, 칩-레벨광원 문제를 극복하는 새로운 광I/O 플랫폼으로, 실리콘 칩간의 광통신을 가능케 하는 벌크-실리콘(bulk-silicon) 기반의 단일칩 광송수신기(트랜시버)를 세계 최초로 개발하였다[13][19]. (그림 3)은 ETRI에서 연구개발한 벌크-실리콘 기반의 광 송수신 단일칩이다.

ETRI의 실리콘 광 I/O 단일 집적플랫폼 기술은, 통상적인 전자회로 칩에서 사용되는 벌크 실리콘 웨이퍼를 사용하고, 수직형 광소자들을 단일 집적하는 방식으로, 광송수신 집적회로(PIC)의 집적화 수준을 on-chip 광원을 포함하는 완성된 칩-레벨 광I/O 집적 구도를 제시하였다. 벌크 실리콘 웨이퍼 위에 선택적 게르마늄 에피 성장 및 실리콘 CMOS-compatible 공정과, 화합물 반도체 레이저 박막을 실리콘 웨이퍼 표면에 이식시킨 후 광소자를 제작하는 추가공정을 통해, 직접 변조 (direct-modulation) VCSELs-on-Si 광원을 포함한 수직형 광 I/O 소자가 모노리식 집적되는, ETRI 독자적 플랫폼 기술이다. 즉, 벌크 실리콘 기판 위에 모노리식 집적된 수직형 광 송수신(TRx) 소자들 기반의 단일칩 광트랜시버칩(single-chip photonic transceiver)기술이다. 빛 파장대역은 650nm에서 1550nm 전 파장대역에 적용 가능한 구도이며, 전자-광 집적화(electronic-photonic integration) 실리콘 칩의 실현을 위한 소형 저가격의 칩-레벨 광I/O해법을 제공할 수 있다.

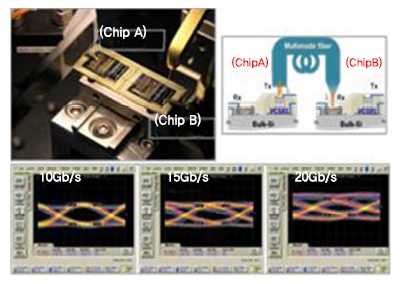

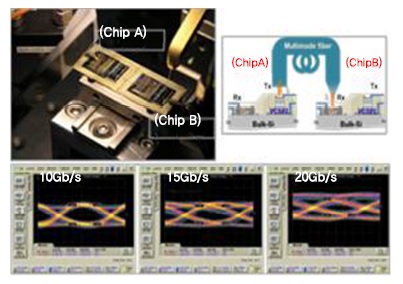

ETRI는, (그림 4)에서 보이는 바와 같이, 실리콘 칩간의 초당 20 기가 비트/채널 데이터의 저전력 초고속 광연결을 프로토타입으로 선보이며, 고속으로 작동하는 viable한 칩-레벨 광 I/O 플랫폼으로, 소형, reliable, 저 에너지 소모의 칩-레벨 플랫폼으로 사용될 수 있다는 것을 실험적으로 증명하였다.

본 광I/O구도가 최소한의 extra cost와 reliable operation으로, 비용 효율이 높은(cost-effective) 대량생산 기반의 미래 실리콘 광통신(future silicon-based optical communications)의 큰 가능성을 보여줄 것으로 예상된다. 본 기술이 미래 실리콘 전자 칩에 초고속, 고밀도 광I/O 플랫폼으로 적용될 경우, 웨이퍼 레벨의 양산 공정이 가능하고, 비약적으로 향상된 데이터 입출력 속도 및 대역폭에 기여할 수 있을 것이다.

본 기술은 평면상의 데이터 통신뿐만 아니라, 3차원 칩 적층 구조의 IC간 데이터 통신에도 유리하여, 3D 적층형 메모리, 적층형 컴퓨터 시스템 등에도 응용 가능하며, 가깝게는 각종 네트워크 광트랜시버로 바로 적용될 수 있다.

VI. 결론

전 세계적으로 실리콘 포토닉스 기술 개발에 있어 실제적용 가능하며, 간단하고(simple), 저가격화(cost-effective/cost reduction)하고, time-to-market에 유리한 플랫폼 개발 경쟁을 벌이고 있다.

ETRI에서 연구개발되어 확보된 벌크-실리콘 단일칩 광송수신기 기술은, 실리콘 칩에서 소형(compact) 자족형(self-contained) 광 I/O를 실현할 수 있는 기술로, 실리콘 기반 칩-레벨 광연결의 실질적 적용(practical implementation)을 막는 이슈들, 즉, 벌크 실리콘 CMOS microelectronics와의 기판 substrate-compatibility 이슈, 온-칩 소형 저전력-소모 광원 문제를 동시에 해결함으로써, 저전력 실리콘 광연결을 실현시킬 수 있는 구도이다. 저가의 벌크 실리콘 웨이퍼에 광 입출력(I/O) 소자를 제작하므로써, 기존의 전자회로 실리콘 칩들에 광데이터 입출력 기능을 부가시킬 수 있는 단일집적 플랫폼기술로, 전자 집적회로(IC)와의 통합성을 크게 증가시키고, 칩-들 사이에 광 데이터의 실용적 송수신이 이루어질 수 있다. 또한, 실리콘 기반의 고성능 광송수신 소자들의 단일칩화에 따른, 소형화, 저가격화, 저전력화 등의 이점으로, 컴퓨터 칩에서부터 광통신 부품, 모바일기기, 센서, 디스플레이 등 광범위한 산업에 폭넓게 적용 가능한 기술이며, 향후 이 플랫폼 기술이 고성능 컴퓨터(HPC), 휴대기기, CPU, 메모리, 3차원 IC, 데이터센터 및 네트워크 광통신 부품, 디스플레이 분야에서 전자-광자 통합(융합)의 실현에 기여할 것으로 예상된다.

ETRI에서 독자적으로 연구 개발된 실리콘 포토닉스 기술 들은 앞으로, 초고성능 컴퓨터의 광I/O 플랫폼으로 적용될 경우, 수퍼 컴퓨터 내 초고속 광연결 하드웨어 개발에 기여할 수 있을 것으로 기대된다. 또한, 빠른 속도로 성장하고 있는 실리콘 광 인터커넥션 시장에 대비한, 액티브 광케이블, 고성능 광커넥터, 네트워크 광트랜시버, 휴대기기, 디스플레이 등에 적용될 수 있는 저가격 고경쟁력 실리콘포토닉 광부품의 기술이 확보되었다. ETRI에서 이미 실용 수준으로 개발된 실리콘 포토닉스 기반의 게르마늄 광수신 소자, 고감도 아발란치 광수신소자 (APD) 기술 등과 더불어 상용화함으로써, 실리콘 광부품 시장의 활성화에 이바지할 수 있을 것으로 기대한다.

약어 정리

APD

Avalanche PhotoDetector

CMOS

Complementary Metal-Oxide-Semiconductor

EPIC

Electronic-Photonic Integrated Circuit

HPC

High Performance Computer

I/O

Input/Output

LA

Limiting Amplifier

PD

PhotoDetector, PhotoDiode

PIC

Photonic Integrated Circuit

SOI

Silicon-On-Insulator

TIA

Transimpedence Amplifier

WDM

Wavelength Division Multiplexing

A. Liu et al., “A High Speed Silicon Optical Modulator based on a Metal-Oxide-Semiconductor Capacitor,” Nature 427, 2004, pp. 615-618.

A.W. Fang et al., “Electrically Pumped Hybrid AlGaInAs-Silicon Evanescent Laser,” Optics Express, vol. 14, no. 20, 2006, pp. 9203-9210.

Intel's Silicon Photonics, http://www.intel.com/ con-tent/www/us/en/architecture-and-technology/sili con-photonics/silicon-photonics-overview.html

C. Gunn, “CMOS Photonics for High-Speed Interconnects, ” IEEE. Micro., vol. 26, no. 2, 2006, pp. 58-66.

IBM's Silicon Photonic Technology, May 12th, 2015, https://www-03.ibm.com/press/us/en/pressrelease/46839.wss

D. Miller, “Device Requirements for Optical Interconnects to Silicon Chips,” Proc. IEEE, vol. 97, no. 7, 2009, pp. 1166-1185.

A. Novack et al., “30GHz Silicon Photonic Platform, ” Proc. in IEEE, International Conference on Group IV Photonics, WA4, 2013, pp. 7-8.

G. Kim et al., “Silicon Photonic Devices based on SOI/Bulk-Silicon Platforms for Chip-Level Optical Interconnects,” Proc. SPIE 9368, 2015, 93680Z-1-7

G. Kim et al., “Low-Voltage High Performance Silicon Photonic Devices and Photonic Integrated Circuits Operating up to 30 Gb/s,” Optics Express 19, 2011, pp. 26936-26947.

김경옥, “미래컴퓨팅/데이터 통신에 혁신을 가져올 실리콘 포토닉스 기술,” ETRI Webzine, vol. 42_Story, 2015.7.16, https://webzine. etri.re.kr/20150710/sub04.html

G. Kim, “Silicon Photonics Technology to Innovate Future Computing/Data Communication,” ETRI Webzine #18, April, 2016.

G. Kim et al., “Compact-Sized High-Modulation-Efficiency Silicon Mach-Zehnder Modulator based on a Vertically Dipped Depletion Junction Phase Shifter for Chip-Level Integration,” Optics Letters 39, 2014, pp. 2310-2313.

I. Kim, et al., “High-Performance Photoreceivers based on Vertical-Illumination Type Ge-on-Si Photodetectors Operating up to 43 Gb/s at λ~1550nm,” Opt. Express 21, 2013, pp. 30718-30725.

J. Joo et al., “Silicon Photonic Receiver and Transmitter Operating up to 36 Gb/s for λ~1550 nm,” Optics Express 23, 2015, pp. 12232-12243.

K. Jang et al., “High Performance Ge-on-Si Avalanche Photodetector,” Proc. SPIE 97553, 2016, 997531C-1.

G. Kim et al., “Single-Chip Photonic Transceiver based on Bulk-Silicon, as a Chip-Level Photonic I/O Platform for Optical Interconnects,” Scientific Reports 5, 11329; doi: 10.1038/srep11329, 2015.

- Sign Up

- 전자통신동향분석 이메일 전자저널 구독을 원하시는 경우 정확한 이메일 주소를 입력하시기 바랍니다.