김용해 (Kim Y.-H.) 실감영상소자연구실 책임연구원

김기현 (Kim G. H.) 실감영상소자연구실 책임연구원

양종헌 (Yang J.-H.) 정보제어소자연수실 선임연구원

피재은 (Pi J.-E.) 정보제어소자연수실 선임연구원

황치영 (Hwang C.-Y.) 정보제어소자연수실 연구원

최지훈 (Choi J.) 정보제어소자연수실 연구원

김진웅 (Kim J.) 기가서비스연구부 책임연구원

Ⅰ. 디지털 홀로그래피 기술동향

홀로그래피 기술은 1947년에 헝가리 물리학자인 데니스 가보르(Dennis Gabor) 가 전자현미경에 대한 연구과정에서 발명되었으나[1], 1962년에 레이저를 홀로그램 생성에 이용할 수 있게 되면서 비로소 많은 연구자들이 관심을 나타내게 되었다.

아날로그 홀로그래피는 3차원 물체에서 반사되거나 발생한 빛의 정보(전자기파의 진폭과 위상)를 기준파를 이용하여 간섭무늬 형태로 감광판에 기록한다. 감광판에 기록되는 간섭무늬의 공간주파수는 ~5000lpm(lines per millimeter) 정도로 매우 높으므로, 감광판의 재료로 사용되는 은 화합물의 그레인 크기는 ~10nm로 매우 정교하게 조절되어 제작된다. 감광판에 기록된 간섭무늬는 사진 인화와 유사한 공정을 거쳐서 홀로그램 재생이 가능한 형태로 가공된다. 현상된 감광판에 기준파를 조사하게 되면 기록되어 있던 3차원 물체의 정보에 해당하는 빛이 발생하여 사람의 눈에 입사하게 되고, 이에 사람들은 입체영상을 보는 듯한 느낌이 들게 된다. 이처럼 재현된 아날로그 홀로그래피 영상은 매우 훌륭한 품질을 나타내지만, 여러 가지 약점도 가지고 있다. 첫째, 감광판을 사용하기 때문에 동영상을 기록하거나 재생하기에 어려움이 있고, 둘째, 감광판을 인화하는데 시간이 많이 필요하게 되고, 셋째 감광판에 기록하기 위해서는 어두운 암실에서 레이저를 사용하여야 하는 단점이 있다.

아날로그 홀로그래피의 약점을 보완하기 위한 디지털 홀로그래피에 대한 개념은 1960년대에 알려졌지만, 실질적으로는1990년대에 대용량 이미지 센서 및 디스플레이 기술이 발전함에 따라 활발히 연구되기 시작하였다.

디지털로 홀로그램 간섭무늬를 기록하는 방법으로는 CMOS 이미지 센서를 이용한 위상 변이 홀로그래피(phase shifting holography) 기술을 이용한다[2]. 아날로그 홀로그래피에서는 감광판에 기록되는 정보 중 0 차항과 쌍둥이 이미지를 제거하기 위해서 비축(off axis) 홀로그래피 기술을 사용할 수 있다. 하지만 현재 개발된 CMOS 이미지 센서의 픽셀 크기가 ~ 수 µm로 아날로그 감광판의 해상도에 비해서는 매우 낮기 때문에 디지털 홀로그래피에서는 비축 홀로그래피 기술을 사용할 수 없다. 따라서 디지털 홀로그래피에서는 잡음으로 기록되는 0차항과 쌍둥이 이미지를 제거하기 위해서는Piezoelectric Transducer(PZT)에 의해 2개의 광 경로 중 한쪽 광 경로를 파장 이하의 크기에서 변하도록 조정하여 여러 장의 간섭무늬를 기록한 다음 수치적으로 제거하는 방법을 이용하여야 한다.

3차원 물체가 실물이 아닌 모델링일 경우에도 컴퓨터 홀로그래피 기술을 이용하여 간섭무늬를 계산할 수 있다. 3차원 물체에서 빛이 회절하여 전파되는 과정은 Rayleigh-Sommerfeld 회절 식을 통하여 정확하게 예측할 수 있지만, 시간이 오래 걸리는 단점이 있다. 계산 시간을 단축하기 위하여 빛의 전파 거리에 따라 최적의 근사식을 이용하여 계산하는 방법들이 최근에 많이 개발되어 있고[3], 또한 컴퓨터의 성능이 계속해서 향상되고 있기때문에 컴퓨터를 이용한 홀로그램 간섭무늬를 계산하는 방법은 많은 연구자가 사용하고 있다.

디지털로 기록된 간섭무늬를 이용하여 3차원 홀로그램 이미지를 재현하기 위해서 디지털 홀로그래피에서는 상용화된 마이크로 디스플레이를 Spatial Light Modulator(SLM)으로 사용했다. 프로젝터에 주로 사용되는 Digital Micromirror Device(DMD)는 빠른 속도(수십 kHz)로 진폭 변조가 가능하다는 장점 때문에 디지털 홀로그래피의 SLM으로 사용되어 왔다[4][5]. DMD SLM을 시분할 방식을 이용하여 구동한다면 재생 이미지의 크기를 늘리거나 재생 이미지의 시야각을 넓힐 수 있다. 하지만 DMD는 고전압에서 안정적으로 동작하는 6개의 트랜지스터를 이용하는 SRAM 이 사용되어야 하고, 반사거울이 기계적으로 기울어져야 하므로 픽셀피치(~7µm) 를 줄이는 데 한계가 있고, 또한 이진 구동만 가능하기 때문에 재생이미지의 계조 표현에 한계를 가지고 있다.

디스플레이에 주로 사용되는 액정은 진폭 변조와 위상 변조가 모두 사용 가능하고, 또한 투과형 SLM 및 반사형 SLM 모두 가능하므로 디지털 홀로그래피에서 많이 사용되고 있다. 최근에 Holoeye 사에서 발표한 GAEA SLM 은 Liquid Crystal on Silicon(LCoS) 기술을 이용하여 제작되었는데 픽셀 피치가 3.74µm 로 현재까지 개발된 SLM 중 가장 높은 해상도를 나타내었다[(그림 1) 참조][6].

하지만 아날로그 홀로그래피에서 사용하는 감광판에 비해서는 액정을 이용한 SLM 의 픽셀 피치가 여전히 크기 때문에 3차원 재현 이미지의 시야각이 매우 작다는 약점이 있다. 픽셀피치를 줄이기 위해서는 픽셀간의 크로스톡(crosstalk) 을 줄이는 노력 및 구동 트랜지스터의 크기를 줄이는 노력이 동시에 필요하다[5].

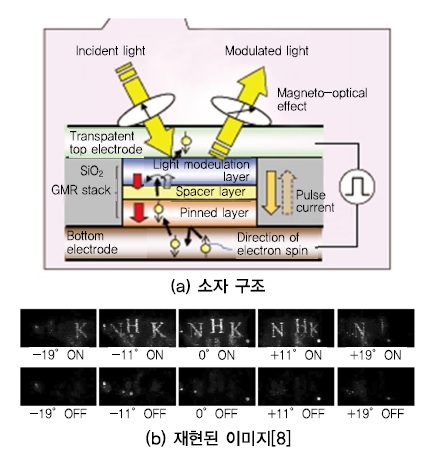

동영상 재현에는 한계가 있지만 픽셀피치만을 줄여서 정지영상을 재현하는 방법도 디지털 홀로그래피 기술 연구에서 많이 연구됐다. Cambridge 대학에서는 플라즈모닉 나노 입자 기술을 이용하거나 Carbon Nanotube (CNT)를 이용하여 픽셀피치가 ~400nm인 SLM을 개발하였다. 이외에도 NHK에서는 거대자기저항(Giant magnetoresistance) 기술을 이용하고, ETRI 에서는 상전이 물질을 이용하여 픽셀 피치 1µm 급 SLM 을 개발하였다[7].

이상 살펴본 바와 같이 디지털 홀로그래피가 아날로그 홀로그래피와 비슷한 품질을 나타내기 위해서는 SLM 픽셀피치가 감광판에 사용되는 은 화합물의 그레인 크기와 비슷하고, SLM 크기가 감광판의 크기와 비슷하여야 하는데 현재로서는 달성하기 어렵다. 단기적으로는 1µm 의 픽셀피치를 가지고 있는 5인치 크기의 SLM 을 개발할 수 있다면 재생된 홀로그램을 관측하기에 어려움이 없고 품질도 우수할 것으로 예측하고 있다. 본고에서는 대면적 초고해상도 SLM 패널 기술의 필요성 및 현황을 소개하려고 한다.

Ⅱ. 대면적 초고해상도 SLM의 개발방향

앞장에서 살펴본 바와 같이 최근까지의 초고해상도 SLM은 미세 피치 픽셀 구현에 유리한 반도체 기술을 바탕으로 개발되어왔다. 공정기술과 소자기술의 눈부실 발전으로 10nm이하의 CD를 가지는 반도체 기술이 개발되었으나, 반도체 기술에서는 기술의 발전 방향이 미세화를 통한 패턴 피치의 감소, 구동 전압의 저감, 그리고 궁극적으로 칩 면적의 소형화를 지향하기 때문에 디바이스 전체 면적이 빛을 조절하여야 하는 SLM의 경우에는 단점이 될 수도 있다. 또한, 빛을 변조해야하는 SLM에 있어서 일반적으로, 변조에 필요한 구동 전압은 피치의 미세화와 함께 줄어들지 않으나, 반도체 공정으로 제조되는 구동소자(MOSFET등)의 전압은 피치의 미세화에 따라 감소되기 때문에, 미세화가 진행됨에 따라 광변조소자의 구동이 어려워지는 문제가 발생하게 된다. 예를 들어 LCoS의 경우 실리콘 웨이퍼상에 반도체 공정으로 LCD 패널을 구성하기 때문에 미세화는 가능하지만, 미세화에 따라 구동 전압의 감소를 고려하면, 특정 피치 이하의 소자 구현이 대단히 어려워진다. 그런 까닭으로 LCoS 패널의 최소 피치를 쉽게 내릴 수 없어 현재 3.74µm수준에 머무르고 있다.

한편 평판 디스플레이 기술의 경우에는 대면적화를 지향하는 기술 방향을 추구해왔다. CRT 모니터의 한계였던 40인치급을 넘어선 평판 디스플레이 기술은 100인치급이상의 구현에도 기술적으로는 제약이 없을 정도의 대면적 기술을 가지게 되었다. 또한, 높은 품질의 화질을 추구하여 사람의 눈에 화소가 구분되지 않는 ‘retina display’를 지향하게 됨에 따라, 중소형 디스플레이 패널의 경우 현재 800ppi 급의 고해상도 패널 기술을 보유하고 있다. (그림 3) 또한, 무안경 3D 기술이나 light field 디스플레이 등의 구현을 위하여 초고해상도 패널의 개발 필요성이 제기되고 있다.

결국, 홀로그래피를 구현하기 위한 SLM의 경우에도 궁극적으로 대면적 홀로그램을 구현하기 위해서는 대면적 구성이 가능한 평판디스플레이 기술 기반으로 개발되어야 할 것으로 생각된다. 즉, glass 기판을 사용하고, Thin-film Transistor를 구동 소자로 채택하는 것이 필요할 것이다. 또한, 광변조소자도 되도록이면 평판 디스플레이 공정과 상호 호환성이 있는 소자의 선정이 유리하다고 할 수 있다.

그러나, 평판 디스플레이 기술을 바탕으로 초고해상도SLM을 개발하기 위해서는 기술적으로 해결해야 할 문제들이 많이 있다. 우선 기판으로 사용되는 유리의 평탄도 문제를 해결해야 한다. 고화질 디스플레이를 지향하면서 국부적인 유리의 평탄도, 즉 거칠기는 매우 향상이 되었지만, 거시적으로는 휘어짐(warpage) 현상이 존재할 수 밖에 없다. 이 현상에서 오는 오차가 수십 µm 이상(전체 기판 기준)되기 때문에 빛의 간섭 현상을 이용하는 광변조소자의 경우 이러한 오차를 보상하는 방법이 필수적으로 필요하다.

또한, 현재 디스플레이 패널을 제조할 때 사용하는 포토 리소그래피 공정의 최소 패턴 크기는 1µm근방에 머무르고 있다. 그런데, 앞에서 살펴본 바와 같이 시야각을 확보하기 위해서는 1µm이하의 픽셀 피치를 구현하는 것이 필수적이다. 따라서 1µm이하의 패턴을 구현하기 위한 포토리소그래피 장비의 개발 혹은 보조적인 수단을 이용한 미세 패턴 형성 공정의 개발이 필요하다.

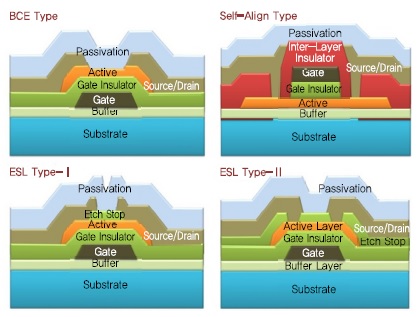

고해상도 디스플레이의 경우 Thin-Film Transistor (TFT)를 구동소자로 채택하고 있다. TFT는 Si 기판위에 형성되는 MOSFET와 달리 유리 기판위에 박막 구조로 형성되므로 높은 구동 전압을 견디도록 설계하기에는 용이하다. 그러나 결정질 반도체를 채널층으로 사용하는 MOSFET에 비하여 비정질 반도체 혹은 다결정 반도체를 사용하게되는 TFT의 경우 이동도가 낮다는 단점을 가지고 있다. 또한, 미세화가 진행되어 짧은 채널, 얇은 절연막 구조를 채택할 수 밖에 상황에서 여전히 높은 구동 전압을 견딜 수 있는지는 향후 과제가 될 것으로 생각된다.

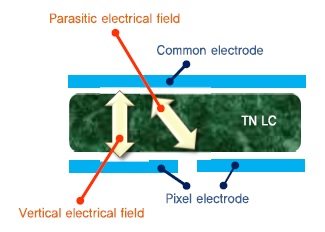

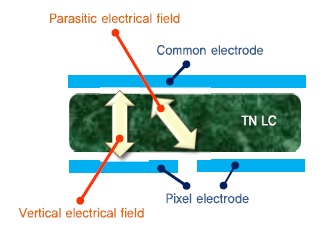

평판 디스플레이서 대표적인 광변조소자는 액정의 경우 낮은 구동전압에서 빛의 위상 혹은 편광을 효과적으로 바꿀 수 있어 널리 사용됐다. 이때 빛의 변조는 광경로에 비례하여 증가되므로 일정 두께 이상의 액정구조 (Cell Gap)를 필요로 한다. 그런데, 픽셀의 미세화가 진행되어 픽셀 간격이 액정 두께보다 작아지게되면, 액정에 미치는 픽셀 전극의 효과가 이웃한 픽셀 전극의 영향을 받게 되는 현상이 발생할 수 밖에 없다. 이러한 이웃 픽셀 전극의 영향을 크로스톡(Cross-Talk) 현상이라 부르는데, 이 현상을 감소시키기 위해서는 짧은 광경로에서도 충분한 광변조를 만들어 낼 수 있는 새로운 액정 소재의 개발이 필수적이 될 것으로 예상된다.

마지막으로 현재의 고해상도 평판 디스플레이는 게이트 전극들과 데이터 전극을 통하여 개개의 픽셀에 필요한 정보를 공급하는 매트릭스 구조로 되어 있다. 이러한 게이트 전극들과 데이터 전극들을 구동칩(driver chip)을 통하여 제어하는 방법을 사용하여왔다. 그런데 구동칩은 반도체 공정을 사용하여 제조되기 때문에 물리적인 면적의 한계가 있다(반도체 공정에서는 일정한 패턴을 반복하는 스텝-앤-리피트(step-and-repeat) 공정을 사용하게 된다. 이때 단위 패턴의 크기는 포토 리소그래피 장비의 한계 때문에 약 30mm×30mm크기 정도로 제한되게 된다). 또한, 칩에서 나오는 전기신호를 외부에 전달하기 위해서는 패드를 형성하여 이를 접합하는 방식을 사용하는 데, 현재까지 개발된 접합 방법에서는 이러한 패드들의 피치가 약 10µm 내외로 제한되고 있다. 그런데 앞에서 살펴본 바와 같이 픽셀의 피치가 1µm이하가 되어야 하므로 게이트 전극과 데이터 전극 모두 혹은 둘중의 하나는 1µm 이하의 피치로 형성되게 될 것이다 현재로는 이러한 피치의 전극 선들을 외부의 구동칩과 연결할 방법을 가지고 있지 않다. 따라서 대규모의 데이터(예를 들어 1µm 픽셀 피치를 가지는 100mm×100mm 패널의 경우 100K×100K(10G)의 데이터가 필요하다.)를 전달해야 하기 위한 새로운 구동 방식의 개발이 필요하다.

Ⅲ. 디스플레이 기술 기반 대면적 초고해상도 SLM 개발

ETRI에서는 2013년부터 정부의 지원(범부처 Giga Korea사업)을 받아 디스플레이 기술을 기반으로 한 대면적 초고해상도 Spatial Light Modulator on Glass (SLMoG) 패널을 개발하고 있다. 본 장에서는 지금까지 개발된 기술 내용과 향후 개발방향에 대하여 기술하고자 한다.

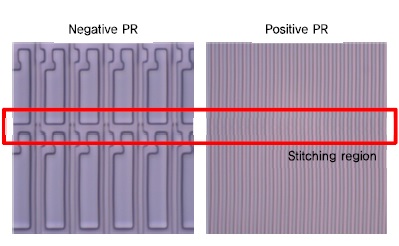

1. 미세 피치 포소리소그래피 공정

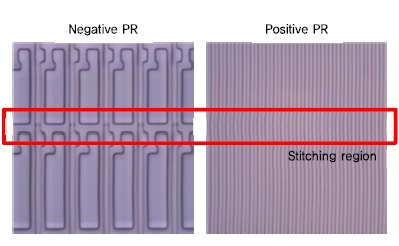

미세 패턴을 구현하기 위해서는 축소 노광 기반의 스텝-앤-리피트 방법의 사용이 필수적이다. 그런데, 일반적으로 축소 노광 방식에서는 한 번에 노광이 가능한 면적이 제한적이기 때문에, 대면적 SLM 패널을 구현하기 위해서는 노광되는 부분을 겹쳐서 진행하는 스티치(stitch) 공정 개발이 필요하다. 이러한 스티치 공정에서는 겹쳐서 노광되는 부분의 길이를 최적화하여야 겹침 부분의 패턴 이상을 방지하는 것이 가능하다. ETRI에 설치된 i-line stepper를 이용하여 스티치 공정을 실시하였다. 특히 양의 방식으로 노광되는 포토 레지스터(positive PR)를 사용하여 공정의 용이성을 확보하였다. 다음 (그림 5)는 이러한 스티치 공정을 이용한 패턴 형성 결과를 보여주고 있다.

그런데, 패널 중에서 픽셀부의 경우에는 반복되는 패턴이 대부분이기 때문에 앞서 소개한 스티치 공정을 통하여 패턴 형성이 가능하지만, 외곽부(특히 패드부 혹은 패드와의 배선 연결부)는 반복되는 패턴이 없으므로 스티치 공정으로 형성하기 어려운 점이 있다. 이러한 부분은 상대적으로 패턴의 미세도가 덜하기 때문에 축소 노광 방식이 아닌 1:1 노광이 가능한 노광기를 사용하는 것이 경제적이다. 이렇게 서로 다른 장비를 사용하여 하나의 기판상에 패턴을 형성하는 방법을 믹스-앤-매치 방법이라고 부른다. ETRI에서는 이러한 방법을 적용하여 i-line stepper와 projection aligner를 한꺼번에 적용하여 SLM 패널을 개발하였다. 다음 (그림 6)은 전체 패널을 스티치 방법과 믹스-앤-매치 방법으로 분할하여 패턴 형성하는 방법에 대한 모식도이다.

2. 1µm급 TFT 소자

디스플레이는 단결정 웨이퍼 상에서 디바이스를 만드는 반도체와는 달리 대면적이 가능한 유리를 기판으로 사용하고 있다. 공정 온도와 하부층의 제한으로 유리 기판상에는 단결정층의 형성이 어렵기 때문에 구동소자인 트랜지스터의 반도체층으로 비정질 반도체나 다결정 반도체를 사용하게 된다. 지금까지는 실리콘 기반의 비정질 실리콘이 주로 TFT-LCD에 다결정 실리콘이 주로 AMOLED에 사용됐다. 비정질 실리콘은 대면적 균일성은 우수하나 이동도 특성이 좋지 않고(이동도 ~ 1cm2/Vs), 다결정 실리콘은 대면적 균일성은 좋지 않으나, 이동도 특성이 우수한 편(이동도 50~100cm2/Vs)이다. 최근 비정질 금속 산화물이 우수한 대면적 균일성을 가지면서도 이동도 특성이 비교적 우수한 편(이동도 10~50cm2/Vs)이고, 특히 누설 전류가 매우 작기 때문에 대면적 SLM을 구성하기에는 유리할 것으로 생각된다. 또한 실리콘 계열 트랜지스터에서 흔히 발생하는 미세 채널 효과(short channel effect) 또한 거의 없는 것으로 알려져 있다.

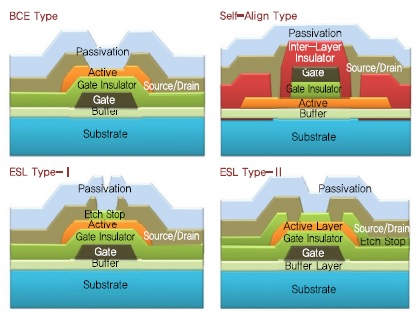

(그림 7)에서 표현된 것처럼 산화물 TFT는 다양한 소자구조로 제작이 가능한데, 가장 적은 면적을 구현하는 것은 백채널식각구조(BCE: Back channel etch)이다. ETRI에서는 Al-doped InZnSnO 층을 이용하여 BCE 구조를 개발하였다. 특히 Al-InZnSnO는 S/D 금속층의 습식 식각액에 대하여 선택비를 가지기 때문에 습식 식각 방식으로도 BCE 구조 형성이 가능하다. 채널층 최적화와 공정 최적화를 통하여 1µm이하의 채널 길이를 가지는 산화물 TFT를 제작하는 데 성공하였다. 좀더 미세한 채널을 형성하는 것은 건식 식각 방식이 유리하나 신뢰성 등 측면에서는 습식 식각 방식이 유리하여 좀더 최적화가 필요하다. 특히, 채널 길이가 작아질 때 작은 면적에 높은 파워가 집중되어 동작시 발열에 의한 특성 열화의 우려가 있어 이에 대한 추가적인 기술 개발이 필요하다.

3. 수직 채널 TFT 소자

기존의 산화물 TFT 구조로 1µm급 채널 길이를 가지는 TFT 구성은 가능하나, 1µm 피치 이하의 픽셀을 구현하기 위해서는 전체적으로 적은 면적을 차지하는 TFT 구조 개발이 필요하다. 채널을 기존의 수평 평면 방식이 아니라 수직 구조로 바꾸면 전체적으로 TFT가 차지하는 면적을 극단적으로 줄일 수 있다. 이러한 수직 채널 TFT는 비정질 실리콘 TFT나 폴리 실리콘 TFT, 유기 반도체 TFT에서 시도된 바가 있으나, 산화물 TFT의 경우에는 소자 구조가 단순하고, 다양한 방법으로 반도체 형성이 가능하여 상대적으로 수직 채널 TFT 형성에 유리한 측면이 있다. 특히 수직 부분에도 균일한 두께 증착이 가능한 원자층 증착법(ALD)과 같은 방법의 사용도 가능하여 우수한 특성의 수직 채널 TFT가 구현되었다. 향후에는 기존의 박막 증착 방법과 동일한 PECVD나 스퍼터 방법을 적용하여 수직 채널 TFT를 제작하는 방법이 개발될 것으로 예상된다.

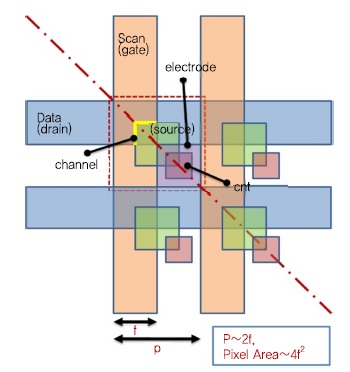

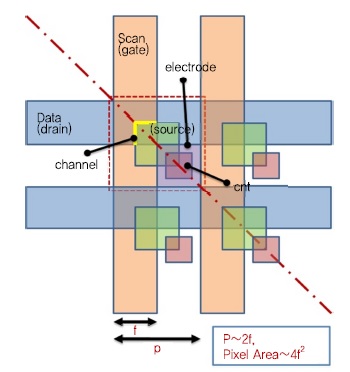

이렇게 수직 채널 TFT를 적용하면 (그림 8)과 같이 기준 피치를 F라 하면 4F2의 면적을 가진 단위 픽셀 구현이 가능하여, 0.5µm의 패턴 구현으로 1µm 픽셀 피치를 가지는 SLM패널 구현이 가능할 것으로 기대된다.

4. 미세 피치 액정 소자

앞서 설명한 바와 같이 픽셀 피치가 줄어듬에 따라 인접한 픽셀의 구동 전압이 구동 픽셀 내의 액정에 영향을 주게 된다. 이러한 현상을 극복하기 위해서는 인접한 픽셀의 구동 전극까지의 거리가 구동 픽셀내의 전극까지의 거리보다 충분히 크도록 픽셀 피치 대비 셀 갭의 높이를 낮출 필요가 있다. 그런데, 변조되는 광 특성이 광경로와 액정의 광변조 특성 계수(굴절율 변화 차이 Δn)의 곱에 비례하므로 광경로를 줄이기 위해서는 광변조 특성 계수가 큰 액정 소재를 사용하여야 한다. 그런데, 일반적으로 이렇게 광변조 특성 계수가 큰 액정의 경우 다른 특성 (안정성, 구동 전압, 구동 속도)에서 열화되는 경우가 많아 새로운 소자 개발이 필요하다. 현재는 Δn이 0.25근방인 소재를 사용하여 SLM 패널을 개발 중이다.

이러한 소재 개발 이외에도 물리적인 격벽의 형성을 통한 크로스톡의 감소나 상하 전극 구조가 아닌 평면 전극의 적용 등 픽셀 구조에 대한 연구도 필요할 것이다.

5. 모듈 방식 구동

현재까지 상용화된 패널의 최고 해상도는 8K×4K급이다. 그 이상의 해상도를 가지는 패널의 구동을 위해서는 더 높은 해상도를 지원하는 구동칩(게이트 드라이버, 데이터 드라이버, TCON등)의 개발이 필수적이다. 그런데, 이러한 구동칩의 개발도 패키징 부분에서의 물리적 한계(칩 본딩등) 때문에 제한을 가지고 있다. 따라서 기존의 COG, COF등 패널의 외곽부에 구동칩을 본딩하여 패널을 제어하는 방식은 1µm피치의 패드들을 통하여 100K이상의 데이터를 전달하는 것에 한계를 보인다.

최근 반도체 기술에서도 한계에 다다른 패턴 축소 기술의 한계를 극복하는 방법으로 고난이도의 패키징 기술을 이용한 반도체 디바이스의 성능향상이 제안되고 있다. 예를 들어 소니에서 개발한 Through Silicon Via(TSV)를 이용한 chip 본딩 기술의 경우 구동 회로부와 픽셀부를 별도로 만들어 접합하여 고해상도의 이미지 센서를 개발하였다.

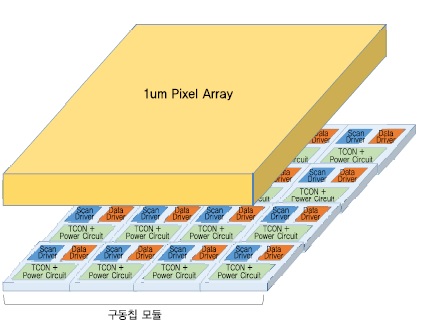

이러한 방법을 SLM에 적용할 경우 (그림 9)와 같이 적당한 크기의 모듈단위로 SLM을 개발한 이후에 이를 모듈연결 방식의 구동을 적용할 경우 비교적 크기의 제한이 없이 초고해상도의 SLM 패널 구동이 가능할 수 있을 것으로 생각된다.

Ⅳ. 대면적 초고해상도 SLM 응용 분야

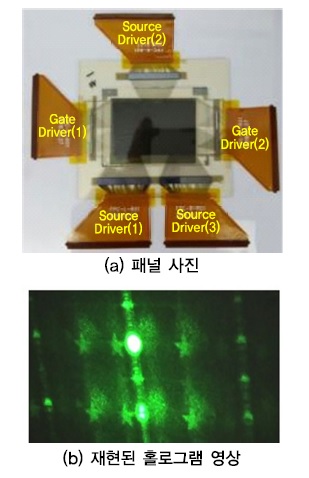

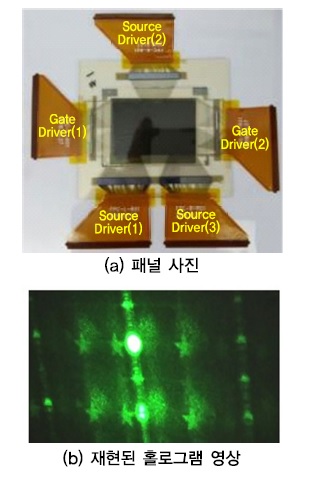

현재까지 SLMoG 기술로 7µm픽셀 피치의 5.8K 패널이 개발되어 홀로그램 영상 재현에 성공하였다[(그림 10) 참조].

대면적 초고해상도 SLM은 홀로그램 영상을 효과적으로 재현하기 위하여 개발하고 있는 디바이스이지만, 홀로그램 영상 재현이외에도 여러 분야에 응용이 가능하다.

먼저 초고해상도 디스플레이 패널 기술을 포함하고 있기 때문에 초고해상도를 요구하고 있는 광파 디스플레이나 집적 영상 디스플레이에 응용이 가능하며, 최근 이슈가 되고 있는 가상/증강 현실용 디스플레이로도 사용이 가능하다.

또한 픽셀 단위로 광의 변조가 가능한 특성을 이용하여 적응 광학(adaptive optics), 광학 영상(Optical Imaging), 광통신(Optical Communication)등 다양한 분야에 응용이 가능하다.

대면적 초고해상도 SLM은 디스플레이 패널 기술의 최첨단 기술로서 디스플레이 패널이 초정밀 능동 광학 소자로 사용될 수 있기에 지금까지 생각하지 못했던 많은 응용 분야 창출 또한 가능할 것으로 생각된다.

References

(그림 1)

픽셀피치 3.74μm GAEA SLM 모습<a href="#r006">[6]</a>

(그림 2)

MRAM 원리를 이용한 SLM

(그림 3)

삼성디스플레이가 SID2016에서 공개한 806ppi 5.5인치 4K AMOLED 디스플레이

(그림 4)

크로스톡의 발생 원인 모식도

(그림 5)

스티치 공정을 이용한 패턴 연결부

(그림 6)

믹스-앤-매치 방법으로 구성한 패널 노광 모식도

(그림 7)

산화물 TFT의 소자 구조

(그림 8)

수직채널 산화물 TFT를 이용한 픽셀 레이아웃

(그림 9)

모듈 연결 방식을 이용한 대용량 패널 구동 방식

(그림 10)

제작된 7μm 픽셀 피치의 SLMoG