실리콘-화합물 융합 반도체 소자 기술동향

Technical Trend of Fusion Semiconductor Devices Composed of Silicon and Compound Materials

- 저자

-

이상흥RF/전력부붐연구그룹 shl@etri.re.kr 장성재RF/전력부붐연구그룹 sjchang@etri.re.kr 임종원RF/전력부붐연구그룹 jwlim@etri.re.kr 백용순RF/전력부붐연구그룹 youngb@etri.re.kr

- 권호

- 32권 6호 (통권 168)

- 논문구분

- 4차 산업혁명 선도를 위한 ICT소재부품기술 특집

- 페이지

- 8-16

- 발행일자

- 2017.12.01

- DOI

- 10.22648/ETRI.2017.J.320602

본 저작물은 공공누리 제4유형: 출처표시 + 상업적이용금지 + 변경금지 조건에 따라 이용할 수 있습니다.

본 저작물은 공공누리 제4유형: 출처표시 + 상업적이용금지 + 변경금지 조건에 따라 이용할 수 있습니다.- 초록

- In this paper, we review studies attempting to triumph over the limitation of Si-based semiconductor technologies through a heterogeneous integration of high mobility compound semiconductors on a Si substrate, and the co-integration of electronic and/or optical devices. Many studies have been conducted on the heterogeneous integration of various materials to overcome the Si semiconductor performance and obtain multi-purpose functional devices. On the other hand, many research groups have invented device fusion technologies of electrical and optical devices on a Si substrate. They have co-integrated Si-based CMOS and InGaAs-based optical devices, and Ge-based electrical and optical devices. In addition, chip and wafer bonding techniques through TSV and TOV have been introduced for the co-integration of electrical and optical devices. Such intensive studies will continue to overcome the device-scaling limitation and short-channel effects of a MOS transistor that Si devices have faced using a heterogeneous integration of Si and a high mobility compound semiconductor on the same chip and/or wafer.

Share

Ⅰ. 서론

1958년 J. Kilby에 의해 집적회로가 개발된 후 실리콘 집적회로 기술은 빠르게 진보하여 왔으며, 이를 바탕으로 통신, 의료, 상업, 레저, 오락 등 사회 전반적인 영역에 적용되었다. 인텔사의 창시자 중 한 명인 고든 무어(Gordon Moore)는 반도체 소자의 집적도는 2년마다 2배씩 증가한다고 예측하였으며, 황창규(전 삼성전자)는 메모리 반도체의 집적도는 1년에 2배씩 증가한다고 예측하였다. 이러한 예측들은 지금까지는 상당한 정도로 정확히 지켜지고 있다.

휴대용 전자 기기의 발전은 마이크로파 또는 밀리미터파 대역의 고주파 소자, 아날로그와 디지털 신호를 동시에 처리할 수 있는 반도체 소자의 필요성을 증가시키고 있다. 특히, 스마트폰, 태블릿 컴퓨터와 같은 모바일/IoT(Internet of Things) 기기의 빠른 발전 및 확산은 반도체 칩의 크기 및 소모 전력의 감소, 높은 동작 주파수와 출력, 다양한 기능의 동시 집적을 요구하고 있다.

현재까지의 실리콘 반도체는 스케일링(Scaling) 즉, 게이트 길이와 게이트 절연막의 두께를 줄여 드레인 전류, 스위칭 속도, 집적도, 동작 주파수를 향상 시켜왔으며, 이는 반도체 메모리의 집적도 및 연산속도의 증가로 이어졌다. 소자의 동작을 위한 물리적인 최소 게이트 길이는 1.5nm이고[1] 소자를 구현하는 패터닝을 고려하면 3.23nm로 예상된다[2], [3]. 현재 실리콘 반도체 스케일링은 수 nm에 도달하여 한계에 직면하고 있다. 지속적인 산화막 두께 스케일링은 터널링에 의한 게이트 누설전류를 증가시키는데, 이를 개선하기 위하여 인텔에서는 high-k 물질을 45nm-노드 양산공정부터 적용하고 있다[4].

지속적인 게이트 길이 스케일링을 위해서 게이트에 의한 전계가 소소-드레인에 의한 전계의 영향을 받아 채널 전하의 흐름을 통제하는 기능을 상실케하는 단채널 효과(Short Channel Effects)를 억제하고 누설전류 증가를 막아야 하는데, 인텔과 삼성전자는 스케일링의 한계와 단채널 효과를 극복하기 위하여 3차원 구조의 FinFETs(Fin Field Effect Transistors)을 개발하여 양산에 적용하였다. 앞서 예는 실리콘 소자의 스케일링으로 인한 문제점을 실리콘 소자 관점에서 극복한 사례이다.

실리콘 소자의 스케일링으로 인한 문제점을 실리콘 소자 관점에서 극복하는 것과 달리, 고이동도(High Mobility)를 갖는 반도체를 사용하여 실리콘 소자의 스케일링으로 인한 문제점을 해결하려는 노력이 계속되고 있다. ITRS 로드맵 2.0(International Technology Road-map for Semiconductor 2.0[5])은 반도체 소자의 드레인 전류와 스위칭 속도를 더욱 높이기 위해서 전자와 정공의 이동도가 실리콘보다 높은 반도체 물질이 사용될 것으로 보고하였다. 즉, 실리콘 기판상에 고이동도 반도체인 갈륨비소(GaAs), 인듐비소(InAs), 인듐인(InP) 등과 같은 높은 전자 이동도를 가지는 Ⅲ-V족 화합물 반도체를 사용하여 nMOSFET(MOS Field-Effect Transistor)을 제작하고, 동일한 기판에 높은 정공 이동도를 가지는 IV족의 게르마늄(Ge)을 사용하여 pMOSFET을 제작하여 스케일링의 한계를 극복하고자 하는 것이다. 그뿐만 아니라, 화합물 반도체 소자는 밀리미터파 대역 및 테라헤르츠 응용 분야에 있어서 실리콘 반도체 소자보다 우수한 주파수 특성, 고이득, 저잡음 및 고출력 특성을 보인다.

실리콘 기판상의 고전하 이동도의 화합물 반도체를 사용하여 실리콘 소자의 한계를 극복하려는 노력뿐만 아니라, 실리콘 기판상에 화합물 전자소자와 광소자를 동시 구현하려는 노력도 계속되고 있다. 실리콘-화합물 반도체를 융합한 대표적인 소자로는 GaAs/Si, InP/Si 및 GaN/Si 등을 들 수 있으며, Ge/Si의 예도 있다.

실리콘-화합물 융합 반도체 소자 기술의 성공은 차지하고라도 궁극적으로 실리콘 기판상에 광소자와 전자소자가 동시 구현될 경우, SoC(System on Chip) 칩 내부, 칩과 칩 간의 신호를 전기배선(구리배선)이 아닌 광배선을 이용할 수 있으므로 신호를 더욱 빠르게 효율적으로 전송할 수 있다. 실리콘-화합물 융합 반도체 소자 기술은 궁극적으로 가능한 모든 기능을 하나의 칩에 집적하자는 것이며, 이로 인하여 소형화를 실현하고 제작 비용을 절감할 수 있다.

본고에서는 실리콘 기판상에서 Ⅲ-V족 화합물 반도체를 채널로 사용하여 전하 이동도를 높이거나(실리콘 기판상의 화합물 전자소자), 실리콘 기판상에 화합물 반도체를 사용하여 전자소자와 광소자를 동시 집적화하는 연구 동향에 대하여 알아보고자 한다.

Ⅱ. 실리콘-화합물 융합 반도체 소자 기술

1. 실리콘 기판 상의 화합물 전자소자 기술

이 절에서는 다양한 반도체 소자의 이종접합을 통하여 Si 소자가 직면한 스케일링 문제를 극복하고, 각 소자의 장점을 극대화한 전자소자에 대한 연구 동향을 살펴보고자 한다.

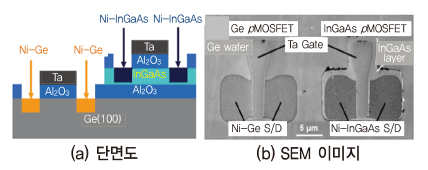

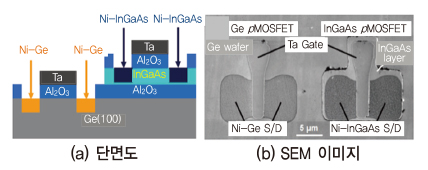

먼저, 웨이퍼 본딩을 통한 고전하 이동도 CMOS(Complemen-tary Metal-Oxide-Semiconductor) 구현방법은 다음과 같다. 실리콘 CMOS보다 빠른 스위칭 속도를 구현하기 위해서 실리콘의 전자, 정공 이동도보다 빠른 이동도를 가지는 물질을 사용하여야 한다. 이를 위하여 (그림 1)과 같이 InGaAs를 사용하여 nMOSFET를 구현하며, 동일한 웨이퍼 위에 Ge을 사용하여 pMOSFET을 제작한다. 그 이유는 InGaAs의 전자 이동도(<7,800cm2/Vs @ In contents=0.53 [6])와 Ge의 정공이동도(<1,900cm2/Vs)가 Si의 전자, 정공 이동도(1,350cm2/Vs, 480cm2/Vs) 보다 빠르기 때문이다.

InP 위에 성장된 InGaAs 웨이퍼와 Ge웨이퍼 위에 각각 Al2O3를 증착하고, 증착된 Al2O3 면을 접합시킨 후 InP를 제거하여 이종접합이 가능한 웨이퍼를 제작하며, InGaAs층과 Ge 기판을 사용하여 CMOS를 구현한다. 이렇게 제작된 CMOS는 실리콘 CMOS보다 빠른 스위칭 속도를 보이지만, nMOSFET과 pMOSFET의 높이가 달라 MOSFET 간의 전극 형성이 어렵고, 기생성분이 증가하며, 수율이 떨어지고, 집적도를 높이기 어렵다.

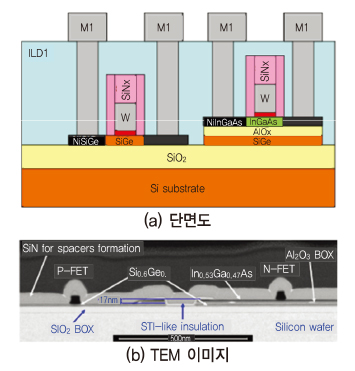

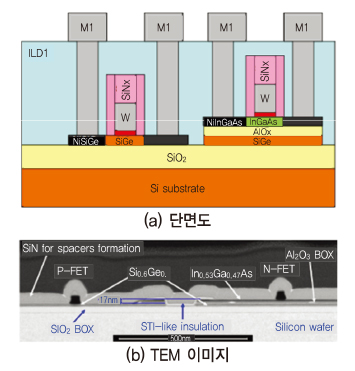

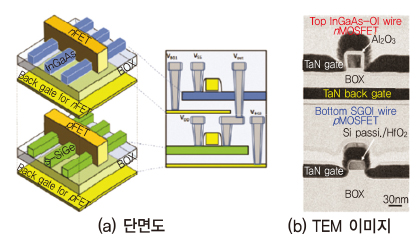

다음은 웨이퍼 본딩과 평탄화 기술을 통한 고전하 이동도 CMOS 구현 방법이다. (그림 2)는 (그림 1)에서 발생한 문제점들을 개선하기 위하여 SOI(Silicon on Insulator) 기술과 평탄화 기술을 적용하여 InGaAs와 SiGe을 이종접합한 예이다. SOI 기판상에 Ge을 증착하고 열처리를 통한 콘덴세이션 기법(Ge condensation: Si 상에 Ge을 증착하고 열처리를 하면 Ge이 Si으로 확산되어 들어가면서 SiGe이 형성되는 기법, 열처리 온도와 시간을 조절하여 SiGe의 Ge 농도를 조절할 수 있음)을 사용하여 SiGe층을 형성한다. InP 위에 InGaAs를 성장시키고, Al2O3를 증착 후 SiGe층 위에 접합시켜 이종접합 웨이퍼 형성한다. nMOSFET과 pMOSFET은 각각 InGaAs층과 SiGe층을 사용하여 제작된다.

(그림 1)의 방법에서 제기된 평탄화 문제를 해결하기 위하여 MOSFET 공정 후 유전체(Interlayer dielectric)를 증착하여 표면을 평탄화하고 패터닝(Patterning)을 통하여 전극을 연결하여 CMOS를 구현한다. 특히, FDSOI(Fully Depleted SOI) 구조를 적용하고, 매우 얇은 SiGe층(9nm)과 InGaAs층(6nm)을 사용하여 게이트 길이가 줄어들 때 발생하는 단채널 효과[9]를 최소화한다. 이 방식은 금속 전극과 유전체 사이에서 발생하는 기생성분으로 인한 스위칭 속도 저하와 집적도 저하가 초래된다.

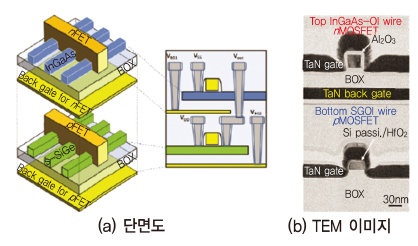

다음은 3차원 순차 집적 기술을 사용한 고전하 이동도 CMOS 구현방법으로, 집적도 개선을 위해 고안되었다[10]. 이 방식은 제일 아래층에 원하는 반도체 소자를 제작하고, 그 위에 다른 종류의 기판을 이종 접합시킨다. 2번째층에 반도체 소자를 제작하고, 리소그라피(Lithography) 공정을 통해 패터닝하여 첫 번째층과 두 번째층을 연결한다. 이를 계속적으로 반복하여 적층함으로써 하나의 칩에 다양한 종류의 반도체 소자를 접합시키고, 다양한 기능을 수행하도록 할 수 있다.

(그림 3)은 3차원 순차 접적 기술을 사용하여 SiGe pMOSFET과 InGaAs nMOSFET을 집적하여 CMOS를 구성한 단면도와 TEM 이미지이다. SOI 기판과 Ge 콘덴세이션 기법을 사용하여 SiGe층을 형성한다. SiGe층에 나노와이어(Nano-wire) 구조의 pMOSFET을 제작하고, 그 위에 SiO2층을 증착한 뒤 CMP(Chemical Mechanical Polishing)를 통해 평탄화한다. TaN과 SiO2를 순차적으로 증착한다. 이때 증착된 TaN은 InGaAs nMOSFET의 백게이트(Back-gate)로 동작하여 소자의 동작 성능을 조절하는데 사용된다. SiO2 위 InP에 성장된 InGaAs층을 접합하고 에칭을 통해 InP를 제거한다. InGaAs층을 사용하여 나노와이어 구조의 nMOSFET을 제작하고, 리소그라피 공정과 금속 증착을 통하여 pMOSFET과 nMOSFET을 연결하여 CMOS를 제작한다.

3차원 순차 집적 기술은 매우 얇은 반도체층을 사용한다. 이 기술은 각층을 연결하는 금속 패턴을 리소그라피를 통해서 형성하는 것이 가장 큰 특징이다. 이 방법을 통하여 기존의 웨이퍼 본딩 기술보다 높은 집적도(>108/mm2)와 좁은 피치(Pitch)(<100nm)를 획득하는 것이 가능하다[12]. 또한, 백게이트 구조를 적용한 커플링 효과(Coupling Effect)[13]에 의해 문턱 전압(Threshold Voltage)을 조절할 수 있으며, 이를 이용하여 휴대용 전자기기의 대기 모드에서의 소모 전력을 감소시킬 수 있다. 이러한 장점에도 불구하고, 이 방법은 아래층에 제작된 반도체 소자가 성능 저하 없이 견딜 수 있는 온도(Thermal Budget)보다 낮은 온도에서 상층의 반도체 소자를 제작하여야 하므로 적절한 저온 공정 기술의 개발이 필요하다.

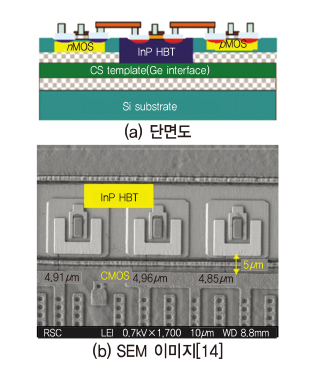

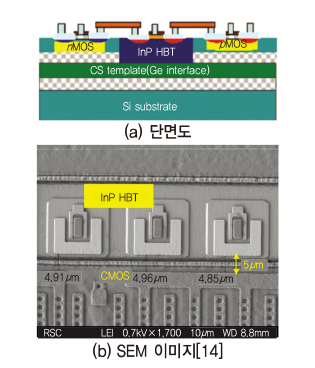

다음은 고주파 동작과 아날로그와 디지털 신호를 동시에 처리하기 위한 소자 기술에 관한 것으로, 에피 성장을 통한 InP HBT(Heterojection Bipolar Transistor)와 Si CMOS 이종접합 구현방법이다. (그림 4)는 InP HBT와 Si CMOS를 이종접합한 것으로, Ge층이 삽입된 유사 SOI 구조가 사용된다. Si 기판에 CMOS가 제작되고, Si CMOS 기술을 사용하여 InP가 성장될 영역이 패터닝 및 Ge층까지 에칭된다. InP 에피층이 선택적으로 성장되고, 그 위에 HBT가 제작되며, 마지막으로 Si CMOS 소자와 InP HBT가 금속으로 연결된다.

Ge은 Si CMOS 공정에 사용되는 물질이며, 격자 상수가 InP 성장에 필요한 버퍼층으로 사용되는 GaAs와 매우 유사하여 고품질의 GaAs 버퍼층을 성장시키는 것이 가능하기 때문에 선택된다. 또한, InP HBT는 Si 소자의 게이트 길이 감소에 따른 낮은 전류 붕괴 전압(Breakdown Voltage)을 보완하고, 빠른 전자 이동도를 이용한 높은 스위칭 속도를 얻기 위하여 적용된다. 이 방법은 Ge과 버퍼층의 계면에서 발생하는 격자 결함이 버퍼층을 통해서 에피층까지 전달되는데 이는 InP 기판을 사용하여 HBT를 제작하는 경우와 비교하였을 때 소자의 성능과 신뢰성의 저하를 야기한다. 버퍼층의 두께를 증가시키는 방법을 사용하여 에피층으로 전파되는 격자 결함을 줄일 수 있으나, 이는 고주파 동작시의 방열 특성을 저하시킨다. 또한, Si CMOS와 InP HBT의 연결에 사용되는 전극의 길이와 기생 성분을 최소화하기 위해서 CMOS가 제작되는 Si 기판의 높이와 InP 에피층의 높이가 동일하도록 하는데, 이는 InP의 격자 결함을 제한하는 또 다른 제약사항으로 작용한다.

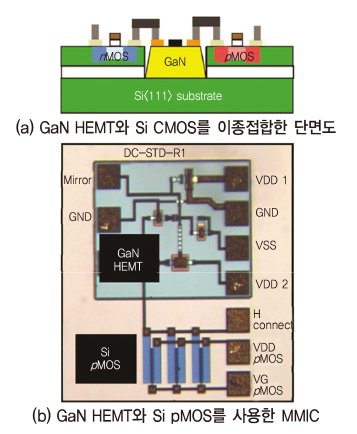

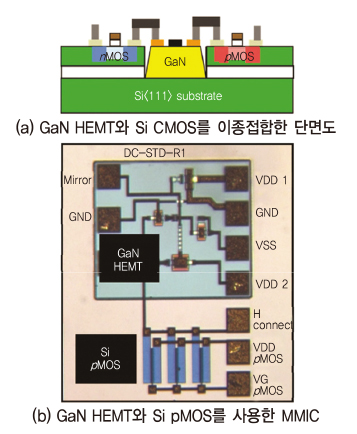

다음은 에피 성장을 통한 GaN HEMT와 Si CMOS 이종접합 구현방법이다. (그림 5)는 Si MOSFET과 GaN HEMT(High-Electron-Mobility Transistor)가 하나의 기판에 집적된 예이다. 기판은 SOI 기판이 사용되며, 일반적인 Si <100> 기판이 아닌 고저항 <111> 기판이 사용되는데, GaN와의 격자 상수의 차이로 인하여 <111> 기판에서만 GaN을 성장시킬 수 있기 때문이다. Si MOSFET이 제작되는 Si 박막은 <100>가 사용된다. Si MOSFET을 제작하고, GaN을 성장시킬 영역을 Si <111> 기판까지 선택적으로 에칭한 후 GaN을 성장시키고 HEMT 소자를 제작한다. 마지막으로 GaN HEMT 소자와 Si MOSFET을 금속 전극을 사용하여 연결한다.

(그림 5b)는 GaN HEMT를 포함한 간단한 전력 증폭기 MMIC(Microwave Monolithic Integrated Circuit) 이다. GaN HEMT, GaN 다이오드, Si pMOSFET으로 구성되었으며, GaN HEMT는 전력 증폭, GaN 다이오드는 레벨 변환(Level Shifting) 그리고 Si pMOSFET은 전류원으로 사용되었다.

이 방법은 (그림 4)의 InP HBT를 사용한 경우와 비교하여 쉽게 기판을 제작할 수 있으며, GaN HEMT의 빠른 스위칭 속도, 높은 전류 붕괴 전압, 고주파 동작시의 높은 출력과 같은 GaN HEMT의 장점을 활용할 수 있다. 이러한 장점에도 불구하고 이 방법은 버퍼층과 GaN층에 인가되는 스트레스와 웨이퍼의 휨을 최소화하기 위해서 Nucleation층과 버퍼층을 최적화하여야 하며, Si과 GaN 계면에서 Si에 의한 GaN의 도핑(Doping)을 최소화하여야 한다. 또한, GaN층의 높은 성장 온도에 의한 Si MOSFET의 성능 저하를 최소화하여야 하며, GaN층의 높이는 Si 박막의 높이와 동일하게 하여야 한다.

앞으로의 전자소자는 모바일/IoT 기기의 발전에 따라 낮은 전력 소모, 소자 크기의 축소, 성능의 향상, 다양한 기능의 동시 집적이 요구될 것이며, 이들의 요구에 부응하여 Ⅲ-V 기반의 서로 다른 물질을 Si 반도체 기술과 함께 이종접합한 소자 구조와 공정기술의 개발은 지속될 것으로 사료된다. 이러한 이종접합을 사용한 소자 및 공정 기술은 반도체 설계에 있어서 고주파 동작, 고집적 회로, 아날로그와 디지털 신호의 동시 처리, 다기능의 집적화를 가능하게 한다.

2. 실리콘-화합물 융합 전자소자 및 광소자 집적 기술

이 절에서는 실리콘-화합물 융합의 전자소자 및 광소자 동시 집적에 관한 연구 동향을 살펴보고자 한다. 먼저, 실리콘 기판상에 전자소자와 광소자를 동시 구현한 살펴보고, 다음으로 서로 다른 기판에서 전자소자와 광소자를 각각 구현한 후 집적화하는 방법에 대하여 살펴본다.

앞서 설명한 바와 같이, 실리콘 기판상에 이종의(Heterogeneous) 반도체 융합 소자는 대표적으로 실리콘 기판 상의 갈륨비소(GaAs/Si), 실리콘 기판 상의 인듐인(InP/Si), 실리콘 기판 상의 질화갈륨(GaN/Si), 길리콘 기판 상의 게르마늄(Ge/Si)을 들 수 있다. 이들 이종의 융합 반도체 소자는 재료들 간의 격자상수 차이로 재료들 계면에 완충층을 삽입하여 응력에 의한 변형을 조절하는데, 여기에 사용되는 재료로는 CoSi, NiSi, FeSi2 등이 있다[16]. 다음은 실리콘 기판 상에 이종의 융합 반도체 소자 구현 예이다.

먼저, 실리콘 기판상의 갈륨비소(GaAs/Si) 소자를 구현하는 방법이다. 일반적으로 실리콘 기판상에 갈륨비소를 직접 성장하게 되면 격자상수 불일치(4%)로 인하여 성장하고 냉각하는 동안 크랙(Crack)이나 전위(Dis-location)가 발생한다. 따라서, 실리콘 기판상의 갈륨비소(GaAs/Si)는 실리콘 기판상에 갈륨비소를 직접 성장하지 않고 실리콘 위에 STO(SrTiO2)를 수 원자층으로 성장한 후, 갈륨비소를 성장한다. 해외 일부 업체 중심으로 실리콘 기판상의 갈륨비소 발광다이오드(LED: Light Emitting Diode)와 RF(Radio Frequency) 전자소자를 개발하여 실리콘-화합물 융합의 광소자와 전자소자를 구현하였다.

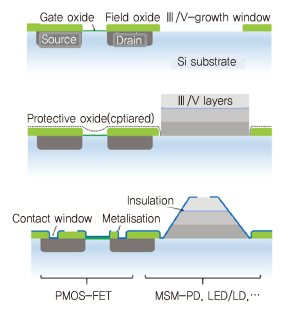

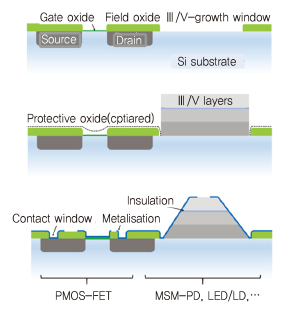

다음은 실리콘 기판상의 인듐갈륨비소(InGaAs/Si) 소자를 구현한 예이다. (그림 6)은 실리콘 기판상에 CMOS 공정 후, 인듐갈륨비소인(InGaAsP)을 선택적으로 성장하여 1.3μm, 1.55μm의 금속-반도체-금속 광검출기(MSM-PD: Metal-Semiconductor-Metal Photo-detector), 발광다아오드, 레이저 다이오드(Laser Diode)를 구현한 것으로[17], 실리콘 기판상에 CMOS 전자소자와 인듐갈륨비소인(InGaAsP) 기반의 광소자를 동시 집적한 예이다.

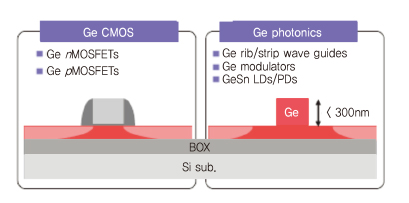

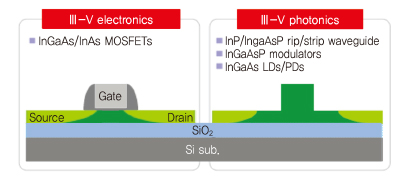

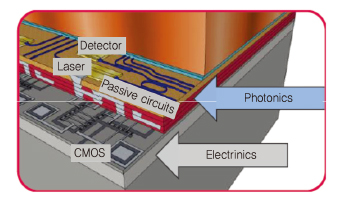

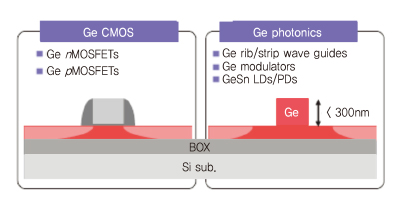

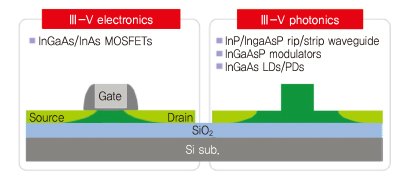

일본 도쿄대학에서는 실리콘 기판상에 게르마늄 CMOS 전자소자와 게르마늄 광소자를 동시에 집적화하는 연구와 실리콘 기판상에 Ⅲ-V 전자소자와 Ⅲ-V 광소자를 동시에 집적화하는 연구를 하고 있다. (그림 7)과 같이, 실리콘 기판에 GeOI(Ge-on-Insulator) 기판을 제작하여, 고전하 이동도를 갖는 게르마늄 CMOS와 게르마늄 기반의 레이저 다이오드(LD), 광검출기(PD), 변조기, 도파로 등 광소자를 집적하여 (그림 7) 실리콘-화합물 융합 전자소자 및 광소자 집적기술을 개발 중에 있다. 뿐만 아니라, (그림 8)과 같이 실리콘 기판에 III-V 전자소자인 고성능 인듐갈륨비소(InGaAs) MOS 트랜지스터와 인듐갈륨비소인(InGaAsP) 기반의 레이저 다이오드(LD), 광검출기(PD), 변조기, 도파로 등 광소자를 집적하여 (그림 8) 실리콘-화합물 융합 전자소자 및 광소자 집적기술을 개발 중에 있다[18].

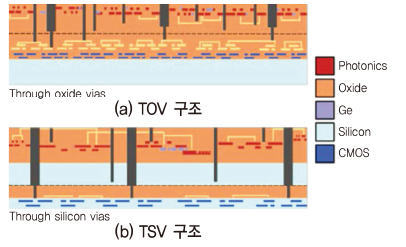

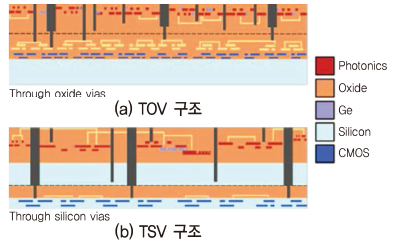

다음은 각기 다른 기판에서 제작된 전자소자와 광소자 본딩을 통하여 실리콘-화합물 융합 전자소자 및 광소자 집적화 방법들이다. (그림 9b)는 미국 UC 버클리팀이 개발한 방법으로, 조밀한 패키지를 위한 TSV(Through Silicon Via) 방법이다. 즉, 아래의 전자소자 칩과 위의 광소자 칩을 본딩하고 실리콘 비아(Silicon via)를 통하여 두 칩을 연결하는 것이다. (그림 9a)는 미국 MIT 팀이 개발한 방법으로, TOV(Through Oxide Via) 방법이다. 즉, 전자소자 웨이퍼와 광소자 웨이퍼를 다이싱하기 전에 산화막을 형성한 후 본딩하고 산화막 비아(Oxide Via)를 통하여 두 웨이퍼를 연결하는 방법이다. (그림 9)에서와 같이 전자소자와 광소자가 두꺼운 실리콘 비아를 통하여 연결되는 TSV 방법보다 TOV 방법이 더 낮은 기생 정전용량을 갖는다. TOV 방법의 기생 정전용량은 TSV 접근법의 기생 정전용량 30fF 보다 휠씬 적은 1.45fF을 갖는 것으로 보고되었다. 이와 같이 전자소자와 광소자 인터커넥션시 기생 정전용량을 낮추는 것은 전력소모를 적게 하고 고속 동작을 가능케 한다. TSV 방법은 250fJ/bit를 소모하는 5Gb/s 링크에 사용되는 온-칩 광 송신 및 수신 모듈을 가능케 한다[20].

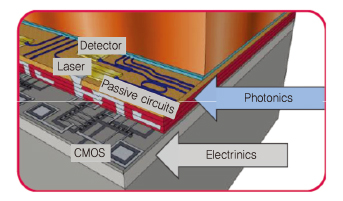

네덜란드 아인트호벤 대학에서는 실리콘 칩 위에 얇은 InP-막(IMOS: InP-Membrane On Silicon)을 사용하여 CMOS와 광소자를 집적하였는데, 여기서 IMOS는 실리콘 도파로와의 광결합을 막아주는 역할을 한다. InP 얇은 막이 실리콘 전자 칩 위에 폴리머로 본딩되며, 얇은 광층은 능동소자(레이저, 검출기, 변조기)와 수동소자(도파로, 필터, 결합기, 디멀티플렉서)를 포함한다. 전자층과 광층 사이에는 전기적 접촉(Contact)을 통하여 전자소자와 광소자가 연결된다.

실리콘 기판상에 광소자와 전자소자 동시 집적화는 SoC(System on Chip) 칩 내부, 칩과 칩 간의 신호를 전송 시 전기배선의 단점을 극복하고 광배선을 이용할 수 있으므로 기술적 어려움에도 불구하고 연구자들에게 큰 매력이 되고 있다.

Ⅲ. 결론

본고에서는 실리콘 기판상에서 고전하 이동도의 화합물반도체를 사용하여 실리콘 소자의 한계를 극복하는 연구 동향과 실리콘 기판상에서 전자소자와 광소자의 융합 연구 동향에 대하여 살펴보았다. 실리콘 기판상에 고전하 이동도의 화합물반도체를 사용하여 실리콘 전자 소자의 성능을 능가함과 동시에 다양한 기능을 할 수 있는 전자 소자를 개발하는 방향으로 연구가 진행되고 있다. 뿐만 아니라 실리콘 기판 전자소자와 광소자 융합은 크게 실리콘 기판상에 CMOS 전자소자와 인듐갈륨비소(InGaAs) 계열의 광소자 집적, 실리콘 기판을 이용한 게르마늄 CMOS 전자소자와 게르마늄 광소자 집적의 연구가 활발하며, 전자소자와 광소자 웨이퍼나 칩의 본딩을 통한 TSV나 TOV 연구가 활발하다.

앞서 살펴본 바와 같이 실리콘 소자의 스케일링 한계와 단채널 효과를 극복하기 위한 3차원 구조의 FinFET(Fin Field-Effect Transistor) 등 구조 개선 노력과 실리콘 기판상에서 고이동도(High mobility)를 갖는 실리콘-화합물 융합 반도체 연구, 반도체 칩간 고속데이터 전송을 위한 실리콘/화합물 융합 전자소자 및 광소자 집적 연구는 앞으로도 지속될 것으로 판단된다.

약어 정리

CMOS

Complementary Metal-Oxide-Semiconductor

CMP

Chemical Mechanical Polishing

FinFET

Fin Field Effect Transistor

GeOI

Ge-on-Insulator

HBT

Heterojection Bipolar Transistor

HEMT

High-Electron-Mobility Transistor

IoT

Internet of Things

LED

Light Emitting Diode

MMIC

Microwave Monolithic Integrated Circuit

MOSFET

MOS Field-Effect Transistor

MSM-PD

Metal-Semiconductor-Metal Photo-detector

RF

radio frequenc

SoC

System on Chip

TOV

Thtough Oxide Via

TSV

Through Silicon Via

V.V. Zhirnov, R.K. Cavin, J.A. Hutchby, and G.I. Bourianoff, “Limits to Binary Logic Switch Scaling - a Gedanken Model,” Proc. IEEE, vol. 91, no. 11, Nov. 2003, pp. 1934-1939.

K. Kim, “Silicon Technologies and Solutions for the Data-Driven World,” IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig., San Francisco, CA, USA, Feb. 22-26, 2015, pp. 1-7.

T.P. Pearsall and J.P. Hirtz, “The Carrier Molbilities in Ga0.47In0.53As Grown by Organo-Metallic CVD and Liquid-Phase Epitaxy,” J. Cryst. Growth, vol. 54, no. 1, 1981, pp. 127?131.

H. Yokoyama et al., “CMOS Integration of InGaAs nMOSFETs and Ge pMOSFETs with Self-Align Ni-Based Metal S/D Using Direct Wafer Bonding,” Symp. VLSI Technol., Honolulu, HI, USA, 2011, pp. 60-61.

L. Czornomaz et al., “Co-integration of InGaAs n- and SiGe p-MOSFETs into Digital CMOS Circuits Using Hybrid Dual-channel ETXOI Substrates,” IEEE Int. Electron Dev. Meeting, Washington, DC, USA, 2013, pp. 2.8.1?2.8.4.

S. Cristoloveanu and S. Li, Electrical Characterization of Silicon-on-Insulator Materials and Devices, Boston, MA, USA: Kluwer Academic Publisher, 1995.

P. Batude, S. Sklenard, C. Xu, B. Previtali, B. De Salvo, and M. Vinet, “Low Temperature FDSOI Devices, a Key Enabling Technology for 3D Sequential Integration,” Int. Symp. VLSI Technol., Syst. Applicat., Hsinchu, Taiwan, Apr. 22-24, 2013, pp. 1-4.

T. Irisawa et al., “Demonstration of Ultimate CMOS Based on 3D Stacked InGaAs-OI/SGOI Wire Channel MOSFETs with Inde-pendent Back Gate,” Symp. VLSI Technol.: Dig. Techn. Papers, Honolulu, HI, USA, June 9?12, 2014, pp. 1?2.

P. Batude, “3D Sequential Integration: an Alternative Path towards CMOS Scalability,” Semicond. Interface Specialists Conf., San Diego, CA, USA, Dec. 10-13, 2014.

H.-K. Lim and J.G. Fossum, “Threshold Voltage of Thin-Film Silicon-on-Insulator (SOI) MOSFETs,” IEEE Trans. Electron Dev., vol. 30, no. 10, 1983, pp. 1244-1251.

D.S. Green, C.L. Dohrman, J. Demmin, Y. Zheng, and T.-H. Chang, “A Revolution on the Horizon from DARPA,” IEEE Microw. Mag., vol. 18, no. 2, 2017, pp. 44-59.

T.E. Kazior, “Beyond CMOS: Heterogeneous Integration of III-V Devices, RF MEMS and other Dissimilar Materials/Devices with Si CMOS to Create Intelligent Microsystems,” Philos Trans. Royal. Soc. A., vol. 372, no. 2012, Feb. 2014, pp. 1?13.

E.G. Moroni, R. Podloucky, and J. Hafner, “Supersoft Transition Metal Silicides,” Phys. Rev. Lett., vol. 81, no. 9, Aug. 1998, pp. 1969-1972.

D. Fehly, A. Schlachetzki, A.S. Bakin, A. Guttzeit, and H.-H. Wehmann, “Monolithic InGaAsP Optoelectronic Devices With Silicon Electronics,” IEEE J. Quantum Electron., vol. 37, no. 10, Oct. 2001, pp. 1246-1252.

M. Takenaka and S. Takagi, “Si/III-V CMOS Photonics for Low-Power Electronic-Photonic Integrated Circuits on Si Platform,” Conf. Lasers Electro-Opt., San Jose, CA, USA, June 5?10, 2016, pp. 1?2.

N.D. Heidel, N.G. Usechak, C.L. Dohrman, and J.A. Conway, “A Review of Electronic-Photonic Heterogeneous Integration at DARPA,” IEEE J. Select. Topics Quantum Electron., vol. 22, no. 6, Nov./Dec. 2016.

- Sign Up

- 전자통신동향분석 이메일 전자저널 구독을 원하시는 경우 정확한 이메일 주소를 입력하시기 바랍니다.