4차 산업 혁명의 숨은 혁신 기술: 전자 패키징 기술

Hidden Innovations in the Fourth Industrial Revolution: Electronic Packaging Technology

- 저자

-

최광성ICT소재연구그룹 kschoi@etri.re.kr 문석환ICT소재연구그룹 shmoon@etri.re.kr 배현철ICT소재연구그룹 hcbae@etri.re.kr 장건수ICT소재연구그룹 ksjang4444@etri.re.kr 엄용성ICT소재연구그룹 yseom@etri.re.kr

- 권호

- 32권 6호 (통권 168)

- 논문구분

- 4차 산업혁명 선도를 위한 ICT소재부품기술 특집

- 페이지

- 17-26

- 발행일자

- 2017.12.01

- DOI

- 10.22648/ETRI.2017.J.320603

본 저작물은 공공누리 제4유형: 출처표시 + 상업적이용금지 + 변경금지 조건에 따라 이용할 수 있습니다.

본 저작물은 공공누리 제4유형: 출처표시 + 상업적이용금지 + 변경금지 조건에 따라 이용할 수 있습니다.- 초록

- Electronic packaging technology is a technology that easily connects devices to the outside. The fourth industrial revolution is thought to be possible with the advancement of certain devices. The advancement of these devices must be accompanied by innovations in electronic packaging that connects the devices to the outside world, allowing their performances to be implemented at the system level. In this paper, the development trends of 2.5D/3D technology, heterogeneous integration technology, ultrafine interconnection technology, and heat dissipation technology will be examined, and the development direction of these technologies will be discussed.

Share

Ⅰ. 서론: 4차 산업혁명과 전자 패키징 기술의 연관성

4차 산업혁명 개념에 대해 여러 가지 논의가 분분하다. 새로운 개념이 떠오를 때 이해를 돕는 손쉬운 방법 중 하나가 키워드 분석이다. 4차 산업혁명과 관련하여 키워드 분석 결과를 살펴보면 빅데이터, IoT(Internet of things), 인공지능, 드론, 3D 프린터, 가상현실, 증강현실, 뇌 과학 등으로 보고되었다[1]. 최근에 전자 패키징 기술 분야에서 주로 언급되는 키워드를 살펴보면 대용량(High Bandwidth), 방열, 이종 집적(Heterogeneous Integration), 2.5D/3D 집적, TSV(Through Silicon Via), Fan-out packages 등이다[2]. 이러한 기술적 키워드는 모두 앞서 언급된 4차 산업혁명의 주요 키워드를 구현하는데 사용되는 핵심 기술들이다.

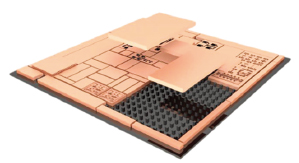

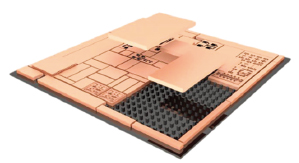

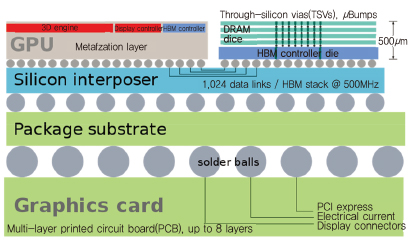

일반적으로 메모리 버스는 전체 시스템 성능을 좌우하는 것으로 알려져 있다[3]. 예전의 컴퓨터들은 메모리 버스의 속도에 프로세서가 동작하도록 설계되었다. 그러나 최근에는 프로세서가 메모리 속도 보다 몇 배 빠르게 동작하도록 설계되고 있고, 이에 따라 프로세서가 메모리로부터 정보를 기다려야 하는 지경에 이르렀다. 이러한 문제를 해결하기 위해 DDR(Double Data Rate) 이나 GDDR(Graphics Double Data Rate)은 핀당 대역폭을 늘리는 방법을 사용하였다[4]. 그러나 이러한 방법은 열 발생을 늘린다는 점에서 제한적이었다. 이러한 문제점을 해결하기 위해 최근에 HBM(High Bandwidth Memory) 솔루션이 제안되어 인공지능을 비롯한 고급 서버 시스템에 적용되고 있을 뿐만 아니라 차기 스마트패드에서도 적용될 예정이다[5], [6]. AMD사는 SK하이닉스사와 함께 Fiji GPU(Graphics Processing Unit) 모듈을 개발하였고 Vega를 2017년에 양산을 예정이며, NVIDIA사는 Tesla P100을 양산하고 있다[7]. (그림 1)은 HBM을 적용한 GPU 메모리 모듈 단면도를 보여준다[8].

(그림 1)

HBM을 적용한 GPU 메모리 모듈 단면도[8]

[출처] Shmuel Csaba Otto Traian [CC BY-SA 4.0(https:// creativecom-mons.org/licenses/by-sa/4.0) or GFDL (http:// www.gnu.org/copyleft/fdl.html)], via Wikimedia Commons.

GPU 메모리 모듈의 가장 큰 특징은 GPU와 HBM 사이에 1,024개의 데이터 링크가 적용되었다는 점이다. 이러한 고밀도 배선은 일반적인 유기 패키지 기판으로 구현이 불가하기 때문에 실리콘 인터포저가 적용되었다. 이렇게 다채널을 제공하는 HBM 인터페이스의 장점으로 인해 핀당 1Gbps의 속도로도 총 128GB/s의 대역폭을 확보할 수 있다. HBM2의 경우 핀당 2Gbps 속도를 제공하여 총 256GB/s의 대역폭을 제공한다. TSV의 낮은 기생 캐패시턴스로 인해 이러한 넓은 대역폭을 제공함에도 전력 소모는 낮다.

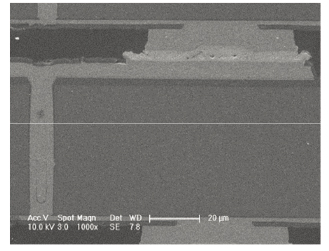

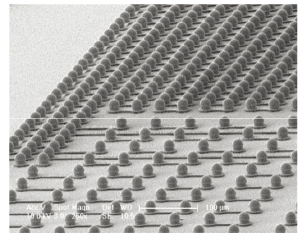

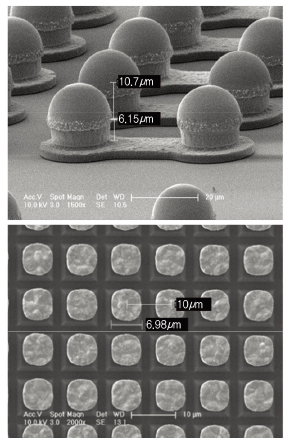

HBM과 실리콘 인터포저는 (그림 2)에서 보이는 바와 같이 TSV 기술을 적용하여 구현되었다. HBM 내 메모리 칩의 접합 그리고 HBM과 실리콘 인터포저의 접합은 모두 (그림 3)에서 보인 바와 같이 40~50μm 피치의 구리 필러 위의 솔더 범프를 형성하여 이를 아래 칩 상의 UBM(Under Bump Metallization)과 접합 공정을 수행하여 얻어진다. 이러한 솔더 범프의 개수는 약 1만 개에 다다른다. 이러한 미세 피치 접합은 인공지능용 프로세서 모듈에 국한되는 것이 아니다. VR(Virtual Reality)·AR(Augmented Reality)용 핵심 디스플레이로 떠 오르고 있는 마이크로 LED의 접합을 위해서 10μm 피치의 솔더 범프가 개발되고 있다[9].

(그림 1)의 GPU 메모리 모듈을 보면 다양한 이종 디바이스들이 하나의 패키지 안에 구현되어 시스템의 성능을 규정짓고 있음을 알 수 있다. 이와 같은 기술 개발로 인하여 지난 20년간 반도체 산업의 기술 로드 맵으로 사용되었던 ITRS(International Technology Road-map for Semiconductor)가 종언을 고했다. 이는 무어의 법칙이 그 한계에 다다랐기 때문이다. 그에 대한 대안으로 스마트 폰과 마이크로 서버에 근간을 둔 시스템 수준의 요구사항에 따른, 이종 집적에 방점을 찍은 ITRS 2.0이 시작되었다[10].

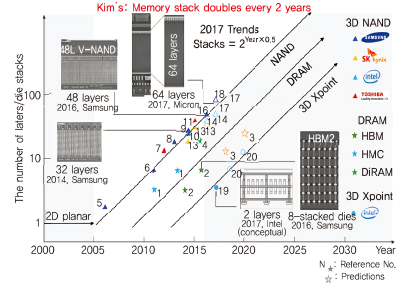

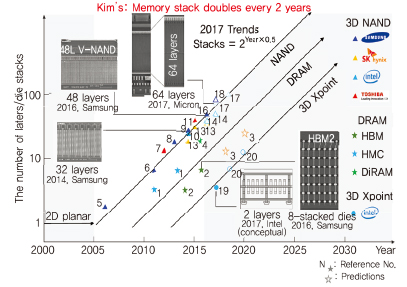

KAIST 김정호 교수는 무어의 법칙 대신 앞으로 2년마다 수직으로 적층되는 메모리 칩 또는 셀의 층수가 2배가 될 것으로 예측하였다. 이를 ‘Kim’s Law’로 명명하였고 이를 통해 미래의 반도체 개발 방향을 제시하였다[(그림 4) 참조]. 이 법칙은 주로 DRAM(Dynamic Random-Access Memory) 칩 및 NAND(Negative-AND) 플래시 메모리 셀이 적층되는 법칙이다. 미래의 NAND 플래시 메모리의 경우 셀과 칩의 적층이 동시에 일어날 것으로 예측되었고 2020년경에는 NAND Flask 셀의 적층이 100층을 넘어가고, DRAM 칩의 적층이 16층 이상이 될 것으로 예측하였다. 이러한 3차원 적층 과정을 통해서 메모리의 중요한 성능인 대역폭을 증가시키고, 신호 지연을 최소화하면서, 사용 전력도 극소화할 수 있다. 이러한 성능은 특히 4차 산업혁명을 맞이하여 빅데이터 센터와 클라우드 컴퓨터가 확장 보급되면서 더욱 중요한 성능이 된다. 4차 산업혁명 시대에 Kim’s Law는 미래 반도체 발전 방향을 제시한 법칙이라고 생각된다[11].

이러한 2.5D 및 3D 집적을 통한 이종 집적의 상용화는 패키지 공정 기술의 혁신이 뒷받침되어서 가능해졌으며 관련 기술을 지속적으로 국산화, 고도화하는 것이 필요하다. 또한, 고집적에 필연적으로 수반되는 발열 문제를 효과적으로 제어하는 방열 기술이 필수적이다. 일례로 HBM2가 1.2TB/s의 큰 대역폭을 GPU에 제공하지만 이로 인해 60W의 전력을 더 필요로 한다. 2.5TB/s을 요구하는 경우 120W가 필요하고 3TB/s의 대역폭은 160W를 메모리에만 필요하다고 한다[12]. 이러한 문제를 해결해야 GPU 모듈을 고성능 서버뿐만 아니라 일반 소비자들도 사용할 수 있게 된다. 전력 문제뿐만 아니라 이로 인해 발생하는 방열 문제의 효과적인 대처가 필요함을 알 수 있다.

이종 접합 기술의 장점은 앞서 언급한 대로 무어의 법칙 한계로 인해 더욱 부각되고 있으며, 그에 따라 민수용 기술 개발뿐만 아니라 군수용에서도 그 장점이 인식되고 있다. 최근 DARPA는 CHIPS(Common Heterogeneous Integration and IP Reuse Strategies) 프로그램을 발표하였다[13]. CMOS(Complementary Metal Oxide Semiconductor) 설계 및 공정 비용이 급상승함에 따라 군수용으로도 더 이상 매력을 잃어가고 있고 개별 모듈 구조로 즉, IP(Intellectual Property)를 재사용하는 것이 효율적임이 프로그램 시작의 배경임을 설명하였다[(그림 5) 참조].

Ⅱ. 본론: 전자 패키징의 혁신 기술

1. 접합 공정 기술

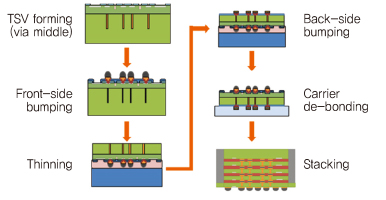

(그림 6)은 HBM의 패키징 공정도를 보여준다[14]. Via middle 공정으로 메모리 셀을 만든 후 TSV를 형성하고 BEOL(Back End of Line)과 솔더 범프를 만든다. 그 이후 Temporary bonding 공정을 수행하고 그라인딩 공정 등을 수행하여 TSV를 노출시키고 후면 재배선 공정을 수행한다. 마지막으로 Debonding 공정을 수행한 다음 Chip-to-wafer bonding 공정을 수행하여 적층된 칩을 제조한다. 상용화에 있어서 상기 공정의 가장 큰 문제는 적층 공정이다.

(그림 7)은 HBM에 적용되는 솔더 범프 및 마이크로 LED 접합 공정에 적용되는 솔더 범프 사진을 보여준다. 각각 범프 피치가 40μm와 10μm이다. 이와 같은 초미세 범프를 접합시키는 공정에 일반적인 리플로우 공정을 적용할 수 없다. 이는 피치가 조밀하고 칩이나 기판의 휨(Warpage) 현상 때문에 리플로우 공정 중에 단선 및 단락과 같은 불량이 발생할 우려가 매우 높기 때문이다.

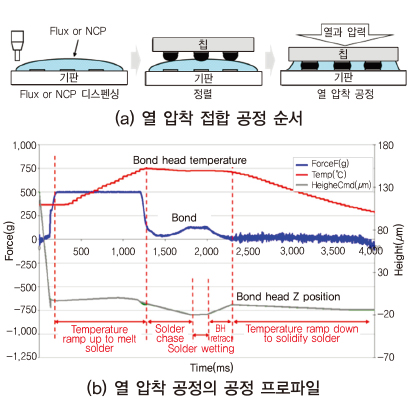

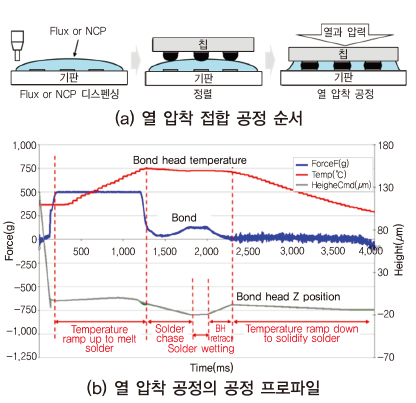

이와 같은 문제점을 해결하기 위한 열 압착 접합 공정이 (그림 8a)와 같이 개발되고 있다. 즉, 접합하고자 하는 개별 칩을 하나씩 기판이나 칩 상에 접합하는 것이다. 이러한 방법은 기존 기술의 한계로 인한 어쩔 수 없는 선택이지만, 바로 이 공정이 TSV를 기반으로 하는 제품 대중화에 걸림돌 중 하나가 되고 있다. 이는 종래의 접합 공정이 기판 수준에서 진행된 데 반해 열 압착 접합 공정은 개별 칩 수준으로 떨어졌기 때문이다. 이와 같은 문제를 해결하기 위해 다양한 기술이 제안되고 있다. 현재 주된 기술 개발 방향은 열 압착 공정 프로파일을 최대한 짧게 하여 공정 소요 시간을 줄이는 것이다. 이를 위해 (그림 8b)에서와 같이 접합 헤드의 승온 속도를 100℃/s 이상으로 하고 냉각 속도를 50℃/s 이상으로 유지하는 기술을 개발하고 있고 이를 더욱 극대화하는 노력을 기울이고 있다[15].

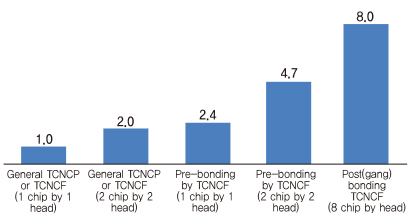

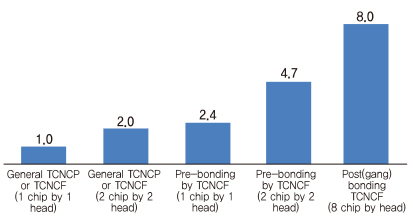

Qualcomm사와 Amkor사는 이러한 문제점을 해결하기 위해 열 압착 접합 공정을 Pre-bonding과 Post bonding으로 나누고 Post bonding의 경우 8개의 칩을 동시에 압착하는 gang Bonding을 적용하였다. 이러한 공정을 위해 접합하고자 하는 칩에 NCF(Non-Conductive Film)를 라미네이션하여 NCP(Non-Conductive Paste)를 도포하는 시간도 줄였다[16]. Pre-bonding 공정에서는 냉각을 도입할 필요가 없고 오직 정렬 공정만 짧게만 하면 되는 장점이 있고 이와 병행으로 Post 공정에서 하나의 접합 헤드로 8개의 칩을 접합할 수 있기 때문에 (그림 9)에서 보는 바와 같이 양산성의 향상이 가능하다.

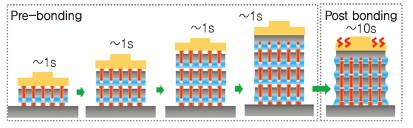

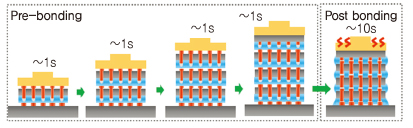

Toray사는 상기와 유사한 개념을 삼차원 적층에 적용할 수 있는 개념을 발표하였다[17]. 즉, (그림 10)에서와 같이 Pre-bonding을 통해 TSV 칩을 삼차원으로 적층하는 것이다. 이 경우에도 오직 정확하게 정렬하는 것만 Pre-bonding에서 요구되기 때문에 공정 시간을 단축시킬 수 있다. 원하는 층까지 적층한 다음 마지막으로 Post bonding을 약 10초 정도 수행함으로 양산성을 확보할 수 있는 개념이다. 이 접합 기술에서도 NCF가 적용되었다. 이러한 Pre-bonding 및 Post bonding의 개념을 실제로 적용시키기 위해서는 NCF의 소재를 최적화하는 기술이 필요하다. 즉, NCF의 온도에 따른 점도의 변화, 필러 제어, 압착 공정시 형태 유지 등 소재의 물리적인 특성을 최적화하는 기술이 필요해서 일반적으로 장비와 소재 개발이 동시에 수행되어야 한다.

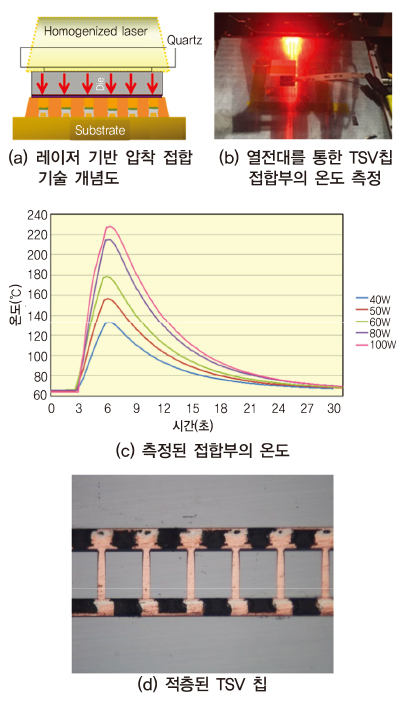

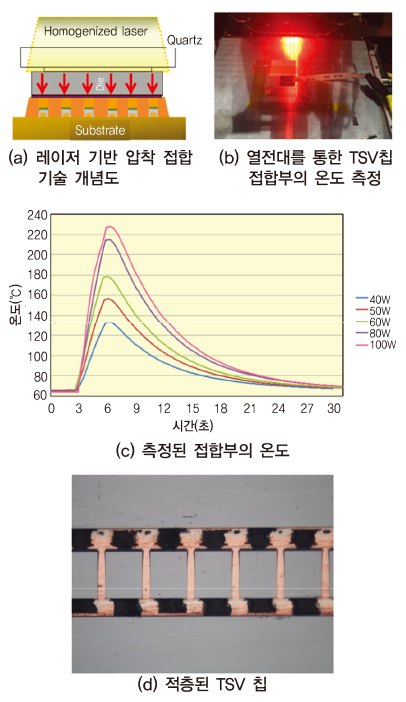

한국전자통신연구원에서는 열 압착 접합 기술의 단점을 극복하기 위해 레이저를 기반으로 한 압착 접합 기술을 개발하였다. 기존 열 압착 접합 기술의 단점은 접합 헤드를 통해 열을 전달하여 접합부 온도를 올린다는 점이다. 이로 인해 냉각에 많은 시간이 소요된다는 점이다. 이러한 문제를 해결하기 위해 (그림 11a)에 나타난 바와 같이 IR(Infra-Red) 레이저를 열원으로 적용하였다. 압력은 Quartz를 통해 전달한다. IR 레이저는 Quartz에 흡수가 거의 되지 않으므로 IR로 인한 Quartz의 승온 문제가 거의 없다. IR 레이저는 실리콘에서 대부분 원자의 진동 형태로 흡수되어 열로 바뀐다. 이와 같은 방법으로 실리콘 자체가 열원이 되고 실리콘의 높은 열 전도율로 인해 접합부에 접합에 필요한 열이 전달된다. (그림 11b)는 TSV 칩 접합부에 열전대를 설치한 다음 레이저 파워 및 시간에 따라 온도 변화를 측정하는 실험 환경을 보여주고 (그림 11c)는 측정 결과를 보여준다. 2초 이내로 최대 온도에 도달하며 8초 이내에 150℃ 이하로 온도가 내려감을 알 수 있다. (그림 11d)는 한국전자통신연구원에서 개발한 NCP의 일종인 Fluxing underfill을 도포한 후 레이저를 가하여 3차원 적층 접합 공정을 완성한 TSV 칩의 단면 사진이다. 짧은 시간에 솔더와 UBM 간의 반응이 정상적으로 이루어졌음을 알 수 있다.

2. 방열 패키지 기술

전자 패키지에서의 방열은 크게 칩 레벨, 모듈 레벨 또는 시스템 레벨로 나뉘어 질 수 있다. 그동안 모듈 및 시스템 레벨에서의 방열 솔루션 제시가 많이 이루어졌지만, 칩 레벨에서는 상대적으로 기술적 어려움에 기인해 그렇지 못한 것이 현실이다. 본 절에서는 최근 제시되고 있는 방열 솔루션에 대해 서술하고자 하며, 칩, 모듈 또는 시스템 레벨로의 구분은 저자의 견해에 따른 것이며, 독자의 이해에 따라 다른 시각을 가질 수 있음을 밝혀둔다.

가. 칩레벨의 방열 기술

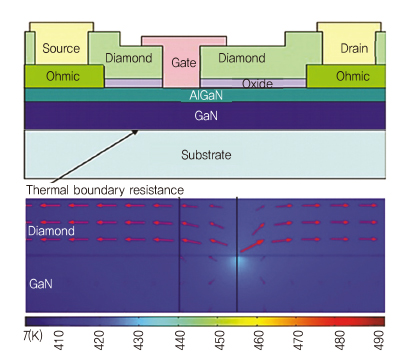

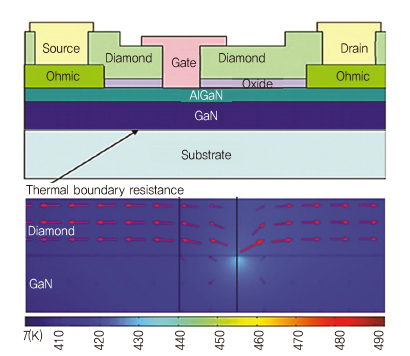

칩 레벨에서의 방열 기술은 작은 크기 및 반도체 공정이 고려되어야 하므로 개발에 제약이 크게 따라왔다. 더구나 칩 패키지는 모듈 또는 시스템 전체 열저항에서 가장 큰 부분을 차지하고 있어 기술적 솔루션의 필요성이 가장 크다. 칩에서의 방열은 소재, 접합 방식 또는 설계 구조에 의해 크게 좌우된다. 방열 소재는 칩 및 기판의 열전도도(Thermal conductivity)가 매우 중요하며, 접합 방식은 기존 Ag-Epoxy(4.3W/m·K), Eutetic(80Au-20Sn, 57W/m·K)에 비해 열전도도가 우수한 Ag sintering(250W/m·K)이 접합 열저항을 크게 감소시키는 것으로 나타나고 있다. 설계 구조 측면에서는 열소산의 향상을 위해 방열 면적 증가뿐만 아니라, 빠른 열점(Hot spot) 제거가 주요 핵심 기술이며, 이를 위해 다이아몬드층을 활용한 열소산 기술 개발이 고온 공정과 기판과의 열팽창 계수 차로 인한 열응력 문제들을 극복하고 최근 들어 크게 증가하고 있다[(그림 12) 참조], [18]. 구체적으로는 HEMT에서 GaN층 위에 CVD로 증착된 다이아몬드층을 통해 대부분의 열이 소산되며, 0.5~10μm의 두께 범위 내에서 효과가 크며, 최소 5μm의 크기만 적용하더라도 방열 효과가 큰 것으로 나타났다. 다만 적층으로 인한 수직방향 상당 열전도도는 크지 않게 되는 점은 해결해야 할 과제이다.

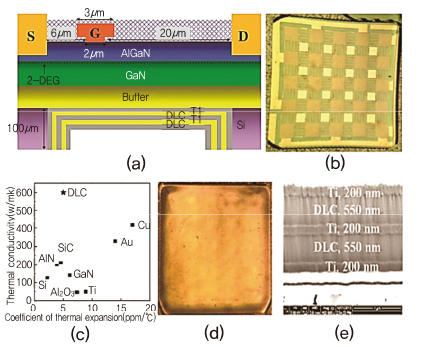

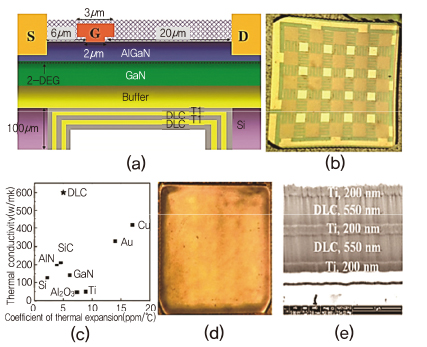

또 다른 열소산 수단으로써 Ti 위에 DLC(Diamond Like Carbon)를 적층하여 사용할 수 있으며, Ti와 반복하여 적층할 때 방열 효과를 위해 최소 1μm 이상은 요구된다. DLC의 적용을 통해 알루미늄 Submount의 표면 온도를 약 2~15℃ 가량 감소시킬 수 있게 된다. 한편 칩의 작은 질량(Mass)로 인한 온도 급상승의 불리함을 보완하기 위한 방안으로써, 칩 뒷면에 가공된 그루브에 PCM을 충전할 수 있으며, 이를 통해 PCM의 용융 상변화 동안 온도 상승을 억제할 수 있게 된다. 기타 그래핀 층을 여러 층 적층하여 평면 방향 열소산 용으로 활용할 수 있으며, 다만 적층 시 섬세한 작업이 요구되는 단점을 갖는다[(그림 13) 참조].

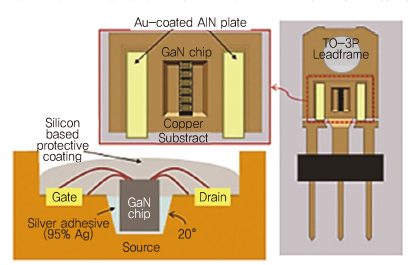

나. 모듈 및 시스템 레벨의 방열 기술

모듈 및 시스템 레벨에서의 방열 기술은 상대적으로 많이 이루어져 왔으며, 주로 패키지 방열 구조 설계, Microchannel을 이용한 액체 냉각 또는 히트파이프 및 히트싱크로 대표되는 건식 냉각 방식들이 고려되고 있다. 패키지 방열 구조 설계에서는 방열 면적이 기본적으로 증가할 수 있도록 칩이 실장되는 캐리어 블록을 V형 그루브 또는 컵(Cup)형 등의 칩 함몰형으로 설계할 수 있다[(그림 14) 참조].

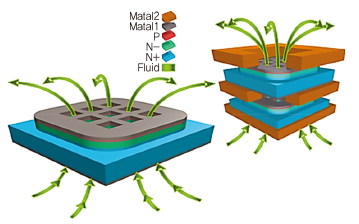

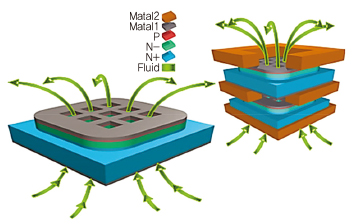

또는 칩 및 기판을 전기주조법(Electroforming)에 의해 증착된 히트싱크에 함몰시킴으로써 Embedded 형 히트싱크 방열 패키지 구조를 고려할 수도 있다. 그러나 열유속(Heat flux)이 증가함에 따라 고성능의 방열 솔루션이 요구되며, 이에 액체 냉각이 주로 활용되고 있다. 액체 냉각은 패키지 크기 제약으로 주로 마이크로채널(Micro channel)을 통한 솔루션이 많이 적용되고 있다. 대표적으로 칩이 직접 실장되는 구리 블록에 마이크로머시닝 기술을 이용하여 마이크로 액체 유로를 설치하는 방식을 고려할 수 있다. 그러나 마이크로 채널을 통한 유동은 커다란 압력 강하(Pressure drop)를 동반할 수 있으며, 이점을 고려해 유로를 기판의 평면 방향이 아닌 기판을 통과하는 수직방향으로 설계할 수도 있다[(그림 15) 참조].

한편 액체 냉각의 효율을 향상시킬 수 있는 방안으로써, 충돌(Impinging) 또는 분사(Spray) 방식이 고려될 수 있으며, 단순 액체 냉각과 비교하면 약 50%가량 방열 성능이 향상되는 것으로 알려져 있다. 이러한 방식은 특히 미세 채널을 통한 액체 냉각 방식의 한계를 어느 정도 해결해 줄 수 있는 장점을 갖는다[(그림 16) 참조].

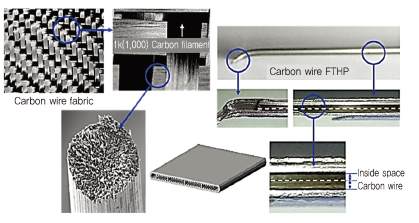

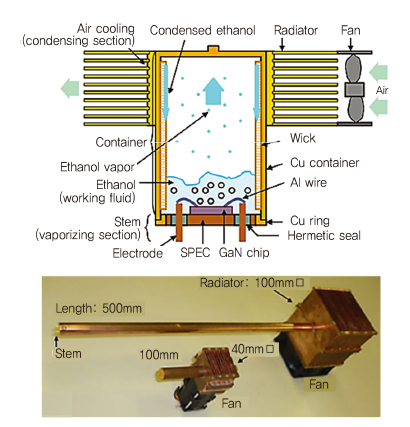

전자 패키지 방열이 내부 또는 주위 온, 습도 환경에 따라 건식(Dry) 방열 기술이 요구되기도 한다. 건식 방열 기술은 히트파이프(Heat pipe) 및 히트 싱크로 대표될 수 있다. 히트파이프 기술은 기판 또는 PCB 자체를 Vapor chamber(히트파이프의 일종)로 제작하는 형태로 적용될 수 있으며, 패키지 내 열점(Hot spot)을 제거할 수 있어 신속한 열소산(Heat dissipation)이 가능하며 이는 히트파이프의 상변화(Vapor-liquid phase change) 열전달에 의한 상당 열전도도(Equivalent thermal conductivity)가 약 10,000~20,000W/mK에 이르기 때문이다[(그림 17) 참조].

히트 싱크 기술은 오래된 솔루션이면서도 적용 대상에 따라 최적화된 방열 구조의 설계가 요구되며, 이에 대한 시뮬레이션 평가는 매우 유용하게 활용될 수 있다.

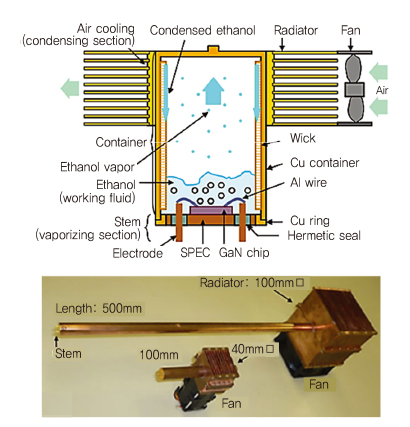

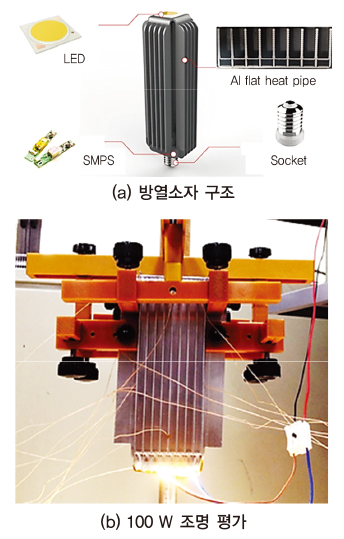

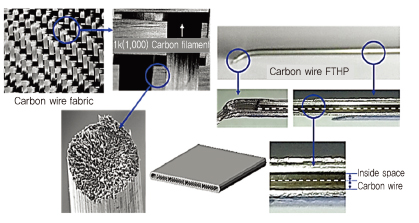

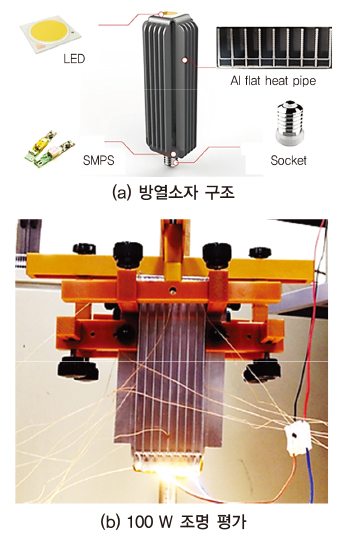

ETRI는 칩, 모듈 및 시스템의 모든 레벨에서 활용 가능한 히트파이프 기술 및 알루미늄 판상 소재 기반의 방열 소자 기술을 개발해 오고 있다. 구체적으로는 기존 인발 구리 원형 소재 기반에서 압출 알루미늄 판상 소재 기반으로의 기술적 변화를 이룸으로써, 대면적화, 경량, 저가 및 다기능화의 차별적 특성을 갖게 되었다[(그림 18) 참조].

응용 기술로 다점 히트 소스를 갖는 레이다 어레이의 건식(Dry) 방열 기술로써 구조 개발이 이루어진 바 있으며, 100W급 소켓형 LED 산업 등의 방열 장치로써 접목돼 중량을 650g까지 감소시키고, 광효율을 5배 향상시킨 바 또한 있다. 아울러 디스플레이 열점 제거용의 대면적 열소산 기술로써도 활용되고, 반도체 장비의 방열 및 온도균일화 기술로도 활용될 전망이다[(그림 19) 참조].

Ⅲ. 결론

최근 전자 패키징 기술의 발전으로 빅데이터, IoT, 인공지능, 가상현실, 증강현실 등 4차 산업혁명의 핵심 기술이 구체화되고 있다. 구체적으로 2.5D/3D 집적 기술을 기반으로 한 이종 접합 기술, 대용량(High bandwidth) 인터페이스 기술, 방열 기술 등이 그것이다. 본 고를 통해 언급된 기술들의 최근 동향과 앞으로 발전 방향을 살펴보았으며 이러한 숨어 있는 기술들의 지속적인 국산화 및 고도화로 다가오는 4차 산업혁명 시대에 대한민국의 기술적인 우위를 확보할 수 있기를 바란다.

용어해설

TSV(Through Silicon Via, 실리콘 관통 홀) 실리콘을 수직 관통하여 전극을 형성하여 수직으로 전기적인 신호를 전달하는 기술로 인커너텍션 밀도를 극대화할 수 있고 전기적인 기생성분이 작아 대용량 전송에 유리하다.

인터포저(Interposer) 둘 사이에 놓다 라는 의미의 라틴어인 interp?nere에서 유래하였다. 두 개의 서로 다른 연결을 이어주는 전기적인 인터페이스 라우팅을 의미하며 칩과 기판 사이의 인터커넥션 간격이 다를 경우 적용된다.

2.5D 집적 기술 TSV가 적용된 실리콘 인터포저를 활용한 집적 기술이다. 종래의 기판에서 구현할 수 없는 고밀도의 배선 및 접합 기술을 지원함으로 종래의 기술과 차별성을 돋보이도록 만들어진 용어이며 실리콘 인터포저위에 다양한 디바이스 및 3D 모듈을 실장할 수 있기 때문에 이종 접합 기술의 플랫폼으로 여겨지고 있다.

약어 정리

AR

Augmented Reality

BEOL

Back End of Line

CHIPS

Common Heterogeneous Integration and IP Reuse Strategies

CMOS

Complementary Metal Oxide Semiconductor

DDR

Double Data Rate

DLC

Diamond Like Carbon

DRAM

Dynamic Random-Access Memory

GDDR

Graphics Double Data Rate

GPU

Graphics Processing Unit

HBM

High Bandwith Memory

IoT

Internet of Things

IP

Intellectual Property

IR

Infra-Red

ITRS

International Technology Roadmap for Semiconduc-tor

NAND

Negative-AND

NCP

Non-Conductive Paste

NCF

Non-Conductive Film

PCM

Phase Change Material

TSV

Through Silicon Via

UBM

Under Bump Metallization

VR

Virtual Reality

ECTC, “Major Topics, Call for Papers,” Accessed 2017. http://www.ectc.net/abstracts/callforpapers2018.pdf

The Processor-Memory Bottleneck, Accessed 2017. http://www.pcguide.com/ref/ram/timingBottleneck-c.html

J. Kim and Y. Kim, “HBM: Memory Solution for Bandwidth-Hungry Processors,” IEEE Hot Chips 26 Symp. (HCS), Cuperti-no, CA, USA, Aug. 12, 2014, pp. 1?24.

Wikipedia, “High Bandwidth Memory,” Accessed 2017. https://en.wikipedia.org/wiki/High_Bandwidth_Memory#cite_note-16

D. Taneja et al., “Understanding the Behavior of SnAg Bumps at 10 μm Pitch and Below for Imaging and Microdisplay Appli-cation,” IEEE Electron. Components Technol. Conf., LasVegas, NV, USA, May 31?June 3, 2016, pp. 361?367.

J.-A. Carballo et al., “ITRS 2.0: Toward a Re-framing of the Semiconductor Technology Roadmap,” IEEE Int. Conf. Comput. Des., Seoul, Rep. of Korea, 2014, pp. 139?146.

H. Mujtaba, “NVIDIA Pascal GPU’s Double Precision Perfor-mance Rated at Over 4 TFLOPs, 16nm FinFET Architecture Confirmed ? Volta GPU Peaks at Over 7 TFLOPs, 1.2 TB/s HBM2,” Accessed 2017. http://wccftech. com/nvidia-pascal-volta-gpus-sc15/

D. Green, “Common Heterogeneous Integration and IP Reuse Strategies (CHIPS),” Accessed 2017. https://www. darpa.mil/program/common-heterogeneous-integration-and-ip-reuse-strategies

W.-S. Lee et al., “A Study of the Effectiveness of Underfill in the High Bandwith Memory with TSV,” Int. Symp. Microelectron., vol. 2013, no. 1, 2013, pp. 810?813.

A. Eitan and K.Y. Hung, “Thermo-Compression Bonding for Fine-Pitch Copper-Pillar Flip-Chip Interconnect? Tool Features as Enablers of Unique Technology,” IEEE Int. Conf. Comput. Des., San Diego, CA, USA, May 26?29, 2015, pp. 460?464.

S. Ahn et al., “Wafer Level Multi-chip Gang Bonding Using TCNCF,” IEEE Int. Conf. Comput. Des., Las Vegas, NV, USA, May 31?June 3, 2016, pp. 122?127.

N. Asahi et al., “High Productivity Thermal Compression Bonding for 3D IC,” IEEE Int. 3D Syst. Integr. Conf., Sendai, Japan, 2015, pp. 129?133.

Y. Zhou et al., “Thermal Characterization of Polycrystalline Diamond Thin Film Heat Spreaders Grown on GaN HEMTs,” Appl. Phys. Lett., vol. 111, no. 4, 2017.

A. Wang, M.J. Tadjer, and F. Calle, “Simulation of Thermal Management in AlGaN/GaN HEMTs with Integrated Diamond Heat Spreaders,” Semicond. Sci. Technol., vol. 28, 2013.

H.C. Chiu et al., “High-Performance, Micromachined GaN-on-Si High-Electron-Mobility Transistor with Backside Dia-mondlike Carbon/Titanium Heat-Dissipation Layer,” Appl. Phys. Exp., vol. 8, no. 1, 2015, pp. 1?4.

S. Cheng et al., “Enhanced Lateral Heat Dissipation Packaging Structure for GaN HEMTs on Si Substrate,” Appl. Thermal Eng., vol. 51, no. 1?2, 2013, pp. 20?24.

K. Vladimirova et al., “Innovative Heat Removal Structure for Power Devices - The Drift Region Integrated MicroChannel Cooler,” Int. Symp. Power Semicond. Dev. IC's, San Diego, CA, USA, May 23?26, 2011, pp. 332?335.

J.L. Xie et al., “Multi Nozzle Array Spray Cooling for Large Area High Power Device in a Closed Loop System,” Int. J. Heat Mass Transfer, vol. 78, Nov. 2014, pp. 1177?1186.

N. Otsuka et al., “Low-Pressure Direct-Liquid-Cooling Technology for GaN Power Transistors,” Japanese J. Appl. Phys., vol. 50, no. 4s, 2011, pp. 1?5.

Y.W. Park et al., “Development of an Aluminum Flat Heat Pipe with Carbon Wire Wick,” Joint 18th Int. Heat Pipe Conf. 12th Int. Heat Pipe Symp., Jeju, Rep. of Korea, June 12?16, 2016.

(그림 1)

HBM을 적용한 GPU 메모리 모듈 단면도[8]

[출처] Shmuel Csaba Otto Traian [CC BY-SA 4.0(https:// creativecom-mons.org/licenses/by-sa/4.0) or GFDL (http:// www.gnu.org/copyleft/fdl.html)], via Wikimedia Commons.

- Sign Up

- 전자통신동향분석 이메일 전자저널 구독을 원하시는 경우 정확한 이메일 주소를 입력하시기 바랍니다.