극한 환경용 반도체 기술 동향

Technical Trends of Semiconductors for Harsh Environments

- 저자

-

장우진RF/전력부품연구그룹 wjchang@etri.re.kr 문재경RF/전력부품연구그룹 jkmun@etri.re.kr 이형석RF/전력부품연구그룹 hyungseok@etri.re.kr 임종원RF/전력부품연구그룹 jwlim@etri.re.kr 백용순광무선융합연구본부 yongb@etri.re.kr

- 권호

- 33권 6호 (통권 174)

- 논문구분

- 최신 반도체, 하드웨어 기술 동향 특집

- 페이지

- 12-23

- 발행일자

- 2018.12.21

- DOI

- 10.22648/ETRI.2018.J.330602

본 저작물은 공공누리 제4유형: 출처표시 + 상업적이용금지 + 변경금지 조건에 따라 이용할 수 있습니다.

본 저작물은 공공누리 제4유형: 출처표시 + 상업적이용금지 + 변경금지 조건에 따라 이용할 수 있습니다.- 초록

- In this paper, we review the technical trends of diamond and gallium oxide (Ga2O3) semiconductor technologies among ultra-wide bandgap semiconductor technologies for harsh environments. Diamond exhibits some of the most extreme physical properties such as a wide bandgap, high breakdown field, high electron mobility, and high thermal conductivity, yet its practical use in harsh environments has been limited owing to its scarcity, expense, and small-sized substrate. In addition, the difficulty of n-type doping through ion implantation into diamond is an obstacle to the normally-off operation of transistors. Ga2O3 also has material properties such as a wide bandgap, high breakdown field, and high working temperature superior to that of silicon, gallium arsenide, gallium nitride, silicon carbide, and so on. In addition, Ga2O3 bulk crystal growth has developed dramatically. Although the bulk growth is still relatively immature, a 2-inch substrate can already be purchased, whereas 4- and 6-inch substrates are currently under development. Owing to the rapid development of Ga2O3 bulk and epitaxy growth, device results have quickly followed. We look briefly into diamond and Ga2O3 semiconductor devices and epitaxy results that can be applied to harsh environments. are currently under development. Owing to the rapid development of Ga2O3 bulk and epitaxy growth, device results have quickly followed. We look briefly into diamond and Ga2O3 semiconductor devices and epitaxy results that can be applied to harsh environments.

Share

Ⅰ. 서론

20세기 과학기술의 업적 중에서 현대생활을 크게 바꿔놓은 발명품을 꼽으라면 반도체 소자이다. 반도체 소자의 발명은 집적회로, 메모리 소자, 마이크로프로세서 등으로 이어지면서 개인용 컴퓨터가 보급되고 인터넷과 광무선 통신의 혁신적인 발전으로 이어져 정보의 세계화가 이뤄졌고, 이제는 우리 생활에 깊숙이 자리 잡고 있는 스마트폰으로 발전하면서 반도체가 없는 현대 사회는 상상할 수 없을 만큼 이미 우리 생활에 밀접하게 자리 잡고 있다. 또한, AI, IoT 등의 급속한 발달로 반도체 소자는 실로 현대사회 인간에게 있어서 의식주와 같은 존재라고 해도 과언이 아니다.

1947년 초기에 개발된 게르마늄(Ge) 반도체는 1954년 이후부터는 실리콘(Si)에 반도체 소재의 주인 자리를 물려줌으로써, ‘최초로 트랜지스터에 적용’이라는 영예만을 남긴 채 반도체 산업에 크게 기여하지 못한 반도체 소재로 역사에 기록되었다. 1960년대부터 성장한 메모리 및 마이크로프로세서 산업의 핵심인 실리콘을 제1세대 반도체 소재라고 한다면, 1970년대 이후 본격적인 연구개발이 이루어지면서 고속 및 고주파 전자소자, 광전소자 분야를 전담해 온 갈륨비소(GaAs), 인듐인(InP) 계열의 III-V족 화합물은 제 2세대 반도체 소재이다. 1990년경 청색 발광 다이오드를 시작으로 가시광 광전소자의 실용화에 성공한 질화갈륨(GaN) 계열의 질화물 및 탄화규소(SiC) 소재는 다른 반도체가 가지지 못하는 광대역 파장범위의 광전 기능과 고출력/초고주파 전자 기능 등 다양한 응용이 가능한 제 3세대 반도체 소재로 분류할 수가 있다.

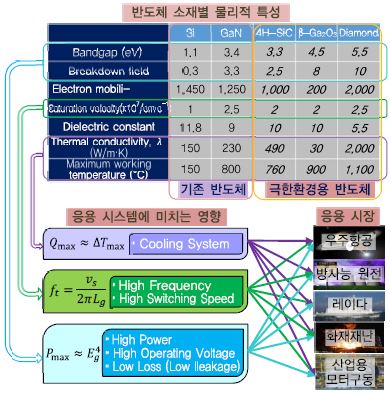

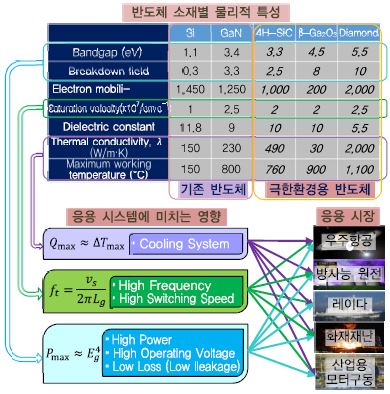

하지만, 앞서 열거한 제 1~3세대 반도체 소재는 재료의 물성적 한계로 인하여, 극고전압/고온/고압/고충격/고방사선 중에서 한 가지 이상이 존재하는 스마트 그리드, 철도수송, 풍력발전터빈, 선박 및 산업용 모터, HEV/EV, 자동차 엔진, 태양광 발전 인버터, 재난탐지, 원유탐사장비, 우주산업 등의 환경 조건을 의미하는 극한 환경에 적합한 반도체 소자로의 응용이 어렵다. (그림 1)과 같이, 극한 환경용 반도체는 1~3세대 반도체로 분류한 기존 실리콘 및 화합물 반도체보다 안정적으로 동작할 수 있는 우수한 물성을 가진 UWBG 반도체로서, 다이아몬드(diamond) 반도체, 산화갈륨(Ga2O3) 반도체, 질화알루미늄(AlN) 반도체 등이 해당된다.

(그림 1)의 반도체 물성 중에서 밴드갭 특성이 실리콘이 1.1eV인데 비해 다이아몬드는 5.5eV, 산화갈륨은 4.5eV로 4~5배 우수하고, 항복전계도 실리콘은 0.3MV/cm인데 비해 다이아몬드는 10MV/cm, 산화갈륨은 8MV/cm로 27~33배 우수하여 실리콘 반도체로는 구현이 어려운 초고전압/초고전력용 시스템 응용이 가능하다. 반도체 물성 중에서 포화 속도 특성은 실리콘이 1× 107cm/s에 비해 다이아몬드는 2.5× 107cm/s, 산화갈륨은 2× 107cm/s으로 2~2.5배 우수하여 실리콘 반도체에 비해 초고속/초고주파 특성을 얻을 수 있다. 이와 같은 특성으로 인해 전력반도체 응용에 있어서 인덕터와 커패시터와 같은 주변 회로의 크기를 줄여 시스템의 크기와 가격을 줄일 수 있다. 반도체 물성 중에서 열전도도 특성은 실리콘이 150W/m·K에 비해 다이아몬드는 2,000W/m·K, 산화갈륨은 30W/m·K로 0.2~13배이고 최대 동작 온도는 실리콘이 150℃ 에 비해 다이아몬드는 1,100℃ , 산화갈륨은 900℃ 로 6~7배 우수하여 실리콘 반도체로는 구현이 어려운 극고온용 시스템 응용이 가능하다.

극한 환경에 속하는 인공위성이나 탐사로봇 등에 사용되는 반도체 기술은 기존 실리콘 반도체와 화합물 반도체 기술을 적용하고 있으나, 고온 및 내방사선 등의 극한 환경을 위해 방열을 위한 모듈과 밀폐구조, 차폐구도 등을 사용하고 있으며 이로 인하여 중후장대(重厚長大)한 부품으로 사용하고 있는 실정이다. 이와 같은 중후장대한 부품을 경박단소(輕薄短小)한 부품으로 개발하기 위해서는 앞서 설명한 반도체 물성이 우수한 UWBG 반도체 기술 개발이 필수적이다.

이와 같은 흐름에 발맞추어, 미국에서는 화성탐사 프로젝트를 본격적으로 추진하면서 고온 및 방사선 환경 탐사로봇인 스피릿을 개발하였으며, 고온 및 방사선 등의 극한 환경에서 화성표면의 각종 데이터를 지상으로 전송하는데 성공하였고 대체 에너지 개발 기술의 필요성이 증가하고 있으며 원자로 등의 안전 감시 및 사고 대응을 위해 200℃ 이상의 고온과 10MGy 정도의 고방사능의 환경에서 사용할 수 있는 로봇에 적용할 극한 환경용 반도체 소자 개발에 박차를 가하고 있다. 또한, 미국 NASA에서는 금성 대기조건인 약 460℃ , 94MPa에서 구동 가능한 구동 온도 500℃ 이상의 금성 탐사체용 전자소자에 대한 연구도 활발히 진행 중이다.

극한 환경용 반도체 기술 중에서 다이아몬드 반도체기술과 산화갈륨 반도체 기술의 주요 이슈는 각각 크게 세 가지로 나눌 수 있는데, 다이아몬드 반도체 기술의 경우는 대구경 기판 제작의 어려움, n형 도핑 기술 부재, 높은 단가이며, 산화갈륨 반도체 기술의 경우는 p형 도핑 기술의 부재, 저전류 밀도, 낮은 열전도도이다.

본고에서는 극한 환경용 반도체 기술 중에서 다이아몬드 반도체 기술과 산화갈륨 반도체 기술을 중심으로 주요 이슈 및 연구 개발 동향을 살펴보고자 한다.

Ⅱ. 극한 환경용 반도체 기술 동향

1. 다이아몬드 반도체 기술 동향

이 절에서는 극한 환경용 반도체 중에서 다이아몬드 반도체 기술의 특징과 관련 연구 동향에 대해 살펴보고자 한다.

다이아몬드는 보석으로서의 가치는 언급할 필요도 없으며, 물리적 특성면에서 초고온/초고전력 전력소자를 위한 우수한 재료 중의 하나이다. 다이아몬드 물성 가운데 가장 우수한 특성은 3차원 구조와 강한 공유결합으로 인해 경도가 큰 것이며 뛰어난 열전도도, 큰 밴드갭, 전자 및 홀의 높은 이동도가 매우 우수하다. 이러한 우수한 특성이 가지고 있지만 천연 다이아몬드는 불행히도 매우 고가이고 희귀하다. 과학자들의 끊임없는 연구로 HTHP 성장기법을 1958년의 Eversole과 1968년 Deryagin의 실험의 아이디어에서 출발하여 HFCVD, MWCVD, HTCVD 기술로 발전하면서 다이아몬드를 제조할 수 있게 되었다.

다이아몬드 결정성장은 단결정 다이아몬드 성장과 다결정 다이아몬드 성장이 있으며, 단결정 다이아몬드 성장은 동종 기판 상에 성장시키는 호모 에피텍시(homo-epitaxy) 성장과 이종 기판 상에 성장시키는 헤테로 에피텍시(hetero-epitaxy) 성장이 있다. 소자의 종류별로 다결정 다이아몬드를 활용하여 제작하는 소자도 있으나 비교적 특성이 떨어지므로 보다 특성이 우수하고 광범위한 소자로의 활용을 위해서는 단결정 다이아몬드가 필요하다. 호모 에피텍시 성장의 경우는 결함이 최소화된 단결정 다이아몬드 성장이 Sumitomo Electric 社를 중심으로 큰 진척을 보였으며 캐리어(carrier) 이동도가 가장 우수한 천연 다이아몬드보다도 우수한 특성을 갖는다.

다이아몬드 반도체의 n형 및 p형 도핑기술은 증가형(enhancement-mode) FET 구현을 위해 필요한 기술로서, p형 도핑은 붕소(B)를 HTHP 분위기에서 수소와 함께 도핑하는 기술을 사용하여 용이하게 구현되지만, n형 도핑은 n형 도핑원소인 인(P)이나 질소(N)가 매우 작은 다이아몬드 격자 상수로 인해 다이아몬드 격자 사이에 존재하기 어렵기 때문에, 아직도 n형 도핑에 대한 확실한 방법이 제시되지 못하는 기술적 한계가 있으며, 최근에는 황(S)을 이용한 도핑연구가 진행되고 있다.

n형 도핑 문제에 있어서 도핑원을 이용하거나 이온 주입법 등의 공정기술을 연구하고 있으며 일본 등에서 황을 이용한 n형 SJ 도핑이 이뤄지고 있으나, 전자소자 응용에 필요한 도핑농도 수준까지는 아직까지는 한계가 있다.

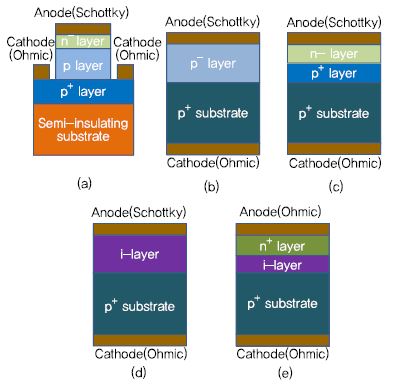

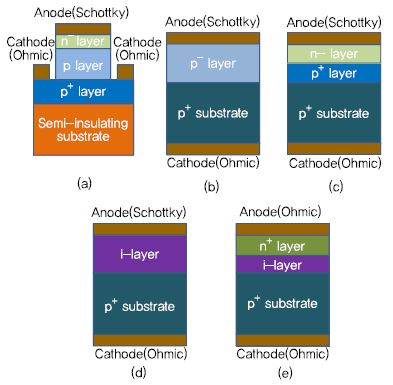

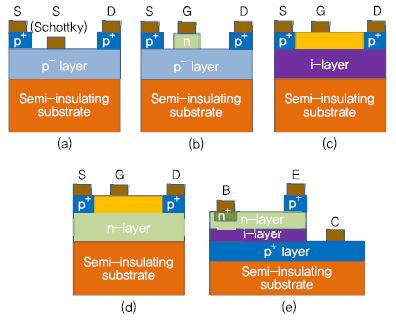

(그림 2)는 지금까지 발표된 다이아몬드 다이오드의 대표적인 구조를 정리한 것이다. 각각의 구조별 특성을 살펴보면, (a)구조는 항복전압이 2.5kV, 항복전계는 7MV/cm 이상이며[1], [2], 최대 전류는 0.5A, 최대 전류밀도는 4.5kA/cm2[2]이며, 400℃ 와 X-선 환경에서 인터페이스가 안정적인 특성을 얻었다. (b)구조는 항복전압이 1.8kV[3], 항복전계는 2.7MV/cm 이며[4], 최대 전류는 20A[5], 최대 전류밀도는 1kA/cm2 이상이며, 250℃ 환경에서 20ns 이하의 역방향 회복 시간(trr) 특성을 얻었다. (c)구조는 항복전압이 100V 이상, 항복전계는 3.4MV/cm이며[6], 최대 전류는 0.1A 이하, 최대 전류밀도는 60kA/cm2 이상[6]의 특성을 얻었다. (d)구조는 항복전압이 2.5kV[7], 항복전계는 4.2MV/cm이며[7], 최대 전류는 0.1A 이하, 최대 전류밀도는 7.5kA/cm2 이상[8]의 특성을 얻었다. (e)구조는 항복전압이 10kV[9], 항복전계는 3.4MV/cm[9], 최대 전류는 0.1A 이하의 특성을 얻었으며 다른 구조에 비해 높은 항복전압 특성을 보였다.

일본 산업기술종합연구소(AIST)에서는 다이아몬드 SBD 전력소자의 경우는 B(boron) 도핑된 p+ 단결정 다이아몬드(001) 기판 위에 p-표동(drift) 층을 MWCVD로 증착하여 제작하였으며, 증착은 120 Torr 압력과 1,000℃ 온도 조건에서 p-표동(drift) 층을 9μ m로 성장시켰다. 방사선 시험에서도 10MGy까지 동작이 확인되었다[10]. 방사선 조사 이전에는 누설전류가 약 100nA/cm2 정도였으며, 3MGy 방사선 조사에는 역방향 전압이 약 70V까지는 방사선 조사전과 누설전류가 거의 변화가 없었으나 10MGy 방사선 조사 이후에는 역방향 전압이 약 30V에서 약 10μ A/cm2 정도로 이전의 특성과 비교하면 누설전류가 약 100배 정도 커지는 결과를 보였다. 다이아몬드 FET도 제작하였는데, HPHT 반절연 다이아몬드(001) 기판 위에 p-표동(drift) 층을 증착하고 p+층을 이용한 옴믹 접촉을 통해 드레인 전극과 소스 전극을 형성하고 쇼트키(Schottky) 게이트를 형성하여 제작하였다. 항복전압 특성은 0.72MV/cm의 결과를 보여서 다이아몬드 물성의 한계 값보다는 약 10배 정도 낮은 특성을 발표하였고 방사선 특성도 10MGy 방사선 조사 이전과 이후를 비교하면 온오프 전류비가 약 4배 정도 감소된 결과를 발표하였다.

지금까지 발표된 다이아몬드 트랜지스터의 대표적인 구조는 (그림 3)에서 볼 수 있다. 각각의 구조별 특성을 살펴보면, (a)구조는 항복전압이 2.2kV, 항복전계는 2.1MV/cm이며[10], 최대 전류는 30mA, 최대 전류밀도는 250℃ 에서 3mA/mm이며, 500℃ 와 10MGy X-선 조사 후에도 안정적인 동작 특성을 얻었다. (b)구조는 항복전압이 600V 이상[11], 항복전계는 6MV/cm 이며[12], 최대 전류밀도는 1,450A/cm2[12] 특성을 얻었다. (c)구조는 항복전압이 2kV[13], 항복전계는 3.6MV/cm[14], 최대 전류는 1.3A[15], 최대 전류밀도는 1.3A/mm[15], 최대발진주파수는 100GHz 이상의 특성을 얻었다. (d)구조는 항복전압이 50V, 최대 전류는 1mA, 채널의 반전(inversion)을 통한 증가형 모드의 특성을 얻었다. (e)구조는 항복전압이 50V, 최대 전류는 1mA의 특성을 얻었으며 앞의 (a)~(d)는 FET 구조인데 비하여 (e)는 BJT 구조이다.

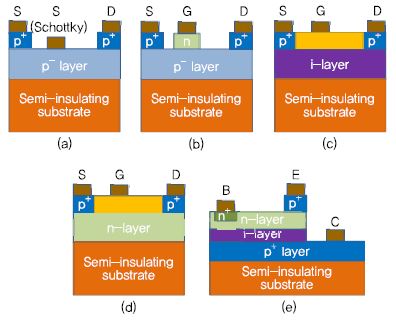

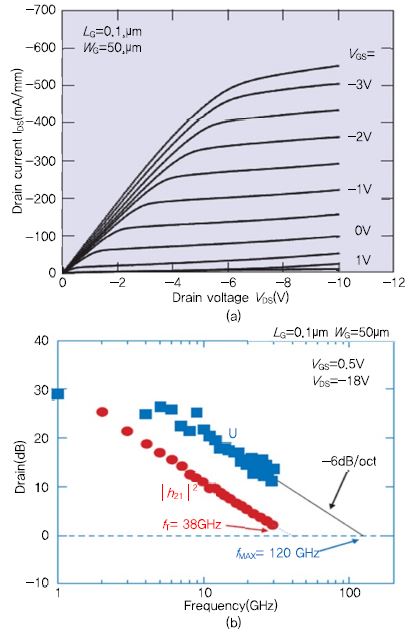

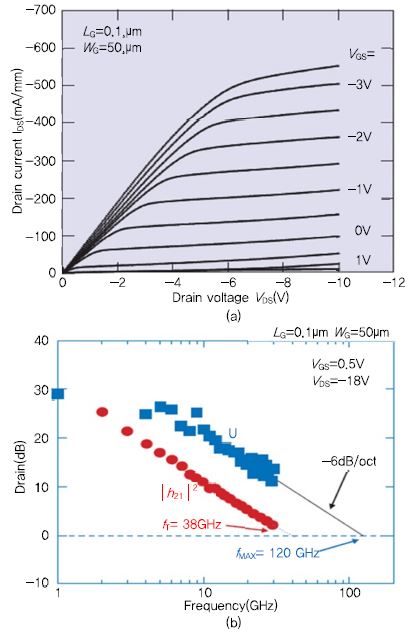

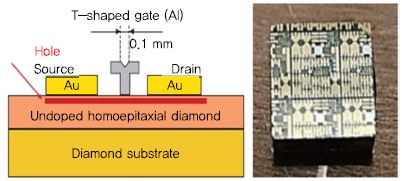

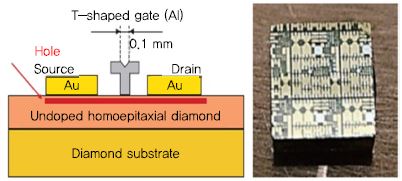

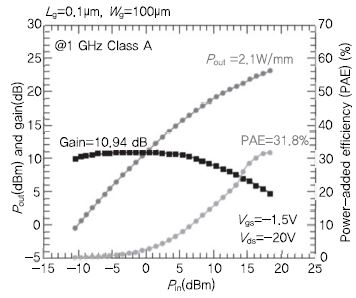

일본의 와세다 대학과 NTT를 중심으로 다이아몬드 기판 가공 및 소자개발이 연구를 수행하였으며, NTT에서는 4mm× 4mm 크기의 단결정 다이아몬드에 FET를 (그림 4)와 같이 제작하여 발표하였다. 특성을 살펴보면, 최대 드레인 전류는 0.55A/mm이며, (그림 5)와 같이 RF 특성은 38GHz의 차단주파수(fT), 120GHz의 최대 발진주파수(fmax) 특성을 얻었다[16].

(그림 4)

다이아몬드 반도체 FET 구조 및 사진

[출처] Reprinted from M. Kasu, “Diamond Field-Effect Transistors as Microwave Power Amplifiers,” NTT Techn. Rev., vol. 8, no. 8, Aug. 2010, pp. 1-5.

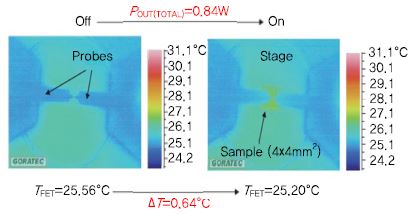

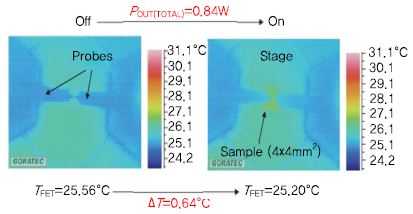

위와 같이 제작된 다이아몬드 FET에 RF 출력전력을 온/오프(On/Off)함에 따라 소자의 표면온도를 비교해보았는데 (그림 6)과 같이 0.84W 전력소모시 0.6℃ 의 온도 상승을 보였으며, 이는 GaAs FET에 비해 1/50 수준의 온도 상승으로 물성의 차이(1/50)로 인한 효과를 그대로 얻었다고 볼 수 있다[16]. (그림 7)은 다이아몬드 반도체 FET의 특성을 나타내었다.

(그림 6)

다이아몬드 반도체 FET의 적외선 열화상 비교 사진

[출처] Reprinted from M. Kasu, “Diamond Field-Effect Transistors as Microwave Power Amplifiers,” NTT Techn. Rev., vol. 8, no. 8, Aug. 2010, pp. 1-5.

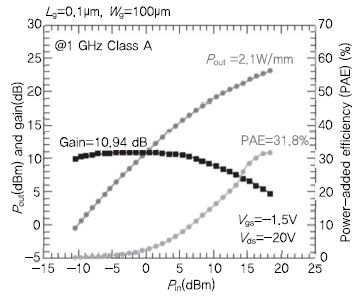

(그림 7)

다이아몬드 반도체 FET의 Class A 동작시 1GHz에서 RF 특성

[출처] Reprinted from M. Kasu, “Diamond Field-Effect Transistors as Microwave Power Amplifiers,” NTT Techn. Rev., vol. 8, no. 8, Aug. 2010, pp. 1-5.

최근에는 다이아몬드 박막 성장기술은 DC-PACVD, HFCVD 등의 방법을 사용하여 4인치 실리콘 기판에 나노 결정 다이아몬드(NCD) 박막을 증착하였으며, 이와 같은 박막기술의 발달로 다이아몬드 박막을 이용하여 다이아몬드의 높은 열전도도 특성을 GaN FET 소자에 상부 방열층으로 응용하는 연구가 진행되고 있다.

미국 해군연구소(NRL)에서는 GaN FET 구조의 에피층 위에 질화규소(SiN) 패시베이션 층(passivation layer)을 형성한 후 750℃ , CH4/H2 분위기에서 MWCVD로 NCD 박막을 증착하고 게이트 메탈 형성을 위해 NCD 박막을 식각하는 공정을 거친 후 게이트를 형성하여 소자에서 열이 가장 많이 발생되는 게이트에 인접하도록 NCD 박막을 위치하도록 하였다. 이를 통해 열방출 효과를 높여 채널의 온도를 20% 낮출 수 있었고 전기적 특성도 향상되었다. 열방출 효율을 더 향상시키기 위해 열전도도 특성이 좋지 않은 SiN 패시베이션 층을 없애고 GaN FET구조의 에피층 위에 NCD 박막을 증착하여 NCD 박막이 패시베이션 층 및 열방출 층 역할을 동시에 할 수 있는 구조를 제안하였다[17]. NCD 박막이 없는 구조의 FET의 특성을 살펴보면, 2-DEG 이동도는 1,220cm2/V·s이며, 면저항은 533Ω/□이며, 온저항은 14.6Ωmm이고, 최대전류는 0.38A/mm, 누설전류는 10μ A/mm, 문턱전압은 -3.07V, 항복전압은 615V였다. 이에 반해 NCD 박막이 있는 구조의 FET를 살펴보면, 2-DEG 이동도는 1,280cm2/V·s이며, 면저항은 478Ω/□이며, 온저항은 11.9Ωmm이고, 최대전류는 0.445A/mm, 누설전류는 95μ A/mm, 문턱전압은 -3.36V, 항복전압은 805V였다. GaN-on-SiC 기판 상에서 GaN HEMT 표면과 약 1μ m 두께의 NCD 박막을 통한 열확산층 사이에 10~50nm 두께의 SiN 중간층을 갖도록 공정하여 제작한 소자는 10GHz에서 전력밀도는 5.2W/mm이고 효율은 52%로 발표하였다. NCD를 통한 열방출 개선효과는 NCD 박막이 없는 소자에 비해 최대전류도 20% 향상되었으며 평균 채널온도도 15~20℃ 감소하였다[18]. NCD가 없는 FET는 약 6W/mm의 출력 전력 특성을 보일 때 약 97℃ 의 온도가 측정되어 3.61℃ ·mm/W의 특성을 나타내며 NCD가 있는 FET는 약 6W/mm의 출력 전력 특성을 보일 때 약 74℃ 의 온도가 측정되고 약 9.5W/mm의 출력 전력 특성을 보일 때 약 78℃ 의 온도가 측정되고 0.96℃ ·mm/W의 특성을 나타내어 NCD 박막의 유무에 따른 특성을 확실이 보여주었다.

중국 Xidian 대학에서는 GaN-on-SiC HEMT 구조에서 패시베이션 층으로 SiN 층 위에 1μ m 두께의 다이아몬드 박막 층을 추가하여 GaN HEMT 소자의 채널에 대한 온도분포를 시뮬레이션하여 비교하였는데, 드레인 전압이 30V일 때는 다이아몬드 박막이 52℃ 차이를 보였고 이로 인한 전류도 약 30% 증가하였다고 발표하였다. 아울러 다이아몬드 박막 층의 두께를 10μ m까지 증가시키면 온도 차이는 약 85℃ 차이를 보이고 다이아몬드 박막 층의 두께가 증가할수록 발열량도 증가하며 차단주파수와 최대발진주파수도 각각 29%와 47% 증가하였다고 발표하였다[19].

2. 산화갈륨 반도체 기술 동향

이 절에서는 극한 환경용 반도체 중에서 산화갈륨 반도체 기술의 특징과 관련 연구 동향에 대해 살펴보고자 한다.

산화갈륨 반도체 단결정 소재에 대한 연구는 일본에서 FZ 방법을 이용한 1인치 이하의 기판을 제작하였으나 기판 결정성도 우수하지 않아 실용화 단계에 이르지 못하였고, 이후 일본 재료연구소에서 EFG 기술을 개발하여 Tamura 社에서 최초로 상업화에 성공하였다. 현재 Tamura 社에서는 세계에서 유일하게 105/cm2 이하의 결함농도를 가지는 2인치 크기의 산화갈륨 반도체 기판을 생산하여 전세계에 공급하고 있다. β-Ga2O3 벌크 결정은 Ga2O3 파우더에 SnO2 파우더 또는 SiO2 파우더를 추가하여 n-형 결정을 만든다[20].

Tamura 社에서 산화갈륨 기판의 상업화에 성공한 이후, 독일, 미국, 일본 등 여러 곳에서 EFG 방법보다 생산성이 우수한 Czochralski 성장법, 순도가 우수한 FZ 방법 등을 이용하여 2인치에 근접한 결정성장 결과를 발표하였다[21], [22].

넓은 밴드갭(Eg=4.8~5.3eV) 장점으로 인하여 고전압 전력소자 구현을 위한 연구가 가장 활발하게 진행 중이며, 산화갈륨 에피성장 기술은 2000년대 후반부터 일본을 중심으로 다양한 결과들이 발표되고 있고, 2015년 이후 미국과 유럽에서도 에피성장 결과들이 보고되기 시작하였다.

산화갈륨 에피성장에 대한 연구는 일본이 가장 주도적으로 앞서가고 있으며, 선진 연구기관에서는 MBE, Mist-CVD, HVPE 성장 방법 등 여러 기술을 통해 산화갈륨 소재의 성장기술에 대한 활발한 연구가 진행되고 있다.

MBE 성장법은 손쉽게 산화갈륨 에피택시를 구현할 수 있어 최초로 전력반도체 소자 제작에 필요한 수준까지 도달한 결과를 발표하였다.

Mist-CVD 성장법은 저렴한 비용으로 다양한 구조를 성장할 수 있으며, 성장된 에피 웨이퍼의 결정질이 우수하며, 최근에는 일본 Flosfia 社에서 Mist-CVD 방법으로 성장한 4인치 사파이어 기판상에 성장된 헤테로 에피 기술과 방열특성의 단점을 극복하기 위하여 n형 Ga2O3 층과 n+형 Ga2O3 층이 있는 얇은 채널층만 리프트-오프(lift-off) 하고 Ti/Au 금속전극에 전사하고 Pt/Ti/Au 전극을 형성하여 SBD를 제작하였다. 제작한 SBD의 온-저항(on-resistance) 특성은 0.1mΩ·cm2로서 SBD 전력반도체 가운데 우수한 결과를 발표하였다[23].

일본 교토대학에서는 Mist-CVD 방법을 이용한 산화갈륨 에피 성장기술을 최초로 발표하였고, 산화갈륨 소재를 이용한 UV 검출기 소자 성능을 발표하였다. 또한, 산화갈륨 단결정 기판을 이용한 β-Ga2O3 에피 성장기술과 사파이어 기판을 이용한 α-Ga2O3 에피 성장기술을 최초로 보고하였고, In/Al/Ga 원소를 이용한 밴드갭 엔지니어링이 가능한 에피 성장기술에 대한 연구를 지속적으로 진행하고 있다.

HVPE 성장법은 고품위의 에피의 고속성장에 적합한 기술로 상대적으로 저렴한 비용으로 다양한 에피층의 성장이 가능하며, 빠른 성장 속도와 낮은 유지비 및 장비 가격으로 인하여 후막 산화갈륨 에피성장에 효과적일 것으로 기대된다. 최근 몇몇 연구 그룹에서 HVPE 성장법을 통해 1× 1014/cm3 정도까지도 캐리어 농도를 조절 가능한 연구 결과들을 발표하고 있어 전력반도체 구현에 필수적인 낮은 도핑농도를 확보하려는 연구가 진척을 보이고 있다.

이처럼 산화갈륨 UWBG 반도체 단결정 벌크 성장과 에피택시 기술 분야는 일본 중심의 글로벌 초기 단계이므로 국내에서도 산화갈륨 단결정 벌크 및 에피 소재에 관한 연구개발을 통하여 차세대 UWBG 반도체 기술의 선점이 필요하다.

산화갈륨 전자소자의 공정기술은 아직까지는 초기 단계 수준으로 기술 성숙도가 낮다. SBD의 경우, 일본 Tamura 社에서 2012년 최초 1.4μ m n형 표동(drift) 층에서 100V 항복전압, 2mΩ·cm2 온-저항 및 1.7V의 순방향 전압(200A/cm2 기준)을 갖는 수직형 SBD를 개발하였고, 2013년 FZ 방법으로 성장시킨 UID 산화갈륨 기판을 이용한 SBD를 개발하여 150V 항복전압과 4.3mΩ·cm2 온-저항을 달성하였다.

2016년 일본 NICT에서 HVPE 기술을 이용하여 주석(Sn)으로 도핑된 n+형 β-Ga2O3(001) 에피 웨이퍼에 7μ m의 두께를 갖는 실리콘으로 도핑된 n-형 Ga2O3 (001) 표동층을 사용하고 Ti/Au 캐소드를 주석(Sn)으로 도핑된 n+형 β-Ga2O3(001) 에피 기판 바닥에 형성하고 Pt/Ti/Au 애노드를 n-형 Ga2O3(001) 표동층 위에 형성하면서 300nm의 SiO2를 이용하여 필드 플레이트 구조를 갖도록 하여, 5.1mΩ·cm2 의 온-저항과 1,076V의 높은 항복 전압 특성을 발표하였다[24].

2018년 미국 플로리다 대학에서는 Tamura 社의 HVPE 기술을 이용하여, 주석으로 도핑된 650μ m β-Ga2O3 기판에 2× 1016/cm3 농도로 성장한 20μ m 두께의 β-Ga2O3 에피층을 다시 10μ m로 CMP하여 Ni(20nm)/Au(80nm)로 쇼트키(Schottky) 전극을 형성하고 주석으로 도핑된 650μ m β-Ga2O3 기판에 Ti(20nm)/Au(80nm)로 캐소드 전극을 형성하여 제작한 결과, 0.25mΩ·cm2의 온-저항과 항복전압 2,300V급으로 최고의 연구결과를 발표하였다. 항복전계는 1.15MV/cm이며 전력성능지수(power figure of merit)는 약 21.2MW·cm2로 평가되었다[25].

일본은 향후 2~3년 이내에 산화갈륨 SBD 양산을 목표로 하고 있으며 FET 기술은 상대적으로 기술 성숙도가 더 낮은 편이다. MESFET의 경우 2012년 마그네슘(Mg)-도핑된 반절연 β-Ga2O3 기판(010) 상에 주석(Sn)-도핑된 300nm 두께의 n-형 Ga2O3 채널층 위에 Ti(20nm)/Au(230nm)를 이용하여 드레인 전극과 소스 전극을 형성하고 Pt(15nm)/Ti(5nm)/Au(250nm)를 이용하여 게이트 전극을 형성하여 드레인 전극과 소스 전극 사이의 거리 20μ m, 게이트 길이 4μ m, 드레인 전극의 직경 200μ m로 제작한 결과, 게이트 전압 +2V, 드레인 전압 40V에서 15mA를 얻었고, 트랜스컨덕턴스는 1.4mS, 온오프 전류비는 약 5× 103, 항복전압 257V의 최초 FET 소자를 발표하였다[26].

2013년 일본 NICT, Tamura 社, Koha 社에서는 주석으로 도핑된 채널에 산화알루미늄(Al2O3) 게이트 절연막을 사용한 MOSFET으로 항복전압 370V, 1010의 온/오프 전류비를 발표하였고, 동년도에 철(Fe) 도핑된 반절연 Ga2O3(010) 기판 위에 3× 1019/cm3 농도의 실리콘 이온주입 공정으로 300nm 두께의 n-형 Ga2O3 채널층을 형성하고 소스와 드레인의 오믹 접촉을 위해 3× 1019/cm3 농도의 실리콘을 150nm 깊이로 이온주입하고 20nm Al2O3로 플라즈마를 통한 ALD한 후 게이트를 형성하여 제작하였다. 제작한 후 특성을 측정한 결과 415V의 항복전압을 가지며 250℃ 의 고온에서도 동작하는 MOSFET을 발표하였다[27].

일본 NICT에서는 철(Fe)-도핑된 β-Ga2O3 반절연 기판에 Si+ 이온주입된 채널과 소오스, 드레인에 n+ 이온주입한 옴익 전극을 갖는 구조를 이용하고, 항복전압 향상을 위한 필드 플레이트 게이트 구조를 갖는 750V 급 MOSFET를 발표하였다. 특히 중요한 고온 특성은 상온(25℃ )에서 온오프 전류비가 약 109 에서 300℃ 고온에서도 약 103 정도를 잘 유지하고 있어 산화갈륨 MOSFET의 고온에서 안정적인 특성을 보였다[28].

최근에는 미국 버팔로 대학 및 공군 연구소 등에서 증가형 모드로 구동되는 MOSFET을 발표하였다. 증가형 모드는 안전한 전력소자의 동작과 시스템의 간편화 및 안정화를 위해 매우 중요하다. 게이트 전극 아래의 채널층을 얇게 성장하거나 좁게 형성하여 n형 채널을 완전하게 공핍시켜 만든다[29]. Purdue 대학에서는 50~150nm 두께의 나노-멤브레인을 이용하여 공핍형 모드와 증가형 모드의 전류밀도 개선 연구를 수행하여 온오프 전류비가 약 1010, 트랜스컨덕턴스가 약 3mS/mm, 최대 0.6A/mm 우수한 결과를 발표하였다[30].

이러한 구조와는 달리 일본 NICT에서는 1.2μ m 두께의 UID 채널을 이용하여 초창기 실리콘 MOSFET 구조와 유사한 개념의 증가형 모드에 관한 연구도 진행되고 있다. 뿐만 아니라 미국 NRL에서는 산화하프늄(HfO2) 게이트 절연막을 이용한 MOSFET 소자 연구를 하고 있다.

산화갈륨은 초광대역 밴드갭으로 극한환경에 대한 내환경 특성이 우수한 장점을 가진다. 미국 플로리다 대학과 NRL에서는 β-Ga2O3 광검출기에 5MeV 양성자(proton)의 고에너지 입자를 도즈(dose)에 대한 영향을 조사하였으며, 미국 플로리다 대학과 Tamura 社에서는 쇼트키 다이오드에 1.5MeV 전자의 조사 영향을 발표하였다[31]. 1.8× 1015/cm2 표면 농도의 전자를 조사할 경우 누설전류와 턴-온(turn-on) 전압의 변화가 거의 없었으나, 조사되는 전자의 농도를 1.4× 1016/cm2 이상으로 증가시키면 임계전압의 증가와 최대 전류의 감소가 일어났다[25].

국내의 경우 산화갈륨 전력소자 연구 진행이 거의 없으나, 2016년부터 홍익대에서는 기초연구를 수행 중이며, 183V의 항복전압과 온-저항 1.3mΩ·cm2 정도를 갖는 SBD 결과를 발표하였다. 특히 2017년 산업부 지원으로 전략적 핵심소재 기술개발 사업을 통하여 α-Ga2O3 및 β-Ga2O3 에피소재 개발과 함께 이를 이용한 1,000V급 전력 SBD와 전력 FET 소자 기술을 개발하고 있다. 에피성장 방법은 앞서 언급한 Mist-CVD, MBE, HVPE 3가지를 연구개발 중이며, 최적의 에피 성장 기술도 개발 중이다.

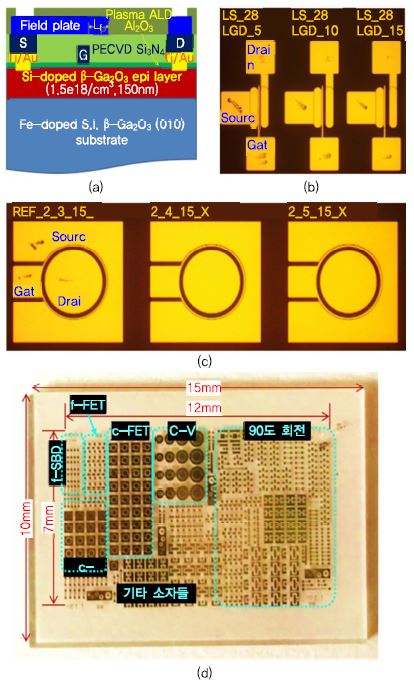

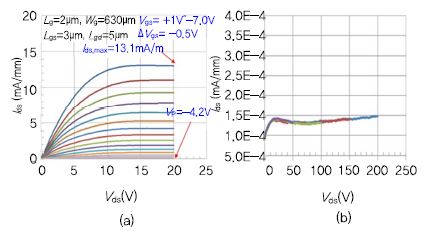

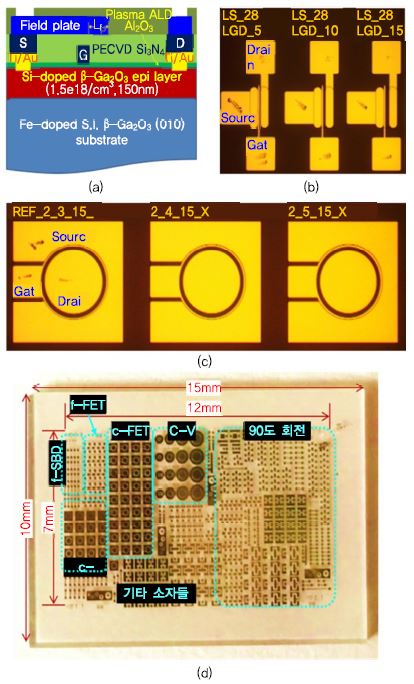

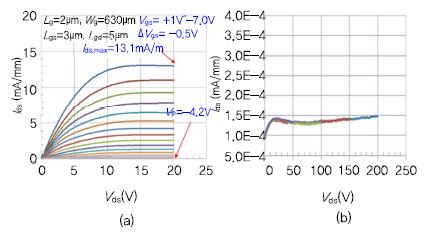

2018년부터 ETRI에서는 국내 최초로 철(Fe)이 도핑된 반절연 기판상에 β-Ga2O3가 에피 성장된 10mm× 15mm 크기의 조각 웨이퍼를 사용하여 (그림 8)과 같이 β-Ga2O3 MESFET과 β-Ga2O3 MOSFET 개발하여 그 결과를 2018년 한국전기전자재료학회 하계학술대회에 발표하였다[32]. (그림 9)와 같이 전류밀도는 10~13mA/mm 정도였으며, 소자는 보유 계측장비의 한계인 200V에서도 안정적으로 동작하여 항복전압이 200V 이상으로 판단된다.

Ⅲ. 결론

본 고에서는 극한 환경용 반도체 기술 중에서 다이아몬드 반도체 기술과 산화갈륨 반도체 기술을 중심으로 주요 이슈 및 기판, 에피, 소자에 대한 연구 동향과 기술 개발 현황을 살펴보았다.

극한 환경용 반도체는 UWBG 반도체의 물성으로 인하여, 기존 실리콘 및 화합물 반도체 등으로 구현된 시스템에 비해 고온동작이 가능하며 큰 방사능 저항도를 갖고 쿨링 시스템이 필요없거나 현저히 줄일 수 있으며 시스템의 크기를 획기적으로 줄일 수 있고 고전압 및 고전력 동작이 가능한 특징을 갖는다.

극한 환경용 반도체 기술 중에서 다이아몬드 반도체기술은 재료적인 특성상 수십 년의 연구 역사에 비해 비교적 더딘 발전을 하고 있으나 지속적인 연구개발을 통해 에피 기술과 다이아몬드 합성기술을 통한 대구경 기판 제작의 한계와 가격문제를 극복하고, n형 도핑 기술이 개발되는 시점에는 다이아몬드 반도체 관련시장은 매우 폭발적으로 증가할 것이다. 산화갈륨 반도체 기술은 다이아몬드 반도체 연구개발 역사에 비해 매우 짧지만 빠른 연구개발 결과물들이 쏟아지고 있는 상황이다. 물론 아직까지 해결해야 할 p형 도핑, 전류 밀도, 열전도도를 개선시키는 방법 등에 대한 연구가 지속적으로 필요한 것도 사실이다. 산화갈륨 반도체 기판은 WBG 반도체인 탄화규소 또는 질화갈륨 반도체 기판에 비해 6~8인치의 경우 SiC 대비 약 1/10, GaN 대비 약 1/100 수준이다. 따라서 고품질 및 저가의 산화갈륨 반도체 기판을 이용할 경우 고효율, 고신뢰성 특성을 갖는 고성능 모듈 및 시스템을 더 작고 값싸게 만들 수 있다. 위와 같은 특성들로 인하여 다이아몬드 반도체 기술은 고가이지만 고성능을 요구하는 극한 환경 시장에 응용할 수 있으며, 관련 시장으로는 초고전력 스마트 그리드(smart grid), 철도수송, 풍력발전터빈, 선박, 산업용 모터, HEV/EV 등에 응용이 가능하다. 또한 효과적인 열방출 응용을 위한 나노결정 다이아몬드 캡핑 기술은 고전력 산업용 모터, HEV/EV, 태양광발전 인버터, 통신 시스템 등에 응용이 가능하다. 비교적 저렴하게 제작이 가능한 산화갈륨 반도체 기술은 저가격·저전력 산업용 모터, 태양광발전 인버터, 통신 시스템 등에 응용이 가능하다.

따라서, 향후 극한 환경용 반도체 기술에 대해 체계적이고 지속적인 연구개발이 이뤄져서, 관련 기술 경쟁력을 확보하고 해당 거대 시장을 선점하길 기대한다.

약어 정리

AI

Artificial Intelligence

BJT

Bipolar Junction Transistor

CMP

Chemical Mechanical Polishing

DC-PACVD

Direct Current Plasma Assisted Chemical Vapor Deposition

EFG

Edge-defined Film Growth

EV

Electric Vehicle

FET

Field Effect Transistor

FZ

Floating Zone

HEMT

High Electron Mobility Transistor

HEV

Hybrid Electric Vehicle

HFCVD

Hot Filament Chemical Vapor Deposition

HTCVD

High-Temperature Chemical Vapor Deposition

HTHP

High-Temperature and High-Pressure

HVPE

Hydride Vapor Phase Epitaxy

IoT

Internet of Things

UWBG

Ultra-Wide Band Gap

MBE

Molecular Beam Epitaxy

Mist-CVD

Mist Chemical Vapor Deposition

MOSFET

Metal Oxide Semiconductor Field Effect Transistor

MWCVD

Microwave Plasma Chemical Vapor Deposition

NASA

National Aeronautics and Space Administration

NCD

Nano-Crystalline Diamond

NICT

National Institute of Information and Communication Technology

NRL

Naval Research Lab.

SBD

Schottky Barrier Diode

SJ

Shallow Junction

UID

Unintentionally Doped

UV

Ultra-Violet

WBG

Wide Bandgap

P.N. Volpe et al., “Extreme Dielectric Strength in Boron Doped Homo-Epitaxial Diamond,” Appl. Phys. Lett., vol. 97, 2010, Article no. 223501.

A. Traore et al., “Zr/oxidized Diamond Interface for High Power Schottky Diodes,” Appl. Phys. Lett., vol. 104, 2014, Article no. 052105.

H. Umezawa et al., “High Temperature Application of Diamond Power Device,” Diamond Related Mater., vol. 24, 2012, pp. 201-205.

R. Kumaresan et al., “Vertical Structure Schottky Barrier Diode Fabrication Using Insulating Diamond Substrate,” Diamond Related Mater., vol. 19, no. 10, 2010, pp. 1324–1329.

V.S. Bormashov et al., “Thin Large Area Vertical Schottky Barrier Diamond Diodes with Low On-resistance Made by Ion-Beam Assisted Lift-off Technique,” Diamond Related Mater., vol. 75, 2017, pp. 78-84.

T. Makino et al., “Diamond Schottky-pn Diode without Trade-off Relationship Between On-resistance and Blocking Voltage,” Phys. Status Solidi A, vol. 207, no. 9, 2010, pp. 2105-2109.

M. Brezeanu et al., “On-State Behavior of Diamond M-I-P Structure,” IEEE Semiconductor Conf., Sinaia, Romania, Sept. 27-29, 2006, pp. 311-314.

S.J. Rashid et al., “Numerical Parameterization of Chemical-Vapor-Deposited (CVD) Single-Crystal Diamond for Device Simulation and Analysis,” IEEE Trans. Electron Dev., vol. 55, no. 10, 2008, pp. 2744-2756.

鈴木 真理子, “高耐圧ダイヤモンドpinダイオード : 卓越した材料ポテンシャルからデバイス実現に向けて,” 応用物理, vol. 85, no. 3, 2016, pp. 218-222.

H. Umezawa et al., “Characterization of X-Ray Radiation Hardness of Diamond Schottky Barrier Diode and Metal-semiconductor Field-Effect-Transistor,” Int. Sypm. Power. Semiconductor. Dev. IC’s, Sapporo, Japan, 2017, pp. 379-382.

H. Umezawa et al., “Diamond Metal-Semiconductor Field-Effect Transistor with Breakdown Voltage Over 1.5 kV,” IEEE Electron Dev. Lett., vol. 35, no. 11, 2014, pp.1112-1114.

T. Iwasaki et al., “High-Temperature Operation of Diamond Junction Field-Effect Transistors with Lateral p-n Junctions,” IEEE Electron Dev. Lett., vol. 34, no. 9, 2013,pp. 1175-1177.

Y. Kitabayashi et al., “Normally-Off C-H Diamond MOSFETs with Partial C-O Channel Achieving 2-kV Breakdown Voltage,” IEEE Electron Dev. Lett., vol. 38, no. 3, Mar. 2017, pp. 363-366.

H. Kawarada et al., “Durability-Enhanced Two-Dimensional Hole Gas of C-H Diamond Surface for Complementary Power Inverter Applications,” Sci. Rep., vol. 7, 2017, Article no. 42368.

K. Hirama et al., “Diamond Field-Effect Transistors with 1.3 A/mm Drain Current Density by Al2O3 Passivation Layer,” Jpn. J. Appl. Phys., vol. 51, no. 9, 2012, pp. 090112:1-090112:5.

M. Kasu, “Diamond Field-Effect Transistors as Microwave Power Amplifiers,” NTT Techn. Rev., vol. 8, no. 8, Aug. 2010, pp. 1-5.

T.J. Anderson et al., “Advanced in Diamond Integration for Thermal Management in GaN Power HEMTs,” ECS Trans., vol. 64, no. 7, 2014, pp. 185-190.

T.J. Anderson et al., “Profiling the Temperature Distribution in AlGaN/GaN HEMTs with Nanocrystalline Diamond Heat Spreading Layers,” CS MANTECH Conf., Boston, MA, USA, Apr. 23-26, 2012, pp. 1-3.

X.-F. Zheng et al., “Influence of the Diamond Layer on the Electrical Characteristics of AlGaN/GaN High-Electron-Mobility Transistors,” China Phys. Lett., vol. 34, no. 2, 2017, pp. 027301:1-027301:4.

A. Kuramata et al., “High-Quality β-Ga2O3 Single Crystals Grown by Edge-Defined Film-Fed Growth,” Jpn. J. Appl. Phys., vol. 55, no. 12, 2016, pp. 1202A2:1-1202A2:6.

Z. Galazka et al., “On the Bulk β-Ga2O3 Single Crystals Grown by the Czochralski Method,” J. Cryst. Growth, vol. 404, 2014, pp. 184-191.

E.G. Víllora et al., “Large-size β-Ga2O3 single crystals and wafers,” J. Cryst. Growth, vol. 270, no. 3-4, 2004, pp. 420-426.

M. Oda et al., “Schottky Barrier Diodes of Corundum-Structured Gallium Oxide Showing On-resistance of 0.1mΩcm2 Grown by Mist Epitaxy,” Appl. Phys. Exp., vol. 9, no. 2, 2016, pp. 021101:1-021101:3.

K. Konishi et al., “1-kV Vertical Ga2O3 Field-Plated Schottky Barrier Diodes,” Appl. Phys. Lett., vol. 110, 2017, pp. 103506:1-103506:4.

J. Yang et al., “1.5 MeV Electron Irradiation Damage in β-Ga2O3 Vertical Rectifiers,” J. Vacuum Sci. Technol. B, vol. 35, no. 3, 2017, pp. 031208:1-031208:4.

M. Higashiwaki et al., “Gallium Oxide(Ga2O3) Metal-Semiconductor Field-Effect Transistors on Single-Crystal-Ga2O3(010) Substrates,” Appl. Phys. Lett., vol. 100, 2012, pp. 013504:1-013504:3.

M. Higashiwaki et al., “Depletion-Mode Ga2O3 MOSFETs on β-Ga2O3(010) Substrates with Si-ion-Implanted Channel and Contacts,” IEEE Int. Electron Dev. Meeting, Washington, DC, USA, Dec. 9-11, 2013, pp. 1-4.

M. Higashiwaki et al., “Field-Plated Ga2O3 MOSFETs with a Breakdown Voltage of over 750 V,” IEEE Electron Dev. Lett., vol. 37, no. 2, 2016, pp. 212-215.

K. Zeng et al., “Interface State Density in Atomic Layer Deposited SiO2/β-Ga2O3(201) MOSCAPs,” IEEE Electron Device Lett., vol. 37, no. 7, 2016, pp. 906-909.

H. Zhou et al., “High-Performance Depletion/ Enhancement-Mode β-Ga2O3 on Insulator(GOOI) Field-Effect Transistors with Record Drain Currents of 600/450 mA/mm,” IEEE Electron Device Lett., vol. 38, no. 1, 2017, pp. 103-106.

S. Ahn et al., “Effect of 5 MeV Proton Irradiation Damage on Performance of β-Ga2O3 Photodetectors,” J. Vac. Sci. Tech. B, vol. 34, no. 4, 2016, pp. 041213:1-041213:5.

(그림 4)

다이아몬드 반도체 FET 구조 및 사진

[출처] Reprinted from M. Kasu, “Diamond Field-Effect Transistors as Microwave Power Amplifiers,” NTT Techn. Rev., vol. 8, no. 8, Aug. 2010, pp. 1-5.

(그림 6)

다이아몬드 반도체 FET의 적외선 열화상 비교 사진

[출처] Reprinted from M. Kasu, “Diamond Field-Effect Transistors as Microwave Power Amplifiers,” NTT Techn. Rev., vol. 8, no. 8, Aug. 2010, pp. 1-5.

(그림 7)

다이아몬드 반도체 FET의 Class A 동작시 1GHz에서 RF 특성

[출처] Reprinted from M. Kasu, “Diamond Field-Effect Transistors as Microwave Power Amplifiers,” NTT Techn. Rev., vol. 8, no. 8, Aug. 2010, pp. 1-5.

- Sign Up

- 전자통신동향분석 이메일 전자저널 구독을 원하시는 경우 정확한 이메일 주소를 입력하시기 바랍니다.