다차원 이종 복합 디바이스 인터커넥션 기술 - 레이저 기반 접합 기술

Laser-Assisted Bonding Technology for Interconnections of Multidimensional Heterogeneous Devices

- 저자

-

최광성ICT소재연구그룹 kschoi@etri.re.kr 문석환ICT소재연구그룹 shmoon@etri.re.kr 엄용성ICT소재연구그룹 yseom@etri.re.kr

- 권호

- 33권 6호 (통권 174)

- 논문구분

- 최신 반도체, 하드웨어 기술 동향 특집

- 페이지

- 50-57

- 발행일자

- 2018.12.21

- DOI

- 10.22648/ETRI.2018.J.330606

본 저작물은 공공누리 제4유형: 출처표시 + 상업적이용금지 + 변경금지 조건에 따라 이용할 수 있습니다.

본 저작물은 공공누리 제4유형: 출처표시 + 상업적이용금지 + 변경금지 조건에 따라 이용할 수 있습니다.- 초록

- As devices have evolved, traditional flip chip bonding and recently commercialized thermocompression bonding techniques have been limited. Laser-assisted bonding is attracting attention as a technology that satisfies both the requirements of mass production and the yield enhancement of advanced packaging interconnections, which are weak points of these bonding technologies. The laser-assisted bonding technique can be applied not only to a two-dimensional bonding but also to a three-dimensional stacked structure, and can be applied to various types of device bonding such as electronic devices; display devices, e.g., LEDs; and sensors.

Share

Ⅰ. 서론: 디바이스 인터커넥션 기술

팹에서 디바이스가 완성되면 이것을 외부와 연결하는 인터커넥션이 필요하다. 기존에 사용되던 대표적 기술은 (그림 1)의 플립 칩 인터커넥션 이다. 플립 칩은 그 이름에서 나타나듯이 디바이스 상에 소자가 있는 면이 아래로 향해 있는 것이 특징이다. 이 기술의 장점은 디바이스 면적 전체를 인터커넥션에 사용할 수 있다는 점이다. 즉, 디바이스 상 소자가 있는 면에 N×M 배열로 인터커넥션에 필요한 전극을 형성하면 많은 수의 인터커넥션을 만들 수 있다. 종래의 디바이스 가장자리 부분에서만 인터커넥션을 할 수 있었던 와이어 본딩 기술에 비해 인터커넥션 수를 다량으로 제공할 수 있는 기술이다.

(그림 1)

플립 칩 인터커넥션

[출처] Reprinted from K.-S Choi et al., “Characterization of 3D Stacked High Resistivity Si Interposers with Polymer TSV liners for 3D RF Module,” IEEE Electron. Components Technol. Conf., 2015, pp. 928-933.

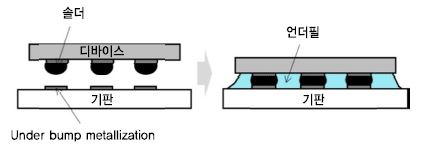

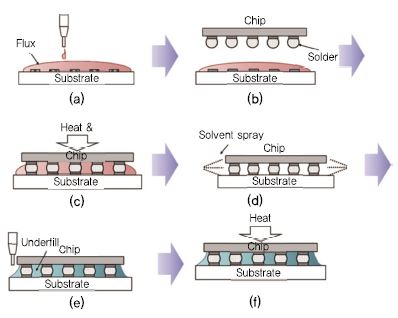

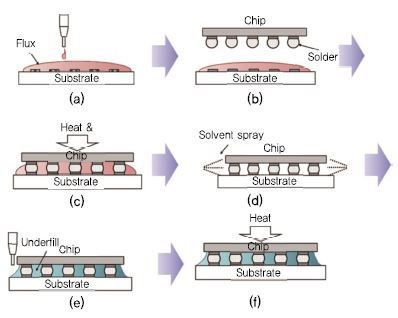

플립 칩 인터커넥션 기술의 공정은 (그림 2)에 나와 있는 바와 같이 여러 단계의 공정으로 이루어져 있다. 플립 칩에서 사용되는 일반적인 접합 소재는 솔더이다. 솔더의 특징 중 하나는 쉽게 산화가 된다는 점이고 일단 솔더의 산화막이 형성되면 산화막의 높은 융점으로 인해 접합이 쉽게 이루어지지 않는다. 이러한 산화막을 제거하는 물질이 플럭스이다. 플립 칩 인터커넥션 공정의 첫 번째는 플럭스를 디바이스 상 솔더 부분에 도포하거나 혹은 기판 상에 있는 UBM(Under Bump Metallization)에 도포하는 것이다. 그 이후에 디바이스와 기판을 정렬하여 접합한 이후 리플로우 공정을 거친다. 리플로우 공정의 온도 프로파일은 솔더 소재와 앞서 적용된 플럭스에 의해 결정된다. 일반적으로 Sn3.5Ag 혹은 Sn3.0Ag0.5Cu 솔더의 경우 최대 공정 온도는 약 260℃ 내외이다. 리플로우 공정 동안 앞서 도포한 플럭스가 솔더의 산화막을 제거하고 솔더와 UBM 사이에 금속 간 화합물이 형성된다. 리플로우 공정 이후에 플럭스 잔사가 남고 이를 세척 공정을 통해 제거한다. 이는 플럭스 잔사가 사용 중에 부식을 일으키거나 이후에 진행되는 언더필 공정 동안 언더필 안에 공극(void)를 발생시킬 수 있는 원인이 되기 때문이다. 경우에 따라서는 무세척 플럭스가 사용되기도 하나 높은 신뢰성이 요구되는 디바이스를 적용할 때는 세척 공정을 반드시 적용하는 것이 일반적이다.

(그림 2)

플립 칩 인터커넥션 공정도: (a) Flux dispense, (b) alignment, (c) reflow, (d) flux residue cleaning, (e) capillary underfill, (f) underfill curing

Reprinted from K.-S Choi et al., “Maskless, Fine-Pitch, Lead-Free Solder Bumping Technology for 3D Integration,” Semicon Korea, 2014.

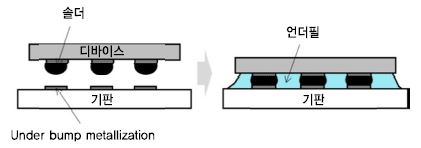

솔더는 무른 소재이므로 인터커넥션 소재로서 기계적인 안정성이 좋지 않다. 특히 디바이스와 기판 사이의 기계적인 특성이 다르기 때문에, 공정 중 혹은 사용 중에 쉽게 파괴될 수 있다. 플립 칩 인터커넥션의 기계적인 신뢰성을 증가시키기 위해 적용되는 소재가 언더필이다. 언더필은 모세관 현상을 이용하여 디바이스와 기판 사이에 도포되며 그 이후 경화 공정을 거쳐 전체 공정이 완성된다.

최근 이러한 플립 칩 인터커넥션 공정에 매우 중요한 변화가 발생하였고 이를 G. Bartlett은 [1]에서 설명하였다. 가장 중요한 변화의 요인은 플립 칩 인터커넥션 숫자의 증가를 들 수 있다. 이는 디바이스로부터 많은 양의 데이터를 주고받기 위한 방편으로 이를 위해서는 인터커넥션 사이의 간격 즉 피치를 좁히는 것 외에는 다른 물리적인 해결책이 없다. 예를 들어 일반적인 메모리의 경우 I/O의 숫자는 보통 100개 정도에 불과하다. 그러나 인공지능에 적용되는 HBM(High Bandwidth Memory)의 경우 I/O의 숫자가 수만 개에 이른다. 이에 따라 제한된 디바이스 면적에 이러한 다량의 I/O를 형성하기 위해서는 인터커넥션 범프 피치를 좁히는 것 외에는 방법이 없다.

피치가 줄어들게 되면 리플로우 공정 중에 디바이스가 이동하거나 혹은 디바이스나 기판이 자체의 특성으로 인해 휨(warpage)이 있는 경우에는 인터커넥션의 불량이 발생할 확률이 매우 높다. 이러한 문제점을 해결하기 위해 제안된 인터커넥션 기술이 열 압착(Thermo-compression) 접합 기술이다. 열 압착 접합 기술이 적용되는 기준은 디바이스 크기에 따라 다르다. 큰 SoC 칩의 경우 (그림 3)에서 나타난 바와 같이 범프 피치 100μm가 기준이 될 수 있지만, 메모리의 경우 범프 피치 55μm의 경우에서도 리플로우 공정이 가능하다. 이는 메모리 디바이스의 크기가 SoC 칩에 비해 작기 때문에 가능하다.

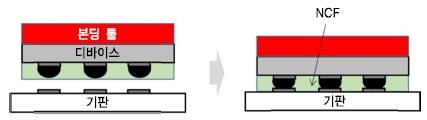

(그림 3)는 열 압착 인터커넥션 공정도를 보여준다. (그림 2)의 일반적인 플립 칩 인터커넥션 공정과 가장 큰 차이점은 디바이스를 하나씩 개별로 pick & place하여 접합한다는 점이다. 이로 인해 양산성이 매우 떨어지는 단점이 있다. 즉, 기존의 플립 칩 인터커넥션 공정에서는 기판 상에 다량에 디바이스를 짧은 시간에 올려놓고 한꺼번에 리플로우하여 양산성을 확보하였지만, 열 압착 공정에서는 이러한 것이 불가능하다. 이는 불량을 줄이기 위함에서 오는 피할 수 없는 단점이다. 이러한 문제를 해결하기 위해 장비 하나에 여러 개의 본딩 툴을 제작하여 양산성을 높이는 기술을 개발하고 있다[2], [3]. 그럼에도 불구하고 접합에 필요한 사이클 시간이 십 초 이상 소요됨에 따라 양산성이 일반적인 플립 칩 인터커넥션 기술을 따라가지 못하고 있는 실정이다. 양산성을 확보하면서 동시에 수율을 높일 수 있는 인터커넥션 기술 개발이 필요한 이유이다.

또 하나의 특이한 점은 NCF(Non-Conductive Film)가 사용된다는 점이다. 경우에 따라서는 페이스트 형태인 NCP(Non-Conductive Paste)가 사용될 수도 있다. 이들 소재의 특징은 플럭스와 언더필의 역할을 동시에 수행한다는 점이다. 따라서 공정이 (그림 3)에서 보는 바와 같이 매우 간단해진다. 이 공정 이후에 NCF 혹은 NCP의 경화를 위한 포스트 경화 공정이 필요할 수도 있다. NCF와 NCP 소재의 차이는 도포되는 부피를 정확하게 제어할 수 있느냐가 가장 중요하다. NCP의 경우 일반적으로 디스펜서에 의해 도포되는 데 양산 조건하에서 부피를 정확하게 제어하는 것이 매우 어렵다. 따라서 TSV(Through Silicon Via)와 같이 부피 제어가 매우 중요한 분야에서는 다소 가격이 비싸지만, NCF가 적용된다.

레이저 기반 접합 기술은 두 가지 인터커넥션 기술 즉, 플립 칩 및 열 압착 인터커넥션 기술의 단점을 보완하기 위해 제안[4]되었으며 IR(Infra-Red) 레이저가 사용된다. 이 기술의 근원을 살펴보면 약 20여 년 전에 IR 리플로우 기술이 검토되었던 시기로 거슬러 올라간다. 당시에 현재 적용되고 있는 열풍 방식과 더불어 IR 리플로우 방식이 검토되었다. IR 리플로우는 몇 가지 장점이 있었지만, 균일하지 않은 온도 구배로 인해 대량생산에는 접합하지 않은 기술로 판명되었던 기술이다. 레이저 기반 접합 기술은 그 당시 거론되었던 단점을 보완하여 나온 기술이라고 생각해도 무방하다고 생각하며 연구(research)의 의미 즉, 다시 찾아본다는 의미를 실질적으로 보여주는 사례라는 생각을 하게 한다.

[4]는 레이저 기반 접합 기술의 원리와 특성을 보여준다. 레이저 기반 접합 기술은 레이저가 디바이스에 조사되면 그중 일부분이 열 에너지의 형태로 흡수된다. 흡수된 열 에너지로 인해 디바이스의 온도가 올라가며 열 전도 현상으로 인해 접합부의 온도 역시 올라가게 된다. 적절한 조건에서 접합부의 온도가 접합 공정에 필요한 온도까지 상승한다. 이때 기판의 온도는 접합부의 온도에 비해 낮게 유지될 수 있다. 일반적으로 디바이스의 열 팽창 계수는 낮고 기판의 열 팽창 계수는 높다. 상기의 레이저 접합의 원리와 두 부품의 서로 다른 열 팽창 계수의 차이로 인해 레이저 접합의 장점이 부각될 수 있다. 접합 공정 동안 열 팽창 계수가 낮은 디바이스는 상대적으로 높은 온도에 머물러 있어 팽창하게 되고 열 팽창 계수가 높은 기판은 상대적으로 낮은 온도에 머물러 있기 때문에 열 팽창을 작게 한다는 점이다. 다시 말해 높이 방향으로 온도 구배가 발생하고 이러한 온도 구배로 인해 그동안 접합 공정에서 발생하였던 불량을 혁신적으로 줄일 수 있다는 점이 레이저 기반 접합 공정의 장점이다.

또 하나의 장점은 레이저 조사 시간이 매우 짧다는 것이다. 일반적인 플럭스를 적용할 경우 레이저 조사 시간은 1초 이내이고 NCP나 NCF를 적용할 경우 레이저 조사 시간은 5초 이내이다. 기존에 열 압착 공정에서 한계점으로 여겨져 왔던 생산성의 문제를 해결할 수 있는 기술적인 장점을 가지고 있다.

레이저 기반 접합 기술에서 사용되는 레이저는 징일반적인 레이저 빔의 특징인 가우시안 빔의 형태를 보이지 않고 동일 평면에서 레이저 강도가 군일한 빔 즉 균질화된 빔(homogenized beam)을 보여준다. 본론에서는 레이저 기반 접합 기술을 적용한 사례를 살펴보고 소재적인 측면에서 개발 현황을 소개하고자 한다.

Ⅱ. 본론: 레이저 기반 접합 기술

2016년 Amkor Korea는 레이저 기반 접합 기술을 발표하였다. 적용된 제품은 플립 칩이 적용된 BGA(Ball Grid Array) 패키지로, 실리콘 디바이스의 크기가 8×8mm2에서 23×23mm2까지 다양하였고 패드 피치도 30/60μm에서 150μm에 이르기까지 좋은 접합 상태를 유지함을 알 수 있다. Amkor Korea에서는 (그림 2)의 일반적인 플립 칩 인터커넥션 공정 중에서 리플로우 단계만을 레이저 기반 접합 공정으로 대체하는 공정만을 개발하였다. 플럭스는 일반 플럭스를 사용하였다. 레이저 기반 접합 공정을 사용하면 일반적인 리플로우 보다 접합 후 휨이 30μ40% 정도 개선됨을 보고하였다.

2017년 Amkor Korea는 레이저 기반 접합 기술을 매우 얇은 플립 칩 패키지에 적용하였다. 기판은 코어가 없는 기판을 사용하였다. 기판의 접합부는 UBM이 아닌 기판 상의 패턴을 적용하는 것이 특징인 ETS(Embed-ded Trace Substrate)가 사용되었다. 실리콘 디바이스의 크기는 11×11mm2과 9.41×11.02mm2 두 가지가 적용되었고 해당되는 피치는 각각 130μm, 30/60μm였다. 기판의 두께는 각각 0.135mm와 0.093mm였다. 레이저 기반 접합 공정을 적용한 결과 MSL(Moisture Sensitive Level) 시험과 TCB(Temperature Cycle Level B), HTS(High Temperature Storage), 그리고 HAST (High Accelerated Temperature Humidity Stress) 시험을 통과하였다[5].

2018년 대만의 미디어택은 스태츠칩팩과 함께 10nm 데이지 체인이 있는 15×15mm2 fcCSP(flip chip Chip Scale Package)에 레이저 기반 접합 기술을 도입하였다. 이 기술을 도입함으로 양산성이 열 압착 접합 공정에 비해 2배 이상 증가하였다고 발표하였다. 또한, ELK(Extremely Low-k) 손상이 개선됨을 확인하였다[6].

2018년 IBM Research-Zurich는 Complex Materials사, 그리고 Pac TEch사와 함께 레이저를 기반으로 하는 소결 기술을 이용하여 솔더를 사용하지 않고 Cu로만 이루어진 접합 기술을 개발하였다. 적용된 Cu paste는 나노와 마이크로 분말로 이루어져 있고 각각의 분말이 유기 바인더로 덮여 있으며 이들 분말들이 솔벤트에 분산되어 있는 구조이다. 실리콘 기판은 10×10mm2 크기이고 실리콘 칩은 8×8mm2 이었다. Cu 필러의 직경은 50μm였고 피치는 100μm였다. 접합을 위해 블레이드를 이용하여 20μm 두께의 Cu paste를 프린팅하였다. 최대 200W의 레이저가 조사되었다. Carro[7]의 연구에서는 3초 동안 11.6W/mm2의 레이저를 조사하여 접합시킨 접합부의 단면을 확인할 수 있다.

2018년 Universal Instruments 사와 Binghamton 대학은 레이저 기반 접합 공정 후 솔더 접합부의 미세 구조를 분석하였고 이러한 미세 구조가 접합부의 크립 특성, 피로 수명에 대해 미치는 영향을 분석하였다. 레이저 조사 시간이 증가할수록 금속 간 화합물의 두께가 증가하였고 그에 따라 접합부의 전단 응력이 감소하는 것을 관찰하였다. 냉각 시간을 변화하여도 접합부의 전단응력의 변화가 없음을 측정하였고 피로 수명에는 영향을 미치는 것을 관찰하였다[8].

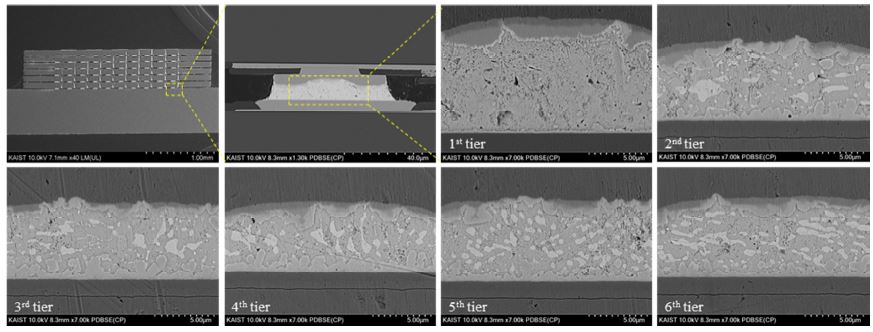

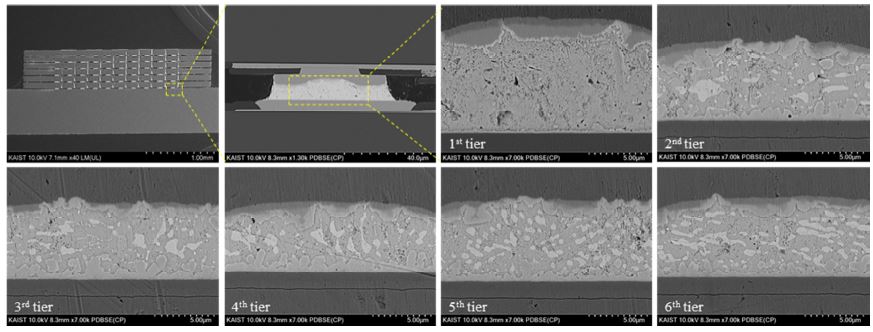

2018년 한국전자통신연구원은 NCP의 일종인 플럭싱언더필을 이용하여 TSV 적층 공정에 레이저 기반 접합 공정을 도입하였다[9]. 플럭싱 언더필 소재의 가장 큰 특징은 일반적으로 NCP 소재에 적용되는 플럭스나 솔벤트를 첨가하지 않고 구성하는 모든 소재를 고분자 기반으로 설계하였다는 것이다. 적층하고자 하는 층에 플럭싱 언더필을 도포하고 상부 TSV 칩을 적층한 후 100W의 레이저를 가하여 6단 TSV 층을 적층하였다. 적층된 각 TSV의 접합부를 단면 SEM으로 관찰한 결과가 (그림 4)에 나타나 있다. 단수가 높아짐에 따라 즉, 레이저를 맞는 횟수가 감소함에 따라 grain이 작음을 알 수 있다. 즉, 접합 공정 횟수가 증가할수록 grain의 크기가 증가한다. 이는 일반적으로 관찰되는 현상으로 표면에너지가 높은 grain boundary를 줄여 전체 시스템의 에너지를 낮추려는 열 역학의 법칙에 따른 것이다. 그 밖에 금속 패드와 솔더 사이에 금속 간 화합물 층 두께 변화는 심하지 않는 것으로 관찰되었다. 일반적으로 금속 간 화합물의 두께가 너무 얇으면 접착력이 약하고 너무 두꺼우면 취성이 강해져서 기계적인 신뢰성이 취약해진다. 일반적인 리플로우 혹은 열 압착의 경우 접합 공정을 반복할수록 금속 간 화합물의 두께가 지나치게 두꺼워지거나 심지어 접합부 전체가 금속 간 화합물로 바뀌는 경우가 있다. 그에 비해 레이저로 적층한 경우에는 이미 적층된 접합부에 가해지는 열 에너지가 상대적으로 작기 때문에 금속 간 화합물의 두께가 그다지 크게 증가하지 않는 것을 알 수 있다.

(그림 4)

[출처] Reprinted from W.A. Braganca Jr. et al., “Collective Laser-Assisted Bonding Process for 3D TSV Integration with NCP,” ETRI J., 2018, Accepted, Korea Open Government Licence (KOGL) Type 4.

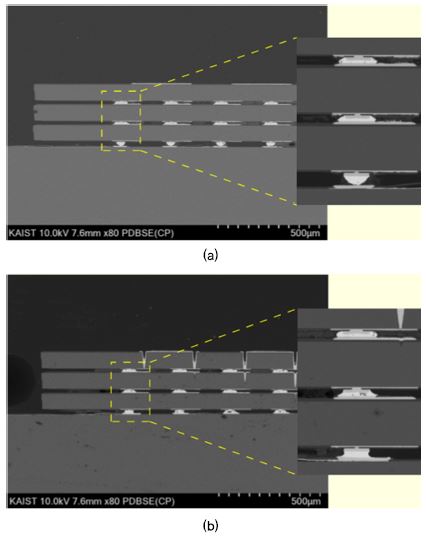

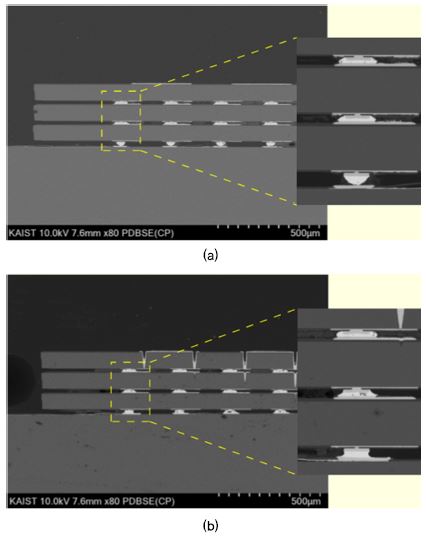

(그림 5)은 TSV 칩에 플럭싱 언더필을 적용하여 3단 적층한 이후 100W의 레이저를 한번 조사하여 3단 적층을 한번에 한 적층 칩의 단면 SEM 사진이다. 3초로 조사한 경우 맨 마지막 층은 접합이 되지 않았고, 5초로 조사해야 세 개 층이 모두 접합됨을 알 수 있다. 이러한 현상은 레이저가 흡수되는 기구와 밀접한 관련이 있다. 레이저는 지수 함수로 흡수된다. 따라서 레이저가 흡수되는 층이 깊어질수록 흡수되는 레이저의 총량이 증가한다. 다시 말해 접합부의 온도가 증가한다. 그러나 어느 정도 깊이 이후에는 흡수되는 레이저의 양이 매우 작게 되어 온도가 더 이상 올라기지 못하게 되는 현상이 발생한다. 이로인해 3초의 100W 레이조 조사는 맨 아래층 접합부의 연결을 확보하는데 충분하지 못했다. 조사 시간을 증가시키면 흡수되는 레이저 에너지 총량이 증가하므로 접합이 이루어진다.

(그림 5)

3단을 적층한 이후 (a) 3초 동안 100W의 레이저를 조사하여 적층한 칩의 단면 SEM (b) 5초 동안 100W의 레이저를 조사하여 적층한 칩의 단면 SEM

[출처] Reprinted from W.A. Braganca Jr. et al., “Collective Laser-Assisted Bonding Process for 3D TSV Integration with NCP,” ETRI J., 2018, Accepted, KOGL Type 4.

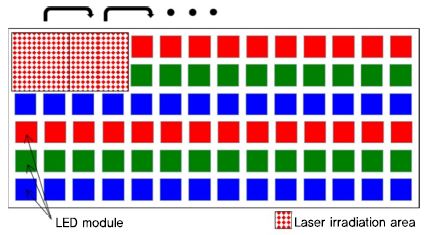

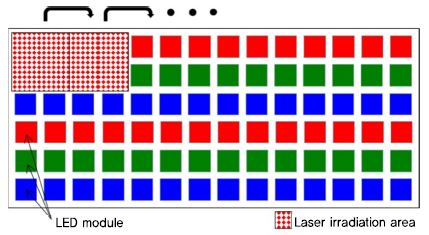

2018년 한국전자통신연구원은 열 변형에 약한 PET 필름 상에 레이저 접합 공정을 적용하여 LED 모듈을 접합한 결과를 발표하였다[10]. 접합에 적용된 소재는 하이브리드 언더필로 앞서 언급된 플럭싱 언더필 소재에 솔더 분말을 첨가한 것으로 여기서는 융점이 139℃인 Sn58Bi 솔더 분말을 사용하였다. PET 필름은 투명함으로 레이저를 거의 흡수하지 않는다. 분광기로 측정한 결과 IR 대역에서 약 3%의 흡수율을 갖는 것으로 측정되었다. 접합 공정 동안 레이저로 인해 PET 기판이 손상되는 우려가 없는 것으로 이러한 장점은 일반적인 리플로우에서는 구현될 수 없는 것이다. 8×20 LED 모듈 배열을 PET 필름에 접합하기 위해 타일링 기법을 사용하였다. (그림 6)에 나타난 바와 같이 일정한 면적의 레이저 조사를 마치 타일을 붙이듯이 주변으로 차례 차례 조사하는 것이다. 이러한 방법을 통해 대면적에도 쉽게 디바이스를 접합할 수 있는 장점이 있다. (그림 7)은 하이브리드 언더필과 레이저를 적용하여 PET 필름에 접합된 8×20 LED 모듈 사진을 보여준다.

Ⅲ. 결론

최근 디바이스 성능의 급격한 발전으로 전통적인 인터커넥션 기술인 플립 칩 인터커넥션 기술이 상업적 적용에 한계를 보이고 있다. 이러한 점을 극복하기 위해 열 압착 인터커넥션 공정이 개발되고 있으나 양산성 측면에서 개선되어야 할 점이 많다. 레이저 기반 접합 공정은 기존의 플립 칩 인터커넥션 및 열 압착 인터커넥션 기술의 약점은 공정 신뢰성 확보와 양산성 확보에 커다란 장점을 제공한다. 이 기술은 fcBGA 및 fcCSP를 위한 집적 기술에 상용화 기술로 적용되기 시작하였고 솔더가 아닌 Cu paste만으로 Cu 필러 칩 접합을 구현하는 공정 개발에 적용되었다. 한국전자통신연구원은 이 기술이 TSV 기반 3차원 접합 기술에 적용될 수 있음을 확인하였고 열에 약한 PET 필름에 LED 모듈을 접합하는데 효과적임을 확인하였다. 레이저 기반 접합에는 전통적인 플럭스가 사용될 수도 있으나 NCP의 일종인 플럭싱 언더필 그리고 하이브리드 언더필이 적용될 경우 공정 단축 등 레이저 기반 접합 기술의 장점이 더욱 부각될 수 있다. 이와 같이 레이저 기반 접합 기술은 2차원의 전통적인 접합 기술뿐만 아니라 3차원의 적층 공정에 적용될 수 있는 유용한 기술이다. 뿐만 아니라 전자 디바이스, LED 등 디스플레이, 센서 등 다양한 이종 디바이스 집적에 적용될 수 있는 기술이다.

용어해설

NCF(Non-Conductive Film) 플럭스와 언더필 역할을 동시에 수행하는 필름 형태의 소재이다. 솔더 범프에 라미네이션되어 열 압착 공정에 적용된다. 부피 제어가 용이하다는 측면에 TSV 삼차원 적층 공정에 적용되고 있다. NCP(Non-Conductive Paste)는 NCF와 동일한 역할을 수행하나 페이스트 형태로 디스펜서를 통해 도포되는 것이 차이점이다. 가격이 NCF에 비해 저렴하다는 장점이 있으나 양산조건 하에서 부피 제어가 쉽지 않다는 단점이 있다.

레이저 기반 접합 기술(LAB: Laser-Assisted Bonding) IR 레이저를 접합하고자 하는 디바이스 전면에 순간적으로 조사하여 접합시키는 공정이다. 레이저가 디바이스에 조사되면 일부가 흡수되어 디바이스 온도를 상승시키고 가열된 디바이스 자체가 접합을 위한 열원의 역할을 한다. 디바이스의 열이 전도 현상에 따라 접합부에 전달되므로 접합부의 온도가 접합에 필요한 온도로 상승된다. 상대적으로 기판의 온도 상승은 높지 않다. 높은 양산성 및 공정 신뢰성이 특징이다.

약어 정리

BGA

Ball Grid Array

ELK

Extremely Low-k

ETS

Embedded Trace Substrate

fcCSP

flip chip Chip Scale Package

HAST

High Accelerated Temperature Humidity Stress

HBM

High Bandwidth Memory

HTS

High Temperature Storage

IR

Infra-Red

LAB

Laser-Assisted Bonding

MSL

Moisture Sensitive Level

NCP

Non-Conductive Paste

NCF

Non-Conductive Film

TCB

Temperature Cycle Level B

TSV

Through Silicon Via

UBM

Under Bump Metallization

G. Bartlett, “Bridging the Gap between Silicon and Packaging,” IEEE Electron. Compon. Technol. Conf., San Diego, CA, USA, May 29–June 1, 2012, Key note speech.

홍성윤, “한미반도체 ‘차세대 3D TSV 필수장비’ 듀얼 TC 본더 출시,” 매일 경제, 2017. 02. 13. http://news.mk.co.kr/newsRead.php?sc=30000001&year=2017&no=101034

K. Seyama et al, “Design and Application of Innovative Multi-Table and Bond Head Drive System on Thermal Compression Bonder with UPH over 2000,” IEEE Electron. Compon. Technol. Conf., San Diego, CA, USA, May 29–June1, 2018, pp. 392-400.

Y. Jung et al., “Development of Next Generation Flip Chip Interconnection Technology Using Homogenized Laser-Assisted Bonding,” IEEE Electron. Compon. Technol. Conf., Las Vegas, NV, USA, May 31-June 3, 2016, pp. 88-94.

C. Kim et al., “Development of Extremely Thin Profile Flip Chip CSP using Laser Assisted Bonding Technology,” IEEE CPMT Symp. Japan (ICSJ), Kyoto, Japan, Nov. 20–22, 2017, pp. 45-49.

C.-Y. Chen et al., “Laser Assisted Bonding Technology Enabling Fine Bump Pitch in Flip Chip Package Assembly,” Electron. Syst.–Integr. Technol. Conf. (ESTC), 2018.

L.D. Carro et al., “Laser Sintering of Dip-Based All-copper Interconnects,” IEEE Electron. Compon. Technol. Conf., San Diego, CA, USA, May 29–June 1, 2018, pp. 279-286.

L.A. Wentlent et al., “Effects of Laser Selective Reflow on Solder Joint Microstructure and Reliability, IEEE Electron. Compon. Technol. Conf., San Diego, CA, USA, May 29–June1, 2018, pp. 425-433.

W.A. Braganca Jr. et al., “Collective Laser-assisted Bonding Process for 3D TSV Integration with NCP, ” ETRI J., 2018, Accepted.

(그림 1)

플립 칩 인터커넥션

[출처] Reprinted from K.-S Choi et al., “Characterization of 3D Stacked High Resistivity Si Interposers with Polymer TSV liners for 3D RF Module,” IEEE Electron. Components Technol. Conf., 2015, pp. 928-933.

(그림 2)

플립 칩 인터커넥션 공정도: (a) Flux dispense, (b) alignment, (c) reflow, (d) flux residue cleaning, (e) capillary underfill, (f) underfill curing

Reprinted from K.-S Choi et al., “Maskless, Fine-Pitch, Lead-Free Solder Bumping Technology for 3D Integration,” Semicon Korea, 2014.

(그림 4)

[출처] Reprinted from W.A. Braganca Jr. et al., “Collective Laser-Assisted Bonding Process for 3D TSV Integration with NCP,” ETRI J., 2018, Accepted, Korea Open Government Licence (KOGL) Type 4.

(그림 5)

3단을 적층한 이후 (a) 3초 동안 100W의 레이저를 조사하여 적층한 칩의 단면 SEM (b) 5초 동안 100W의 레이저를 조사하여 적층한 칩의 단면 SEM

[출처] Reprinted from W.A. Braganca Jr. et al., “Collective Laser-Assisted Bonding Process for 3D TSV Integration with NCP,” ETRI J., 2018, Accepted, KOGL Type 4.

- Sign Up

- 전자통신동향분석 이메일 전자저널 구독을 원하시는 경우 정확한 이메일 주소를 입력하시기 바랍니다.