설계툴을 사용한 저전력 SoC 설계 동향

Low Power SoC Design Trends Using EDA Tools

- 저자

-

박남진SW-SoC개발환경연구실 njpark@etri.re.kr 주유상SW-SoC개발환경연구실 ysjoo@etri.re.kr 나중찬서울SW-SoC융합R&BD센터 njc@etri.re.kr

- 권호

- 35권 2호 (통권 182)

- 논문구분

- 일반논문

- 페이지

- 69-78

- 발행일자

- 2020.04.01

- DOI

- 10.22648/ETRI.2020.J.350206

- 초록

- Small portable devices such as mobile phones and laptops currently display a trend of high power consumption owing to their characteristics of high speed and multifunctionality. Low-power SoC design is one of the important factors that must be considered to increase portable time at limited battery capacities. Popular low power SoC design techniques include clock gating, multi-threshold voltage, power gating, and multi-voltage design. With a decreasing semiconductor process technology size, leakage power can surpass dynamic power in total power consumption; therefore, appropriate low-power SoC design techniques must be combined to reduce power consumption to meet the power specifications. This study examines several low-power SoC design trends that reduce semiconductor SoC dynamic and static power using EDA tools. Low-power SoC design technology can be a competitive advantage, especially in the IoT and AI edge environments, where power usage is typically limited.

Share

Ⅰ. 서론

핸드폰, 노트북 등 최근 소형 휴대용 기기들은 고속, 다기능화되어 가는 추세로 많은 전력을 소모한다. 한정된 배터리 용량에서 휴대시간을 늘리기 위해서는 저전력 SoC 설계는 고려해야 할 중요한 요소 중에 하나이다.

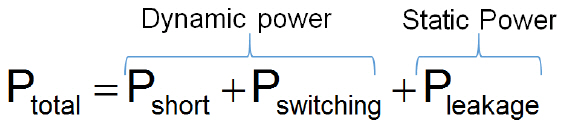

SoC 전력 소비는 동적전력(Dynamic Power)과 정적전력(Static Power)으로 구분된다. 동적전력은 신호가 값을 변경하는 경우 회로 작동 중에 흐르는 전류에 의해 소비되는 전력으로 출력 커패시턴스를 충전 및 방전하는 데 필요한 스위칭전류(Switching Current)와 셀의 스위칭 동안 NMOS 및 PMOS 트랜지스터가 동시에 모두 동작 상태일 때 단락전류(Short Current)에 의해 소비되는 전력이다. 정적전력은 전원을 켰지만 신호가 바뀌지 않을 때 누설전류(Leakage Current)에 의해 소비되는 전력이다[4].

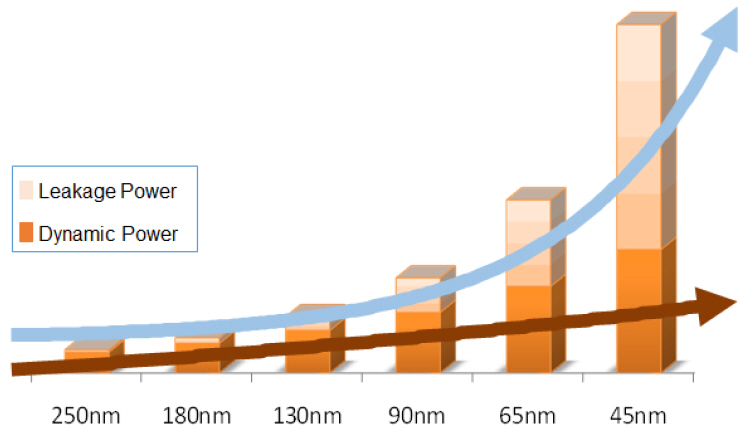

SoC 전력 소비의 절댓값 증가와 함께 반도체 공정기술에 따른 전력 소비의 질적 변화도 발생한다. 반도체 공정기술 크기가 감소함에 따라 총 전력 소비에서 동적전력보다 누설전력이 차지하는 부분이 커질 수 있다. 누설전력은 90nm 공정의 40~50%에서 65nm 공정의 50~60%로 증가한다(그림 1)[8]. 이는 장치가 실제 작동 중일 때보다 작동하지 않는 대기모드에서 더 많은 전력을 소비함을 의미한다.

그림 1

Ratio of Dynamic and Leakage Powers

출처 Synopsys, “Synopsys University Courseware Low Power Design with SAED 90nm EDK,” 2011.

많이 적용되는 저전력 SoC 설계 기술은 클록게이팅(Clock Gating), 다중임계전압(Multi-threshold Voltage), 파워게이팅(Power Gating), 다중전압설계(Multi-voltage Design)를 들 수 있다. 여기서는 EDA 툴을 사용하여 동적전력과 정적전력을 줄이는 저전력 SoC 설계 동향을 살펴본다.

Ⅱ. EDA 전력인식 설계

1. EDA 전력인식 설계흐름

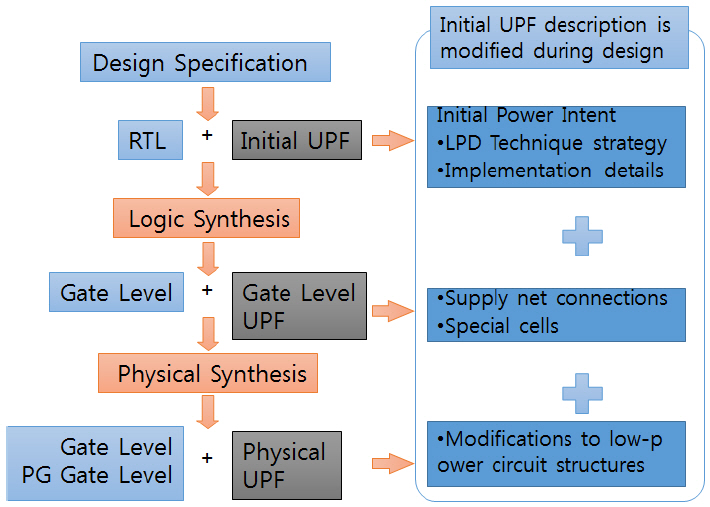

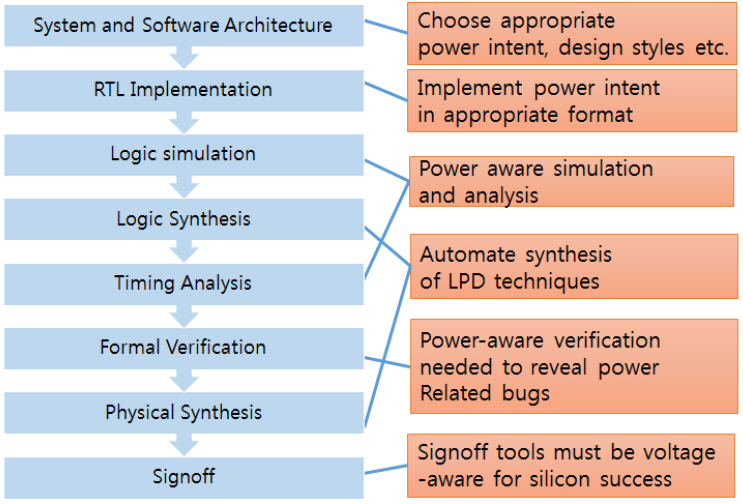

저전력 SoC 설계를 위해 그림 2와 같이 모든 EDA 설계 단계에서 전원관리를 고려해야 한다[8,14]. 시스템 수준에서 설계 특성에 따라 적절한 전력의도를 선택해야 한다. 예로, 설계 초기 단계에서 최대 성능으로 작동해야 하는 부품과 일정 기간 동안 종료될 수 있는 부품이 이미 알려져 있다. RTL 구현 단계에서 이러한 전력의도 또한 구현해야 하며, 이는 RTL에서 직접 수행할 수 있지만 잘 사용되지 않으며 대신 UPF를 사용하여 구현한다.

그림 2

EDA 전력인식 설계흐름

출처 Synopsys, “Synopsys University Courseware Low Power Design with SAED 90nm EDK,” 2011.

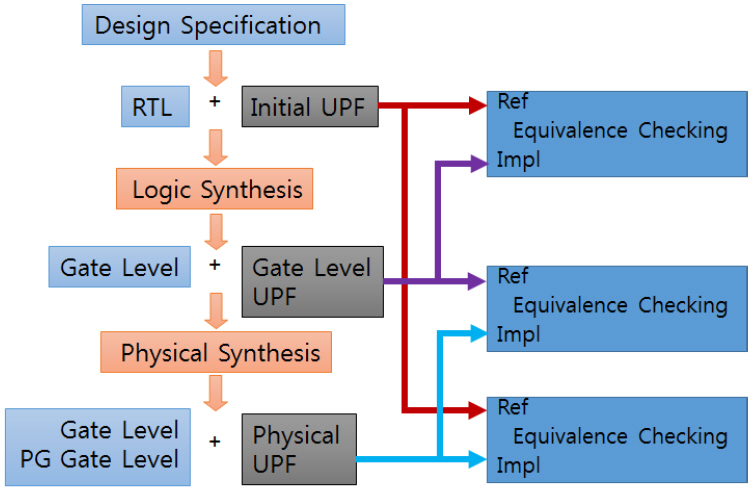

초기 설계 단계에서 전력의도를 시험할 수 있는 전력인식 로직 시뮬레이션과 타이밍 분석 도구가 있어야 한다. 설계 흐름의 또 다른 고려 사항은 저전력 설계(LPD: Low Power Design) 기술을 자동으로 구현할 수 있는 논리 및 물리적 합성 도구가 있어야 한다. 등가성 검증(Formal Verification) 툴은 초기 단계 RTL 및 전력의도와 합성 단계 후의 게이트레벨 설계 간의 등가성을 점검할 수 있어야 한다. 마지막 설계 단계 사인오프도 전압의도를 갖도록 고려해야 한다.

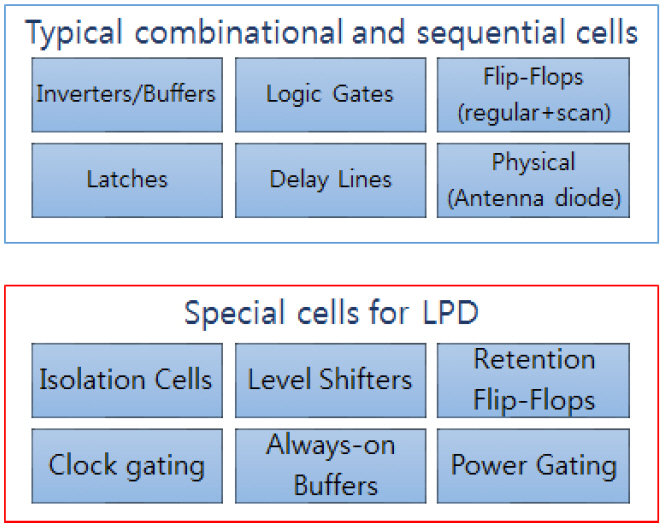

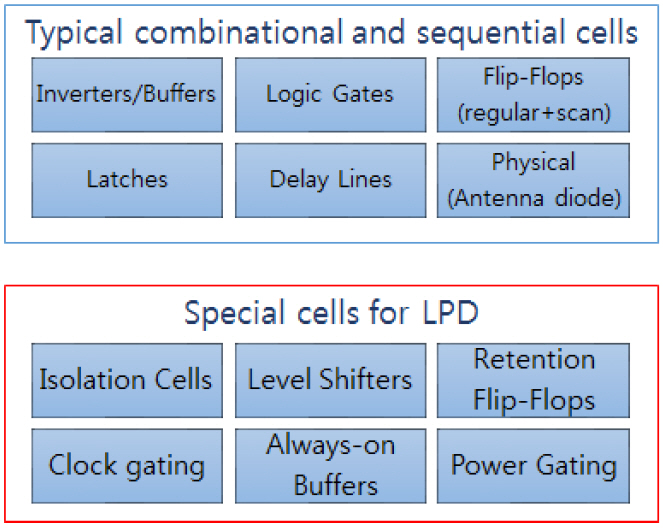

2. Cell Library

저전력 SoC 설계는 EDA 툴에 의해 자동으로 구현되는 추세이며, 저전력 SoC 설계 기술을 구현하기 위해 일반 셀 라이브러리 이외에 특수 셀 라이브러리가 필요하다. 일반 셀 라이브러리에는 다양한 구동 강도의 일반적인 조합 및 순차 논리 셀이 포함된다. 특수 셀 라이브러리에는 클록게이팅, 다중임계전압, 파워게이팅, 다중전압설계와 같은 저전력 전략에 필요한 셀(레벨시프터, 격리 셀, 유지 플립 플롭 등)이 포함된다(그림 3)[3,8]. 셀 라이브러리는 저전력 SoC 설계를 지원하여 동적전력 및 누설전력을 최소화하는 데 사용된다.

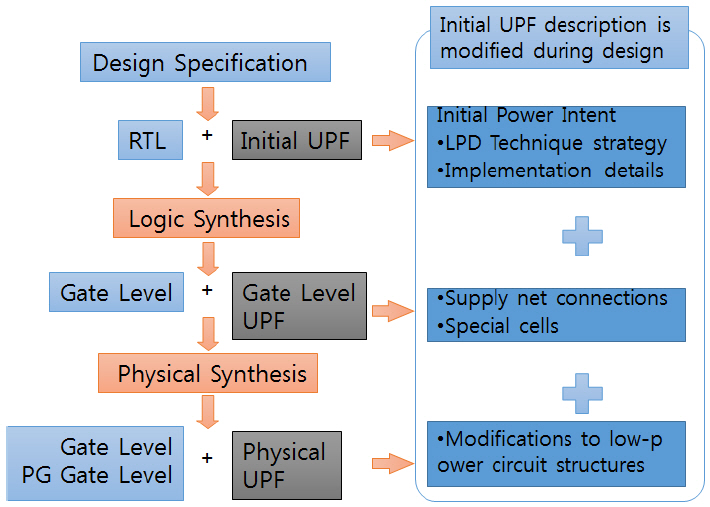

3. UPF 추가 설계흐름

전력의도 사양은 IEEE 1801 표준 또는 UPF (Unified Power Format)를 사용하여 정의할 수 있고, UPF를 사용하여 전원공급장치 네트워크, 전원 스위치, 절연, 유지 및 기타 전원 관리를 할 수 있다. UPF는 설계사양, 논리합성, 물리합성, 분석, 검증 등의 설계흐름 전반에 걸쳐 사용된다[2].

RTL 개발자는 RTL과 초기 UPF를 함께 개발할 수 있으며, RTL 및 UPF은 각각의 다른 파일에 포함되므로 별도로 유지보수 및 수정할 수 있다. 논리합성 단계는 게이트레벨 netlist 및 게이트레벨 UPF 파일을 생성한다. 이 게이트레벨 UPF 파일에는 초기 UPF 정보와 논리합성 중에 생성된 특수 셀에 대한 명시적 전원 공급망 연결을 포함하고 있다. 물리합성 단계는 게이트레벨 netlist 및 게이트레벨 UPF를 읽고 물리적 구현(배치 및 배선)을 수행하여 전원 접지(Power or Ground) 게이트레벨 netlist 및 물리적 UPF 파일을 생성한다. 물리적 UPF 파일에는 이전 UPF 정보와 더불어 전원 스위치와 같은 저전력 회로에 대한 수정 사항을 포함하고 있다(그림 4)[10].

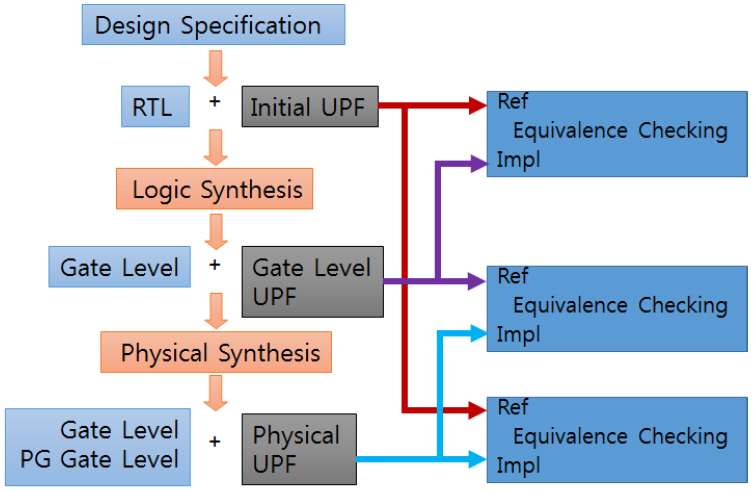

4. 등가성 검증 설계흐름

Ⅲ. 설계툴을 사용한 저전력 SoC 설계 동향

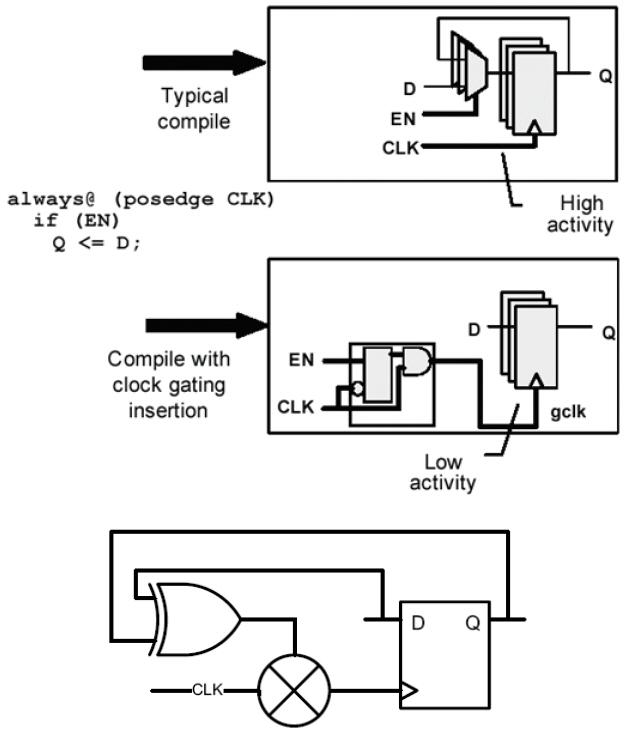

1. Clock Gating

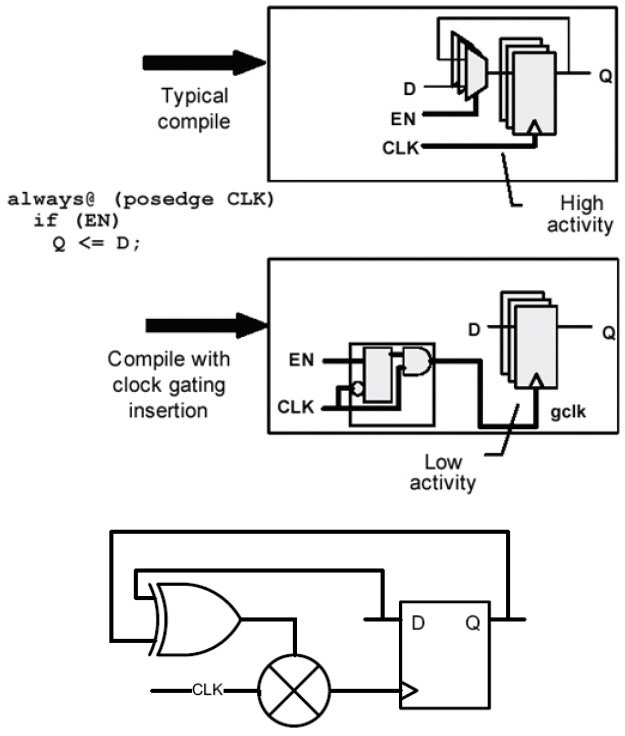

클록게이팅은 비활동 기간 동안 선택된 클록 신호를 정지시키는 동적전력 감소 방법이다. EDA 합성 툴은 클록이 적은 데이터 경로를 감지할 수 있고, 자동으로 클록게이팅 셀을 삽입할 수 있다. 초기에는 설계자가 RTL에서 클록게이팅 회로를 명시적으로 코딩했지만, 오늘날에는 클록게이팅을 구현하기 위해 RTL을 변경할 필요가 없다. 대부분의 라이브러리에는 EDA 합성 툴에 의해 인식되는 클록게이팅 셀이 포함되어 있고, 명시적 클록게이팅 셀과 자동 삽입 명령의 조합으로 클록게이팅을 구현할 수 있다[13].

XOR 자체게이팅 셀에서 XOR는 레지스터에 저장된 데이터와 데이터 핀에 도달하는 데이터를 비교하여, 데이터가 변경되지 않으면 불필요한 클록 사이클은 XOR의 출력에 의해 게이트된다. 자체게이팅은 활성화 조건을 기존 로직에서 유추할 수 없는 경우에 유용하다(그림 6)[11].

SoC에는 일반적으로 많은 클록 버퍼가 있고, 클록 버퍼는 지연을 최소화하기 위해 높은 구동 강도를 가지며, 시스템에서 가장 높은 토글 속도를 가지므로 클록 버퍼에서 최대 50% 이상의 동적전력을 소비할 수 있다. 클록게이팅은 클록 버퍼 전단에 위치하여 전력 절감을 크게 한다. 클록게이팅 적용 실례로 클록게이팅이 없는 180nm 칩과 클록게이팅 기술로 재 구현된 칩과 비교에서 작동모드에 따라 면적이 20%, 전력이 34~43% 감소했다[5].

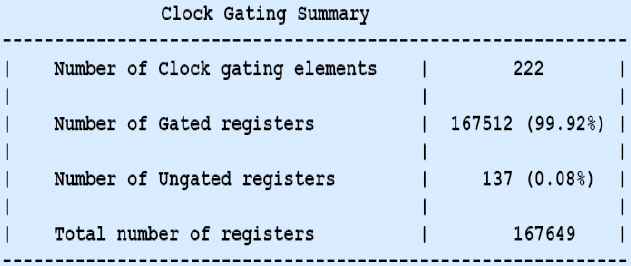

표 2는 EDA 툴에서 클록게이팅 설계 사례이다.

표 2

클록게이팅 설계 사례

표 3은 명령(report_clock_gating)을 실행한 클록게이팅 설계 보고이다.

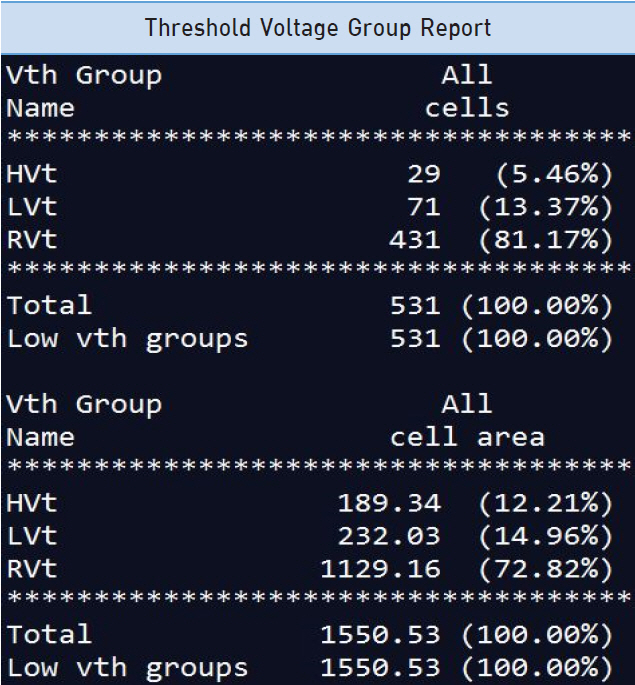

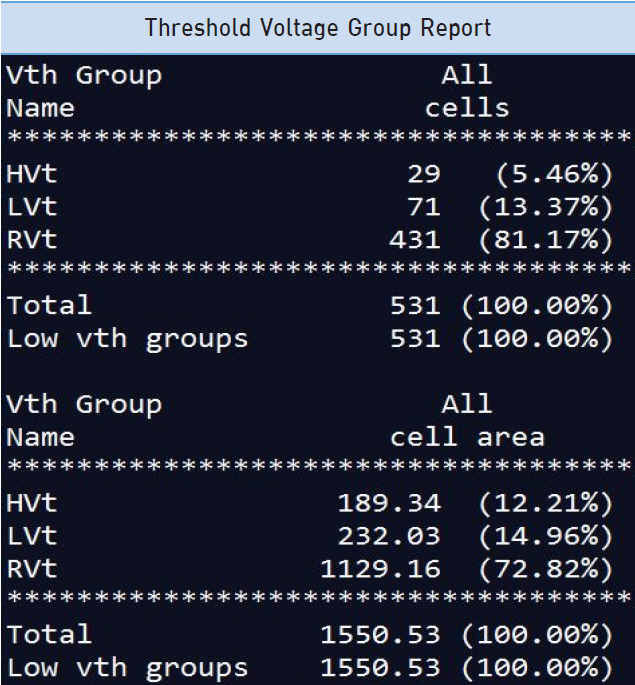

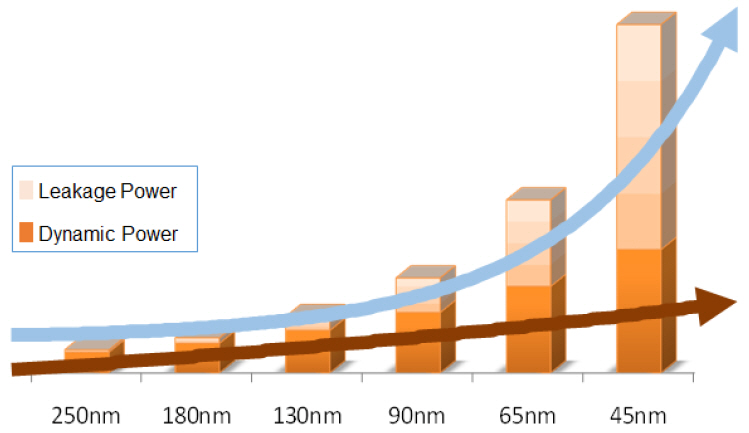

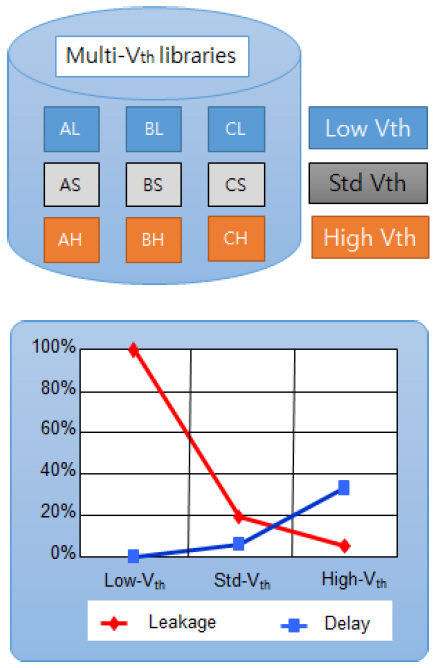

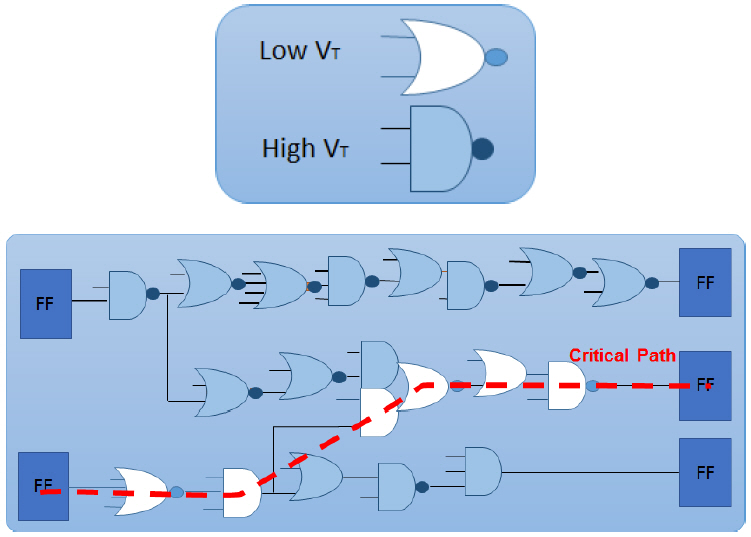

2. Multi-threshold Voltage

다중임계전압은 누설전력 감소 방법으로 다중임 계전압 라이브러리가 필요하다. 일반적으로 동일한 디지털 표준 셀에 대해 낮은 임계전압, 표준 임계전압 및 높은 임계전압의 세 가지 변형이 있다. 높은 임계전압 셀은 누설전력이 낮지만 느리며, 낮은 임계전압 셀은 누설전력이 높지만 빠르다(그림 7)[8].

그림 7

다중임계전압 설계 라이브러리

출처 Synopsys, “Synopsys University Courseware Low Power Design with SAED 90nm EDK,” 2011.

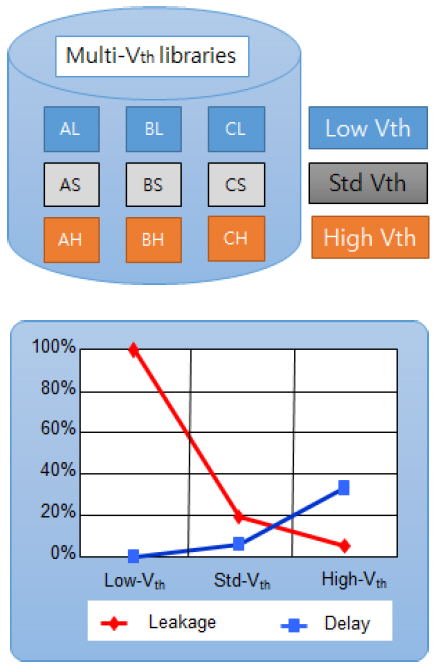

상이한 임계전압을 갖는 셀을 동일한 설계에서 사용 가능하면, 추가 타이밍 마진을 제거함으로써 낮은 누설전력 설계를 할 수 있다. 지연이 작아야 하는 경로(Critical Path)에는 낮은 임계전압 셀(흰색)을 사용하고, 회로의 다른 부분에서는 높은 임계전압 셀(파란색)을 사용하여 누설전력을 감소시킨다(그림 8)[8].

그림 8

다중임계전압 설계

출처 Synopsys, “Synopsys University Courseware Low Power Design with SAED 90nm EDK,” 2011.

EDA 툴은 다중임계전압 라이브러리를 활용하여 타이밍과 전력을 동시에 최적화할 수 있다. 타이밍을 충족시키기 위해 필요할 때만 낮은 임계전압 셀을 배치하여 낮은 임계전압 셀 총 수를 최소화하는 것을 목표로 한다.

표 4는 EDA 툴에서 다중임계전압 설계 사례이다. 표 5는 명령(report_threshold_voltage_group)을 실행한 다중임계전압 설계 보고이다.

표 4

다중임계전압 설계 사례

3. Power Gating

파워게이팅은 비활동 기간 장치의 일부를 종료하는 전력 절약 기술로, 예로 휴대폰 칩에서 음성 처리를 수행하는 블록은 전화가 대기 모드에 있으면 종료되고, 필요할 때 음성처리 블록은 깨워진다. 파워게이팅은 스위칭전력뿐만 아니라 누설전력을 낮추기 때문에 전체 전력 소비를 크게 줄일 수 있다[12]. 파워게이팅을 구현하기 위해서는 표 6의 사항을 고려해야 한다.

표 6

파워게이팅 고려 사항

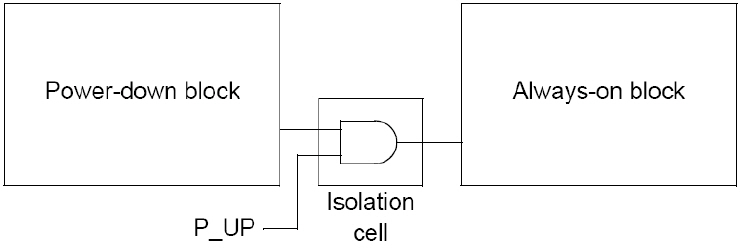

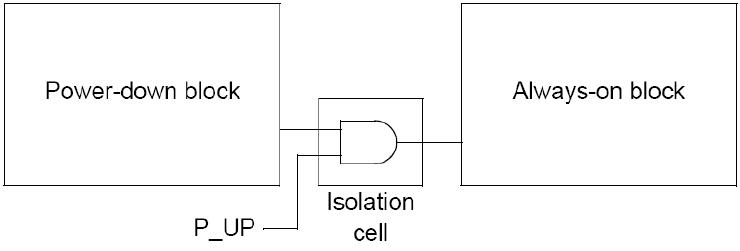

가. Isolation Cell

그림 9는 격리 셀의 간단한 구현을 나타낸다[11]. 왼쪽 블록 전원이 켜지면 신호 P_UP이 높으며 출력 신호가 격리 셀을 통과한다. 왼쪽 블록의 전원이 꺼지면 P_UP이 낮아 로직 0의 신호 상수가 항상 켜져 있는 블록으로 들어간다.

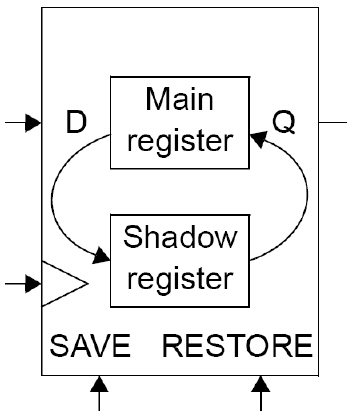

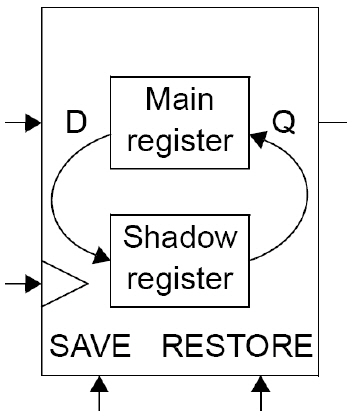

나. Retention Cell

블록의 전원을 껐다가 다시 켤 때 전원 끄기 이전의 상태로 복원되는 것이 요구된다. 이는 블록 레지스터 내용을 전원을 차단하기 전에 블록 외부의 RAM에 복사하고, 전원을 켠 후 다시 복원함으로써 이루어진다. 다른 방법은 그림 10과 같이 전원 차단 블록에서 유지 레지스터를 사용하는 것이다[11]. SAVE 신호는 전원이 꺼지기 전에 메인 레지스터 정보를 shadow 레지스터에 저장하고, RE STORE 신호는 전원을 켠 후 데이터를 복구한다.

표 7은 EDA 툴에서 파워게이팅 설계 사례이다.

표 7

파워게이팅 설계 사례

표 8은 파워게이팅 UPF 사례이다.

표 8

파워게이팅 UPF 사례

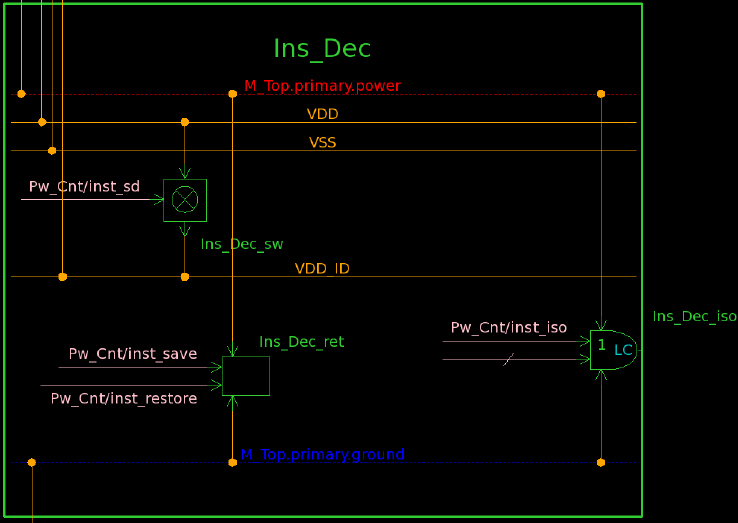

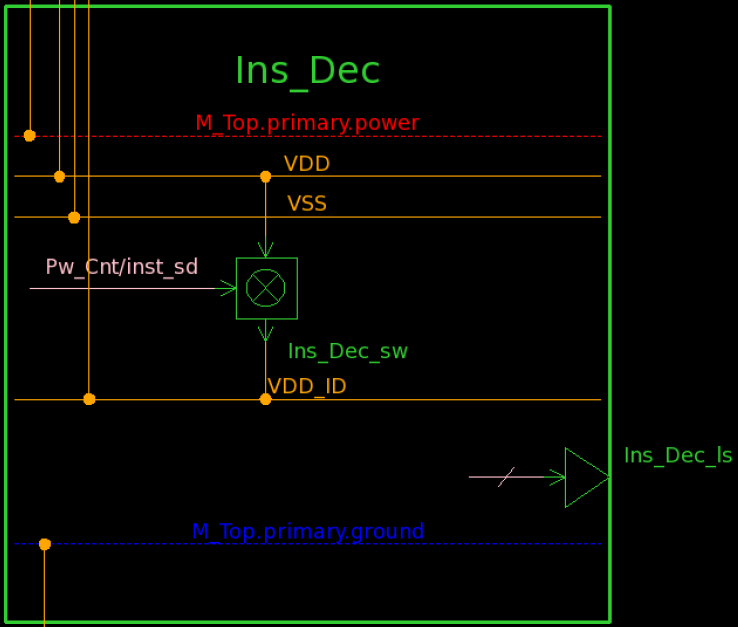

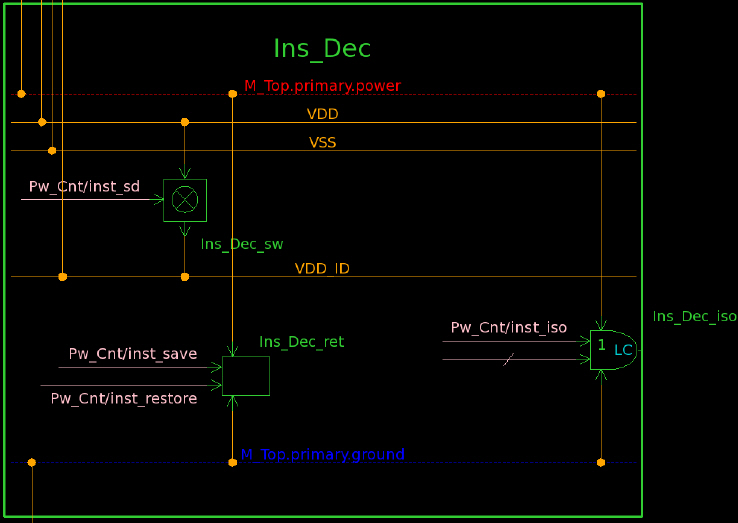

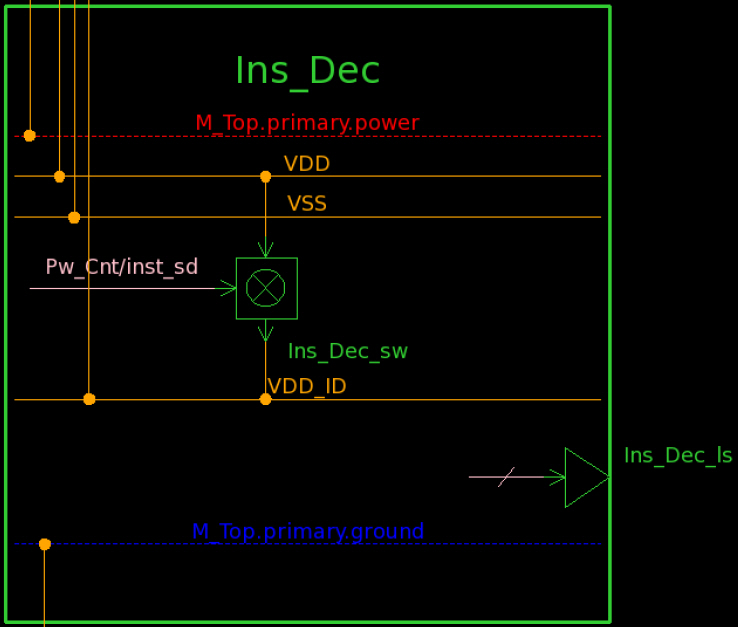

그림 11은 표 8의 UPF Diagram을 나타낸다. 파워게이팅 적용 실례에서 파워게이팅을 통한 에너지 절감은 20~38%로 보고되고 있다[6].

4. Multi-voltage Design

동적전력은 공급전압 제곱에 비례하므로 선택한 블록에서 공급전압을 낮추면 전력을 줄일 수 있다. 그러나 공급전압을 낮추면 설계에서 게이트 지연이 증가한다.

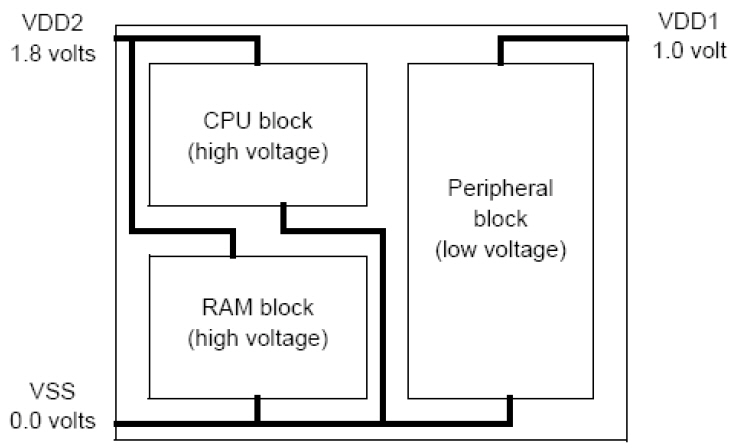

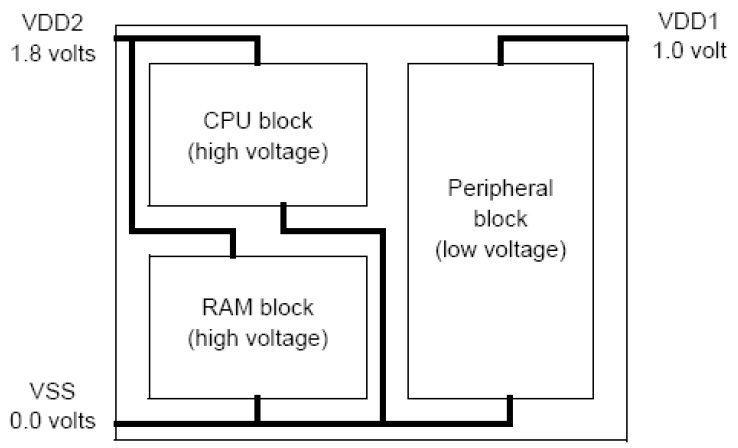

칩의 부품마다 속도 요구 사항이 다를 수 있다. 예를 들어, CPU와 RAM 블록은 주변장치 블록보다 빠를 수 있다. 최대 속도를 얻으려면 CPU와 RAM은 더 높은 전원으로 작동할 수 있고, 주변장치 블록은 그림 12와 같이 더 낮은 전압으로 작동할 수 있다[11]. 다중전압설계에서 칩의 내부 로직은 각각 고유한 공급 장치가 있는 여러 전압 영역 또는 전력 도메인으로 분할된다. RAM 블록에서는 메모리에 액세스하지 않을 때 메모리 내용을 유지하기 위해 낮은 전압을 공급하는 구상과 읽기 및 쓰기를 할 때 더 높은 전압을 공급하는 구상을 할 수 있다.

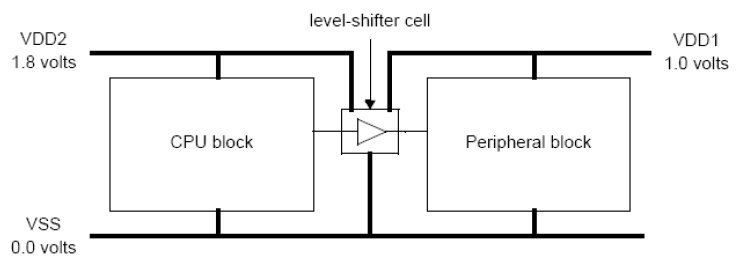

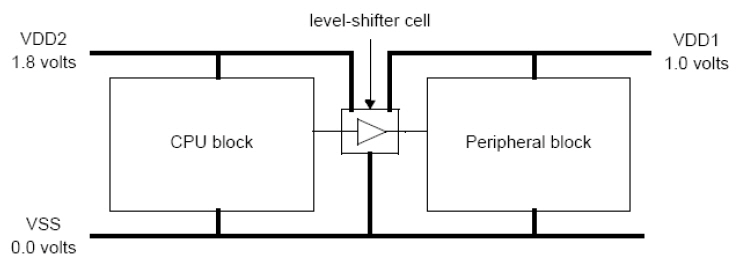

논리 신호가 한 전원 도메인에서 다른 전원 도메인으로 들어가는 경우, 다른 전압 신호를 생성하기 위해서는 레벨시프터 셀이 필요하다.

가. Level Shifter

그림 13에서 레벨시프터는 1.8V 스윙 신호를 1.0V 스윙 신호로 변환하며, 입력 및 출력 공급 전압의 두 가지 전원 장치를 필요로 한다[11].

표 9는 여러 다중전압설계 방법을 나타낸다.

표 9

다중전압설계 방법

표 10은 EDA 툴에서 다중전압설계 사례이다.

표 10

다중전압설계 사례

표 11

다중전압설계 UPF 사례

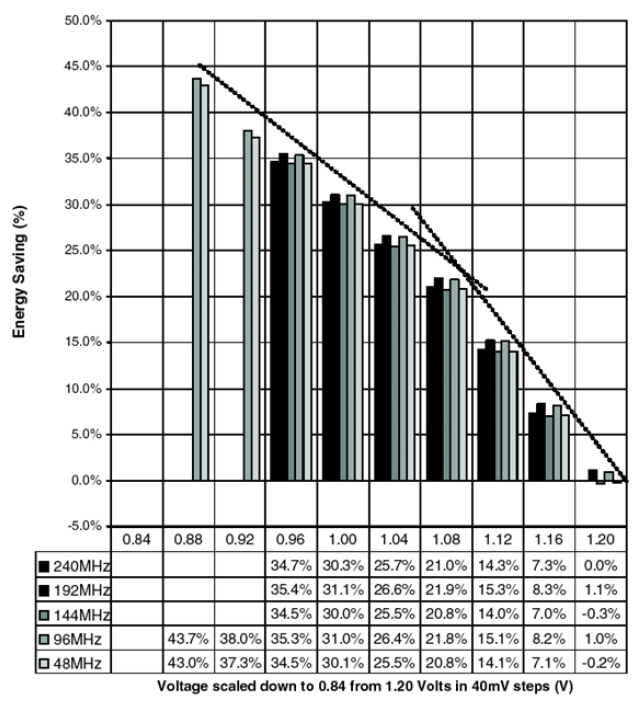

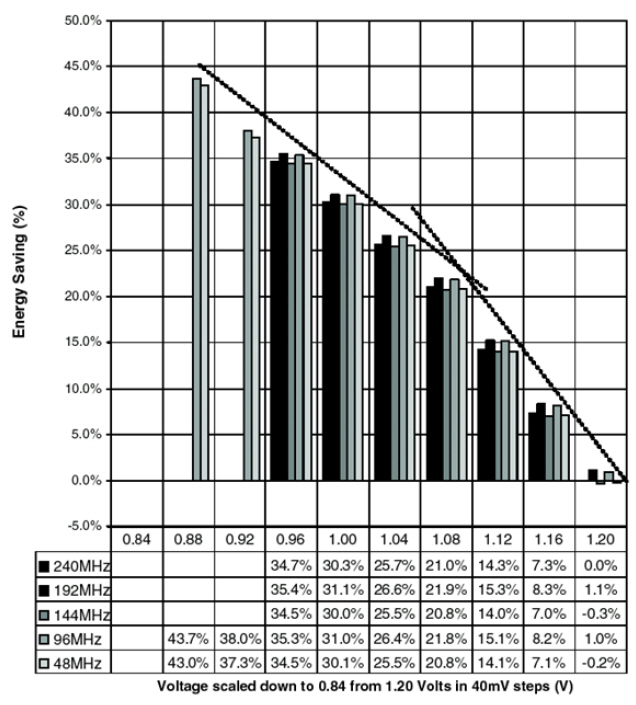

그림 14는 DVFS 다중전압설계 사례(TSMC 65nm, ATLAS926 Case Study)에서 측정된 에너지 절약 (1.20V, 240MHz 기준)을 나타낸다[7]. 그림 15는 표 11의 UPF Diagram을 나타낸다.

Ⅳ. 결론

EDA 툴을 사용하여 다양한 설계 단계에서 클록게이팅, 다중임계전압, 파워게이팅, 다중전압설계 등의 저전력 SoC 설계 동향을 살펴보았다. 최근 소형 휴대용 기기들은 고속, 다기능화 되어가는 추세로 전력 소비의 절댓값 증가와 함께 반도체 공정기술에 따른 전력 소비의 질적 변화도 발생한다. 반도체 공정기술 크기가 감소함에 따라 총 전력 소비에서 동적전력보다 누설전력이 차지하는 부분이 커질 수 있으므로, 적절한 저전력 SoC 설계 방법을 조합하여 전력 사양을 만족하도록 전력 소비를 감소시켜야 한다.

저전력 SoC 설계 기술은 설계 구현 도구에 따라 다르게 처리되며 복잡도에 따라 다른 노력 수준이 필요하다. 클록게이팅 및 다중임계전압 기술은 도구가 자동으로 최적화를 수행할 수 있으므로 일반적으로 적은 노력이 필요하다. 다중전압설계 및 파워게이팅 기술은 도구에 대한 입력으로 아키텍처 수준의 전력관리 전략을 제공해야 하며, UPF의 추가 데이터와 관련하여 설계흐름 수정이 필요하다. 저전력 SoC 설계 기술은 특히 전력 사용에 제한적인 사물인터넷, 인공지능 에지 환경 등에서 경쟁력으로 작용할 수 있다.

약어 정리

AI

Artificial Intelligence

DVFS

Dynamic Voltage Frequency Scaling

EDA

Electronic Design Automation

IoT

Internet of Things

LPD

Low Power Design

NMOS

N-type Metal Oxide Semiconductor

PG

Power or Ground

PMOS

P-type Metal Oxide Semiconductor

RTL

Register Transfer Level

SoC

System on Chip

UPF

Unified Power Format

XOR

Exclusive OR

Ashok B. Mehta, "ASIC/SoC Functional Design Verification: A Comprehensive Guide to Technologies and Methodologies," Springer, 2018.

D. Flynn, R. Aitken, A. Gibbons, K. Shi., "Low Power Methodology Manual: For System-on-Chip Design," Springer. 2010.

Pokhrel, K, "Physical and Silicon Measures of Low Power Clock Gating Success: An Apple to Apple Case Study," SNUG, 2007.

Kwangok Jeong, Andrew B Kahng, Seokhyeong Kang, Tajana S Rosing, and Richard Strong, "MAPG: Memory Access Power Gating," Proc. of the Conference on DATE, 2012, pp. 1054–1059.

Synopsys, "Synopsys University Courseware Low Power Methodology Manual Based on 32/28nm EDK," 2012.

Synopsys, "Implementing Power Gating Using Synopsys Implementation Tools Application Note," Version A-2007.12, January 2008.

그림 1

Ratio of Dynamic and Leakage Powers

출처 Synopsys, “Synopsys University Courseware Low Power Design with SAED 90nm EDK,” 2011.

그림 2

EDA 전력인식 설계흐름

출처 Synopsys, “Synopsys University Courseware Low Power Design with SAED 90nm EDK,” 2011.

그림 3

Cell Library

출처 Synopsys, “Synopsys University Courseware Low Power Design with SAED 90nm EDK,” 2011.

그림 7

다중임계전압 설계 라이브러리

출처 Synopsys, “Synopsys University Courseware Low Power Design with SAED 90nm EDK,” 2011.

그림 8

다중임계전압 설계

출처 Synopsys, “Synopsys University Courseware Low Power Design with SAED 90nm EDK,” 2011.

표 1

등가성 검증 데이터

| • | RTL과 초기 UPF |

| • | 게이트레벨 netlist과 게이트레벨 UPF |

| • | 게이트레벨 netlist과 게이트레벨 UPF |

| • | 전원 접지 게이트레벨 netlist과 물리적 UPF |

| • | RTL과 초기 UPF |

| • | 전원 접지 게이트레벨 netlist과 물리적 UPF |

표 2

클록게이팅 설계 사례

표 4

다중임계전압 설계 사례

표 6

파워게이팅 고려 사항

표 7

파워게이팅 설계 사례

표 8

파워게이팅 UPF 사례

표 9

다중전압설계 방법

표 10

다중전압설계 사례

표 11

다중전압설계 UPF 사례

- Sign Up

- 전자통신동향분석 이메일 전자저널 구독을 원하시는 경우 정확한 이메일 주소를 입력하시기 바랍니다.