양자점 큐비트 기반 양자컴퓨팅의 국외 연구 동향 분석

Research Trend for Quantum Dot Quantum Computing

- 저자

-

백충헌양자컴퓨팅연구실 CHBaek@etri.re.kr 최병수양자컴퓨팅연구실 bschoi3@etri.re.kr

- 권호

- 35권 2호 (통권 182)

- 논문구분

- 일반논문

- 페이지

- 79-88

- 발행일자

- 2020.04.01

- DOI

- 10.22648/ETRI.2020.J.350207

본 저작물은 공공누리 제4유형: 출처표시 + 상업적이용금지 + 변경금지 조건에 따라 이용할 수 있습니다.

본 저작물은 공공누리 제4유형: 출처표시 + 상업적이용금지 + 변경금지 조건에 따라 이용할 수 있습니다.- 초록

- Quantum computing is regarded as one of the revolutionary computing technologies, and has attracted considerable attention in various fields, such as finance, chemistry, and medicine. One of the promising candidates to realize fault tolerant quantum computing is quantum dot qubits, due to their expectation of high scalability. In this study, we briefly introduce the international tendencies for quantum dot quantum computing. First, the current status of quantum dot gate operations is summarized. In most systems, over 99% of single qubit gate operation is realized, and controlled-not and controlled-phase gates as 2-qubit entangling gates are demonstrated in quantum dots. Second, several approaches to expand the number of qubits are introduced, such as 1D and 2D arrays and long-range interaction. Finally, the current quantum dot systems are evaluated for conducting quantum computing in terms of their number of qubits and gate accuracies. Quantum dot quantum computing is expected to implement scalable quantum computing. In the noisy intermediate-scale quantum era, quantum computing will expand its applications, enabling upcoming questions such as a fault-tolerant quantum computing architecture and error correction scheme to be addressed.

Share

Ⅰ. 서론

양자컴퓨팅은 양자 현상에 기반한 변혁적 컴퓨팅으로, 기존에 해결 불가능하였던 문제들을 풀 수 있을 것으로 기대된다. 특히 금융, 화학, 의료, IT 등 다방면에서 양자컴퓨팅의 혁신적 계산능력이 활용되기를 기다리고 있다[1].

양자컴퓨팅의 영향력이 높아질 것이라는 기대가 늘어남에 따라 주요 국가에서의 연구도 늘어나고 있다. 미국은 양자컴퓨팅 분야의 연구개발 법안을 수립하였고[2,3], 유럽과 영국 또한 양자기술에 대규모 투자가 시작되었다[4,5]. 아시아권에서는 일본에서 양자정보처리 프로젝트를 진행 중이며[6], 중국에서는 양자컴퓨팅 산업육성 로드맵을 발표하는 등 관심이 높아지고 있다[7].

양자컴퓨팅 기술이 발전함에 따라 기업에서도 양자컴퓨팅을 활용한 기술개발을 진행하고 있다. 최근 IBM에서는 초전도 기반의 상용 양자컴퓨터를 출시하였고, 작은 규모의 사이즈는 클라우드 형태로 오픈되었다. 특히 구글은 72큐비트의 양자컴퓨터를 발표하였으며, 최근 양자컴퓨팅이 비트기반 컴퓨팅보다 빠르다는 것을 보여주었다[8].

Ⅱ. 큐비트의 정의 및 평가

큐비트는 양자역학적 상태 2개를 이용하는 시스템이다. 이를 컴퓨팅에 사용하기 위하여 시스템의 초기화, 연산, 측정을 수행한다. 큐비트를 만들 수 있는 물리계에는 제한이 없다. 예컨대 초전도 현상이나 이온, 중성원자의 불연속적인 에너지 상태 중에서 특정 2개 상태를 골라서 초기화, 연산, 측정을 할 수 있다면 큐비트가 될 수 있다.

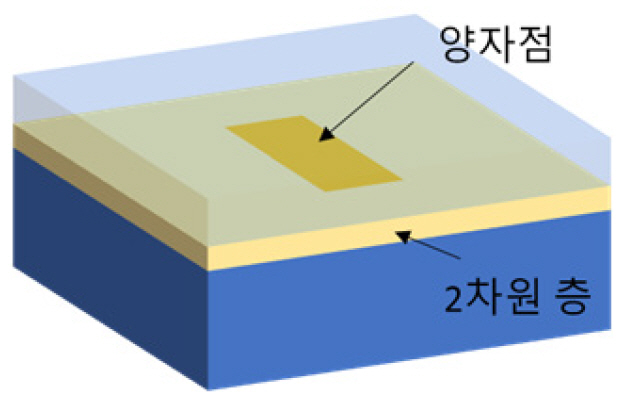

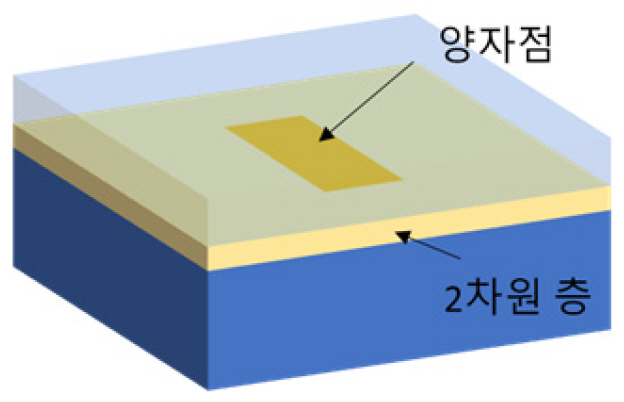

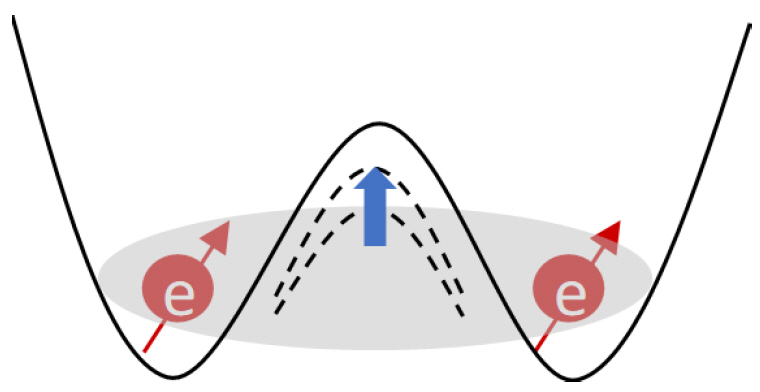

양자점(QD: Quantum Dot)은 3차원 고립 구조체로 불연속적 에너지 준위를 형성하기 때문에 인공 원자라고도 불린다. 양자점 큐비트는 이러한 불연속적 에너지 준위의 가장 기저에 있는 2개의 상태를 이용하여 만든 시스템이다. 3차원 고립 상태를 만들기 위한 방법 중 하나는 단일 층을 형성하는 것이다[9-11]. 반도체의 표면 방향으로 이종의 물질을 쌓음으로써 고립시킨다. 그 결과 그림 1의 노란색 층과 같이 전자가 단일 층 내에서만 움직일 수 있다. 곧이어, 전기적 반발력을 이용하여 전자를 3차원으로 고정시키는 것이다. 이는 제한된 공간에서만 움직일 수 있도록 벽을 만들어 고정시키는 것과 비슷하다. 그림 1의 진한 노란색 칸처럼, 전자는 이 안에 고정되어 움직이기 어려워진다.

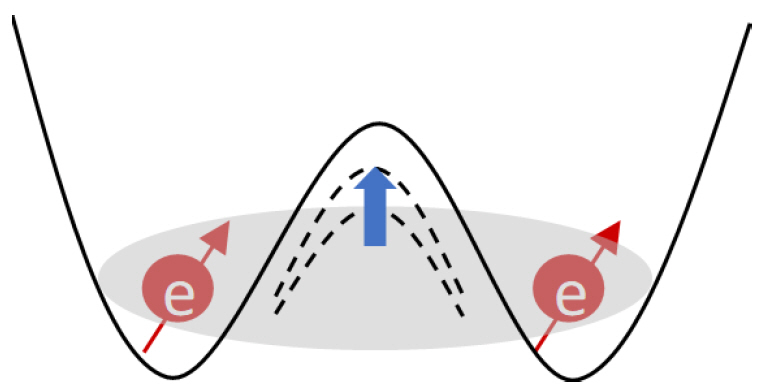

양자점 큐비트는 양자점이 형성하는 불연속 양자 상태들 가운데 두 개의 양자 상태를 선택한다. 이를 위해 양자점 내부의 전자 개수를 조절하기도 한다. 대표적으로 활용하는 큐비트는 전자 1개의 스핀 상태를 이용하여 스핀 위 상태와 스핀 아래 상태를 사용한다. 본고에서는 이를 단일전자 양자점 큐비트라고 하겠다. 다음으로는 전자 2개를 이용할 수 있는데, 전자 2개가 쌍으로 만드는 4가지 상태 중에 2가지를 선택하여 큐비트를 형성하므로, 전자쌍 양자점 큐비트라 명명하도록 하겠다.

양자점 큐비트를 만들면, 이를 연산에 활용하기 위한 신뢰도를 평가한다. 양자 상태는 비트와 위상 두 가지 축에 대한 정보가 있기 때문에 단순히 측정 결과로 나오는 0과 1의 개수만으로 양자 연산에 대한 신뢰도를 판단하기는 어렵다. 이를 해결하기 위하여 비트축, 위상축 등 여러 정보 방향에서 양자 상태의 입출력을 평가하여 양자 연산의 신뢰도를 정의한다.

Ⅲ. 연구개발 동향

본고에서 양자점 기반의 큐비트 연구개발 동향은 양자 게이트 구현, 큐비트 수 확장 방법, 종합적 분석으로 나누어서 조사하였다. 양자 게이트 구현 측면에서는 단일 큐비트 게이트 및 얽힘 큐비트 게이트 개발동향에 대하여 정리하였다. 큐비트 수를 확장하기 위한 방법 측면에서는 작은 영역에서 확장하는 1D, 2D 배열방법과 큰 영역에서 장거리 정보 전달로 확장하는 방법을 고려하였다. 마지막으로 큐비트 수와 양자게이트 정확도를 종합적으로 분석하여 정리하였다.

1. 게이트 구현 측면

가. 단일 큐비트 양자게이트

큐비트를 이용한 양자게이트는 크게 1개의 큐비트를 대상으로 하는 단일 게이트와 2개 이상의 큐비트를 대상으로 하는 얽힘 게이트로 나눌 수 있다. 단일 게이트는 대표적으로 X, Y, Z, H, T 게이트 등이 있다. 직관적인 양자 게이트의 특성을 보이는 것은 X, Z 게이트이다. X 게이트는 비트 정보를 대상으로 NOT 연산을 하는 게이트이며, Z 게이트는 위상 정보를 대상으로 NOT 연산을 하는 게이트이다. 한편, 임의의 연산을 구현하기 위하여 표준적으로 쓰이는 게이트는 H, T 게이트이다. H 게이트는 위상과 비트의 축을 전환시키는 게이트이며, T 게이트는 위상을 변화하는 게이트이다. 이를 조합하여 위상과 비트를 모두 바꿀 수 있다.

양자점 큐비트는 임의의 연산에서 요구하는 H, T 게이트를 구현하기 위하여 X, Y 게이트를 사용한다. 이는 동일한 목적지를 가기 위하여 다른 경로를 사용하는 것과 같다. 완만한 등산로를 이용하여 정상을 올라갈지, 가파른 등산로를 이용할지와 비슷한 셈이다. 양자점 큐비트는 곧바로 H 게이트나 T 게이트를 구현하기 어렵기 때문에 이를 동일한 효과를 나타내는 게이트를 만드는 것이다.

양자점을 이용한 게이트 구동 시간, 정확도는 표 1과 같다. 최근 대부분의 보고에서 단일 게이트는 99% 이상의 정확도를 보이고 있다.

표 1 단일 게이트 성능 지표

| 구분 | 구동시간 (나노초) | 연산수(1초) | 정확도 | 출처 |

|---|---|---|---|---|

| 1 | 1,400 | 715,000 | 99.9% | [12] |

| 2 | 70 | 1,400,000 | 98.6% | [13] |

| 3 | 500 | 2,000,000 | 98.8% | [14] |

| 4 | 65 | 16,600,000 | 99.9% | [15] |

| 5 | 210 | 4,800,000 | 99.7% | [16] |

나. 단일 전자 큐비트를 이용한 CNOT 게이트 구현

CNOT 게이트는 대표적인 얽힘 게이트로서 첫 번째 큐비트가 1일 때 두 번째 큐비트에 NOT 연산을 수행하는 게이트이다. 즉, 첫 번째 큐비트의 상태에 근거하여 첫 번째 큐비트의 상태를 바꾸지 않고 두 번째 큐비트의 비트상태를 반전시키는 연산이다. 이는 양자컴퓨팅의 범용적인 연산을 구성하기 위하여 사용되는 대표적인 2큐비트 논리 게이트이다. CNOT 게이트는 큐비트 간 연산에 방 향성이 있다. 큐비트 1, 2번을 대상으로 CNOT 게이트의 수행 결과와 큐비트 2, 1번을 대상으로 CNOT 게이트의 수행 결과가 차이가 난다. 표 2는 CNOT 게이트의 진리표로 게이트 수행 전후의 입출력 양자 상태를 나타낸 값이다.

표 2 NOT 게이트의 진리표

|

연산 전 상태 |

연산 후 상태 |

||

|---|---|---|---|

| 첫 번째 큐비트 | 두 번째 큐비트 | 첫 번째 큐비트 | 두 번째 큐비트 |

| 0 | 0 | 0 | 0 |

| 0 | 1 | 0 | 1 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 1 | 0 |

단일 전자 큐비트를 이용한 CNOT 게이트의 구현 방법 중 하나는 단일 전자 사이의 교환에 일어나는 에너지 크기를 조절하여 둘 사이에 상호작용이 일어나게 만드는 것이다. 1큐비트 게이트를 구현할 때에는 큐비트 간 상호 영향을 받지 않도록 조절하고, 2큐비트 게이트를 구현할 때에는, 상호작용을 통해 얽힘이 일어나게 만든다. 양자점 큐비트를 2차원 전자층을 이용하여 만들 경우 교환 에너지를 조절하는 것이 매우 용이하다. 양자점 큐비트를 형성하기 위해서는 표면 전극을 통해 전자가 있는 곳과의 전위차를 형성한다. 같은 구조를 연이어 붙여 2개의 양자점에 각각 하나씩 큐비트를 만들었으므로, 두 큐비트가 연접해 있는 전극의 전압을 조절하게 되면 큐비트 간 상호작용을 통한 얽힘 연산을 수행하게 된다.

최근에는 위와 같은 방식으로 미국 프린스턴 대학의 제이슨 페타(J. Petta) 교수가 CNOT 게이트를 구현했다[16]. CNOT 게이트의 구동 시간은 약 200나노초(십억분의 1초)로 1초에 최대 5백만 번의 연산을 수행할 수 있다. 게이트의 수행 정확도는 초기화 및 측정에 포함되는 오류를 배제하면 78%이다.

다. 단일 전자 큐비트를 이용한 C-Phase 게이트 구현

C-Phase 게이트는 첫 번째 큐비트가 1일 때 양자 상태의 위상을 바꾸는 연산을 수행하는 게이트이다. CNOT 게이트와 유사한 점은 첫 번째 큐비트의 상태에 근거하여 연산을 수행한다는 점이다. 다만, 두 번째 큐비트의 비트 상태를 바꾸는 것이 아니며, 해당하는 양자 상태의 위상을 변경하는 연산이다. 이 게이트의 진리표는 표 3과 같다. C-Phase 게이트는 큐비트 간 연산에 방향성이 없다. 연산정확도가 높지 않고 연산량이 한정된 경우, 상대적으로 적은 연산수를 이용하여 양자컴퓨팅의 범용 연산 게이트를 만들 수 있다.

표 3 C-Phase게이트의 진리표

|

연산 전 상태 |

연산 후 상태 |

||||

|---|---|---|---|---|---|

| 위상 | 첫 번째 큐비트 | 두 번째 큐비트 | 위상 | 첫 번째 큐비트 | 두 번째 큐비트 |

| 0 | 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 | 0 | 1 |

| 0 | 1 | 0 | 0 | 1 | 0 |

| 0 | 1 | 1 | i | 1 | 1 |

C-Phase 게이트의 구현 방법 중 한 가지는 각각의 양자점에 있는 단일 전자를 한데 모아서 상호작용이 일어나게 만드는 것이다. 얽힘 게이트를 구현하기 위해서는 큐비트 간 상호작용을 만들어야 한다. CNOT 게이트는 이를 위하여 양자점 큐비트의 위치 간 상호작용을 조절하여 얽힘 연산을 구현했다면, C-Phase 게이트는 하나의 큐비트를 구성하는 전자를 잠시 다른 하나의 큐비트가 있는 곳으로 옮기어 상호작용을 만드는 방식이다.

이러한 구현 방식은 미국 위스콘신 대학의 마크 에릭슨(M. Eriksson) 교수가 구현했다[14]. C-phase 게이트의 구동시간은 160나노초로 1초에 6백만 번의 연산을 수행할 수 있다. C-Phase를 이용하여 Bell state[14]를 형성할 경우, 형성된 양자 상태의 정확도는 89%로 평가되었다.

라. 단일 전자 및 전자쌍 큐비트를 이용한 C-Phase 게이트 구현

단일 전자 큐비트와 전자쌍 큐비트를 같이 이용하는 방식은 양자컴퓨팅에 요구되는 큐비트의 초기화, 게이트 연산, 상태 측정 과정을 매우 빠르게 단축할 수 있다. 단일 전자 큐비트는 얽힘 게이트를 매우 빠르게 수행할 수 있지만, 초기화와 측정에 오랜 시간이 소요된다. 반면, 전자쌍 큐비트는 초기화와 측정이 상대적으로 빨리 완료되고, 얽힘 게이트에 긴 시간이 소요된다. 이러한 장점만을 이용하기 위하여 단일 전자와 전자쌍 큐비트를 동시에 사용하는 이용한 하이브리드형 방법을 이용할 수 있다.

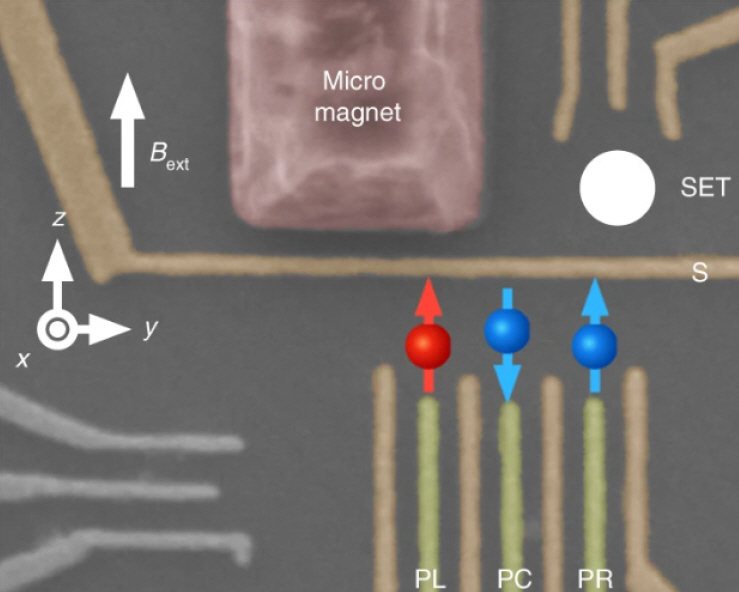

이러한 구현 방식은 일본 이화학 연구소의 세이고 타루차(S. Tarucha) 교수가 구현하였다[17]. 위 보고에서 C-Phase 게이트는 단일 전자 스핀 큐비트의 상태에 근거하여 양자 상태의 위상 값을 변경하도록 구현되었다. 하이브리드형 큐비트의 C-Phase 게이트의 구현 방법은 본질적으로 단일 전자 큐비트의 CNOT 게이트의 구현 방법이나 C-Phase 게이트의 구현방법과 다르지 않아 생략하도록 하겠다. 다만, 주요 특징으로 하이브리드형 큐비트 간 상호작용은 구동 방식상의 차이로 인하여 게이트 구동시간을 비약적으로 단축할 수 있다. C-phase 게이트의 구동시간은 5.5나노초로 1초에 1억 8천만 번의 연산을 수행할 수 있다.

2. 큐비트 수 확장 측면

본고에서는 큐비트 수를 확장하기 위한 방법을 크게 두 가지로 분류하였다. 첫째로 매우 제한된 영역 내에서 확장하는 방법이다. 양자점의 경우 매우 짧은 거리의 정보 전달만이 높은 정확도로 전달되어, 직접 큐비트 간 정보전달을 하는 경우이다. 둘째는 장거리 통신을 통하여 큐비트 수를 늘리는 방법이다. 이는 양자점 내의 단일 전자의 물리 상태로 정보를 전달하지 않고 다른 매개체를 통해 정보를 전달하는 방법이다.

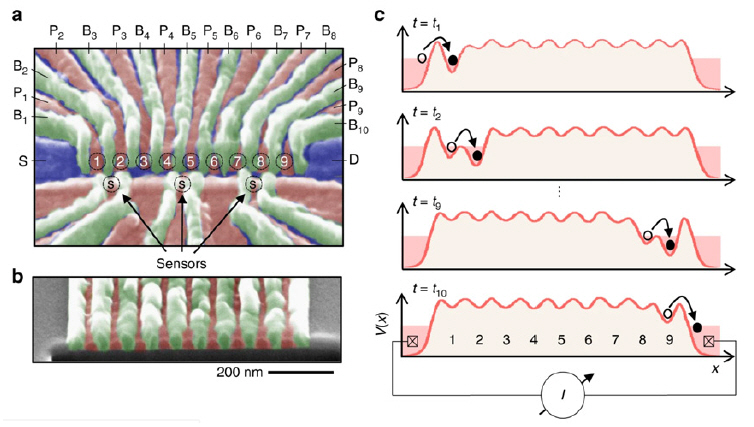

가. 선형 큐비트 배열을 통한 확장

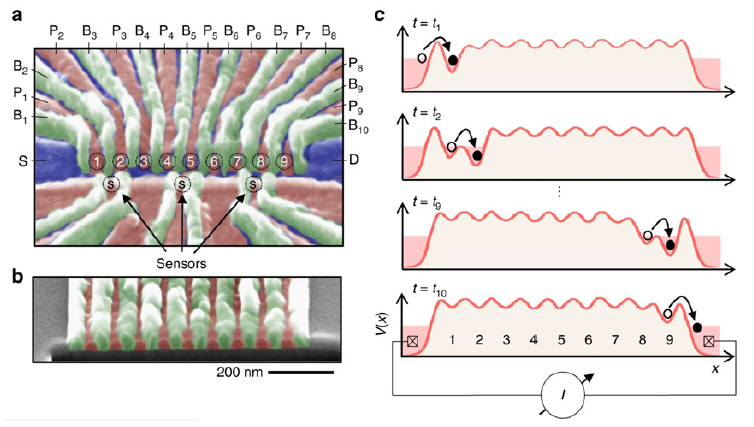

양자점 큐비트의 수를 늘리기 위한 방법 중 하나는 1차원 배열로 양자점을 이어붙이는 방법이다. 그림 3에서 2큐비트를 제작하기 위하여 3개의 양자점을 이어 붙인 것처럼, 그림 4[18]에서는 9개의 양자점을 이어붙였다. 하나의 양자점을 이용하여 최대 1개의 큐비트를 만들 수 있기 때문에 위의 9개 양자점을 이용하면 최대 9개의 큐비트를 만들 수 있다. 다만, 아직까지 9개의 양자점 기반의 9개 큐비트는 아직 구현되지 않았다. 최근 연구 결과[18]에 따르면, 가장 왼쪽에 있는 양자점에 큐비트로 활용 가능한 단일전자를 위치시킨 뒤 이를 오른쪽으로 전달하여 가장 오른쪽 끝에 있는 양자점으로 이동하는 데 성공하였다. 최근에는 이 방식으로 4개의 양자점 큐비트를 구현하였다[19].

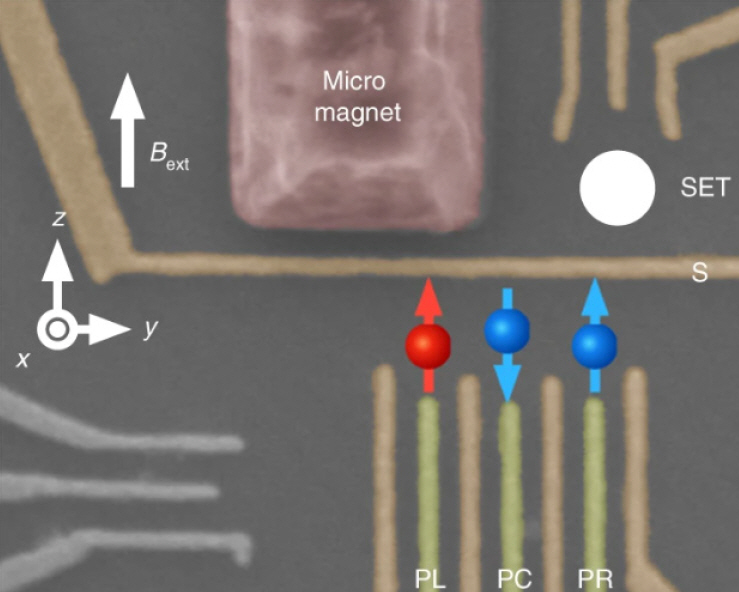

그림 3

하이브리드 큐비트 표면의 전자 현미경 사진. 빨간색이 단일전자 큐비트(왼쪽), 파란색이 전자쌍 큐비트(오른쪽

출처 A. Noiri et al., “A fast quantum interface between different spin qubit encodings.” Nat. Commun., vol. 9, 2018, 5066 (CC BY 4.0)

그림 4

양자점 큐비트의 선형 배열에 대한 전자 현미경 사진 및 전자 이동 모식도

출처 A. R. Mills et al., “Shuttling a single charge across a one-dimensional array of silicon quantum dots.” Nat. Commun., vol. 10, 2019, 1063 (CC BY 4.0)

양자점 큐비트를 일렬로 이어붙이면 확장이 상대적으로 용이하다. 단순하게 생각하면, 무한대로 양자점을 이어붙일 수 있다. 그러나 이 방식은 얽힘 게이트의 사용을 제한한다. 예컨대 양 극단의 큐비트 간에 얽힘 게이트 연산을 하기 위해서는 각각의 큐비트가 물리적으로 인접하도록 이동시킨 뒤, 얽힘 연산을 수행하고 다시 원래의 자리로 위치시켜야 한다.

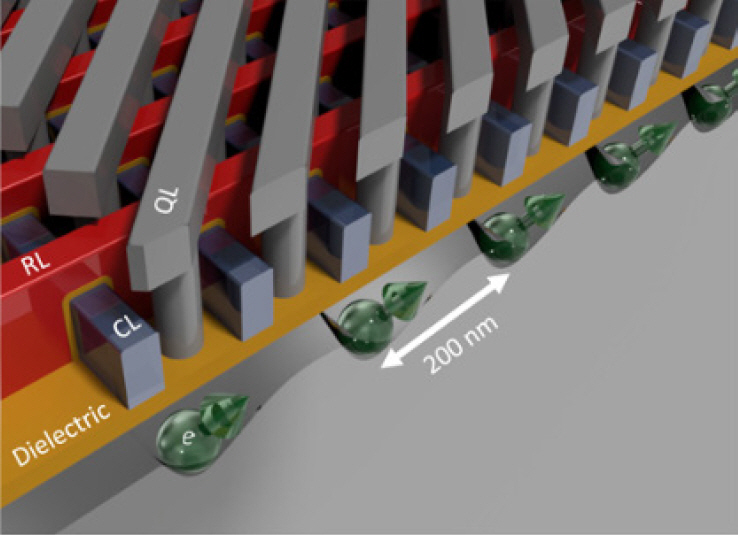

나. 2차원 큐비트 배열을 통한 확장

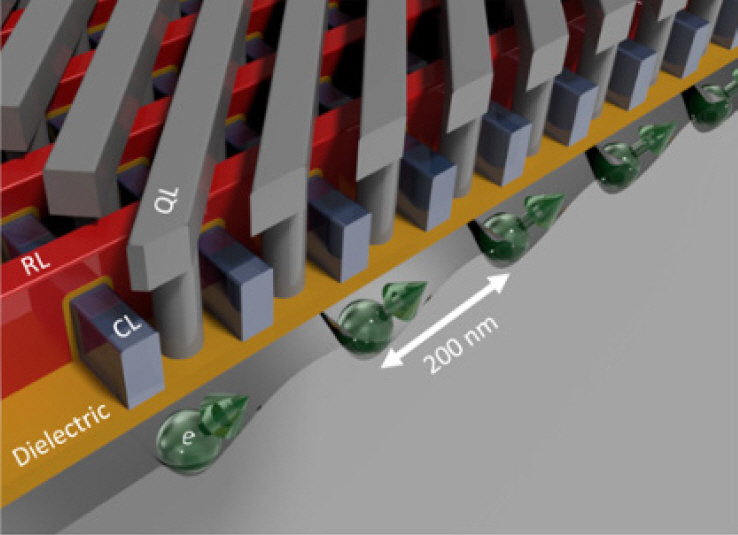

1차원 배열에서 한 발 더 나아가면, 2차원 양자점 배열을 형성할 수 있다. 그림 5에서는 이러한 양자점을 형성하기 위한 전극 구조를 설계하였다. 이 경우에도 단일 양자점을 형성하여 단일 큐비트로 사용할 수 있다. 그러나 아직까지 해당 구조는 실제로 구현되지 않았다.

그림 5

2차원 배열을 통한 양자점 큐비트 수 확장 방법 모식도

출처 R. Li et al., “A crossbar network for silicon quantum dot qubits.” Sci. Adv., vol. 4, 2018, eaar3960 (CC BY-NC 4.0)

위 구조의 가장 큰 장점은 2차원 큐비트 배열로 인하여, 큐비트 수를 획기적으로 확장할 수 있다는 점이다. 이뿐만 아니라 얽힘 게이트를 구현하기 위하여 인접한 큐비트를 위치시키는데 훨씬 적은 비용이 소요된다. 그러나 이를 구현하기 위하여 해결해야 할 문제점이 아직 남아 있다. 우선, 충분히 좋은 절연 재료를 구성해야 한다. 양자점을 구성하기 위한 전극은 수~수십 나노미터 간격으로 매우 가까운 거리로 붙어 있다. 이 전극 간 전자의 이동이 일어나지 않아야 한다. 이런 극한의 환경에서는 아주 작은 전압 차이에 의해서도 번개가 치는 것과 같은 매우 센 전기장이 만들어질 수 있다[20].

1차원 및 2차원 배열은 그럼에도 불구하고 여전히 문제점들이 남아 있다. 첫째로, 다수의 양자점에 전자를 배치하여 변하는 전위를 알고 있어야 한다. 전자의 개수가 많아질수록 각 양자점에 위치한 전위 값이 달라지므로 각 양자점 내부에 1개의 큐비트를 형성하는 것이 어려워진다. 다음으로, 다수의 전극을 어떤 방식으로 효과적으로 제어할지에 대한 문제가 남아 있다. 큐비트의 수가 늘어날수록 제어할 전극의 수가 늘어나기 때문에 하나의 제어선을 이용해 다수의 전극을 제어하는 효과적인 제어 방법이 필요하다.

다. 장거리 정보 전달을 이용한 확장

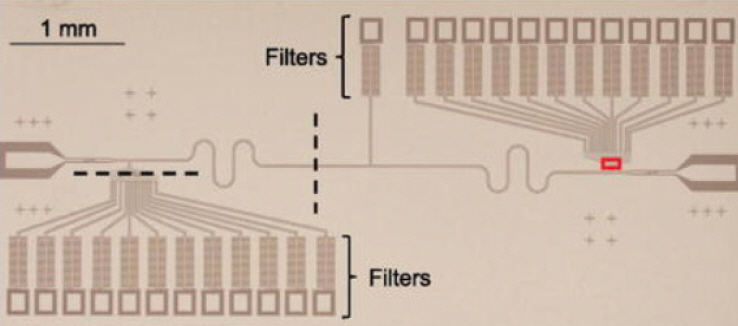

양자점 큐비트의 수를 늘리기 위하여 먼 거리에 있는 큐비트 간 통신을 이용하여 각 지점에 큐비트를 1차원 내지는 2차원 큐비트를 배열할 수 있다. 양자점 큐비트를 제한된 영역 내에서 1차원 혹은 2차원 배열로 확장하더라도 이러한 배열이 물리적인 한계로 인하여 무한대로 확장할 수 없는 지점이 있다. 이때 단일배열 이상으로 큐비트 수를 확장하기 위해서는 장거리에서 양자정보를 전달할 수 있어야 한다. 그림 6은 장거리 간 큐비트의 통신을 위한 구조도이다[21].

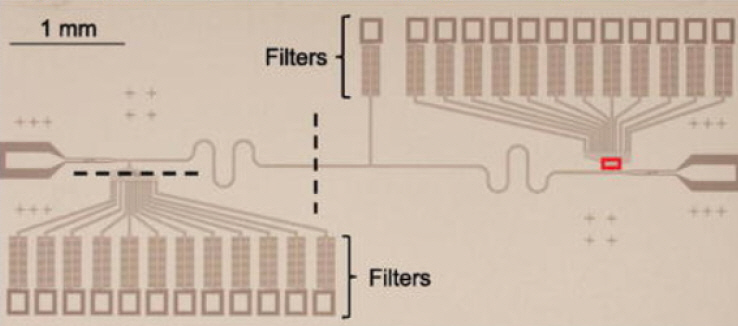

그림 6

공진기를 기반으로 한 장거리 양자정보 전송 소자의 광학 현미경 사진

출처 X. Mi et al., “Circuit quantum electrodynamics architecture for gate-defined quantum dots in silicon.” Appl. Phys. Lett., vol. 110, 2017, 043502 (CC BY 4.0)

최근 연구결과[22]에 따르면, 왼쪽에 있는 양자점에서 오른쪽에 있는 양자점이 연결되어 있는 양자 상태를 만드는 데 성공하였다. 현재까지는 큐비트가 있는 1차원 배열에서 다른 1차원 배열끼리의 상호작용을 보여주는 데 성공하였다. 다만, 이를 이용하여 1차원 배열 간 연산뿐만 아니라, 2차원 배열의 큐비트 간 연산으로 확장하게 된다면 이용 가능한 큐비트의 수를 더 빠르게 늘릴 수 있을 것으로 기대한다.

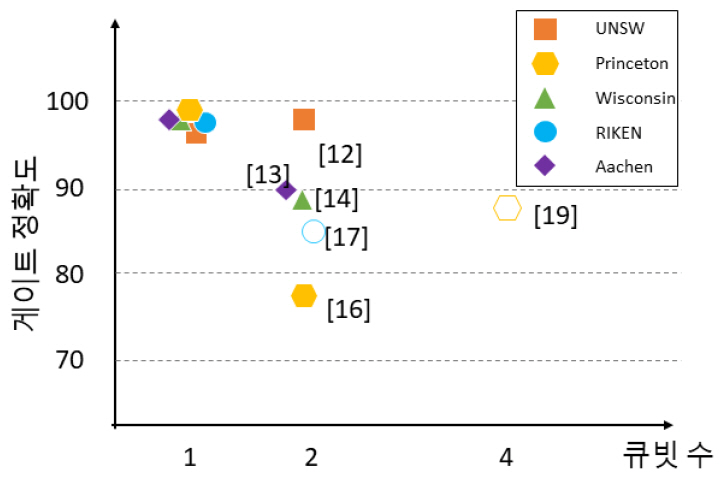

3. 통합적 분석

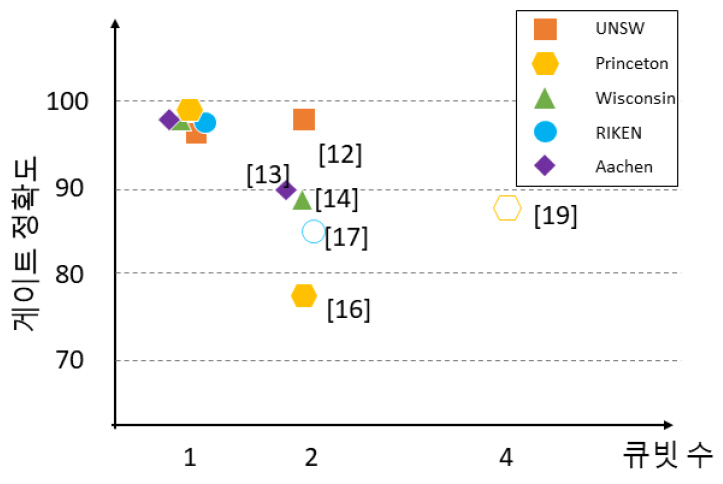

큐비트를 이용하여 양자 알고리즘 등을 수행하여 실용적인 결과를 얻기 위해서는 큐비트 수뿐만 아니라, 개별 연산의 종류 및 정확도, 양자정보의 유지시간 등 여러 가지 평가 요소가 필요하다. 이중 주요하게 평가 요소인 큐비트 수와 게이트 정확도 측면에서 양자점 큐비트의 성능을 평가해 보고자 한다.

본고에서 양자칩의 큐비트 수는 양자칩에서 하나의 시스템으로 평가가 가능한 큐비트의 수로 정의하였다. 즉, 5개의 큐비트가 있다고 하더라도 1개씩 큐비트를 만들어 얽힘 연산이 불가능한 경우는 1개의 큐비트로 평가하였다. 또한 1-2, 3-4, 4-5번 큐비트의 얽힘 연산은 가능하나, 2-3번 큐비트의 얽힘 연산은 불가능한 경우에는 3개로 평가하였다. 다만, 큐비트 칩의 개발 정도가 아직 발전 단계인 점과 제한적인 정보공개인 점을 감안하여, 3개의 큐비트 시스템에서 1-2번과 2-3번이 불연속적으로 연산을 수행했다 하더라도 3개의 큐비트로 간주하였다.

게이트 정확도 또한 본고에서는 2큐비트 얽힘 게이트의 신뢰도(Fidelity)로 정의하였다. 알고리즘 구동을 위한 큐비트의 확장성을 고려하여, 1큐비트 게이트 정확도보다는 2큐비트 게이트 정확도를 고려하였다. 또한, 2큐비트 게이트의 구현 및 정확도 향상이 기술적으로 더 상위 수준에 있음을 반영하였다. 한편, 3큐비트 혹은 N큐비트 얽힘 게이트의 경우에는 현재 얽힘 게이트가 보편적으로 이루어지고 있지 않다고 판단하여, 기준에서 제외하였다.

위 기준으로 비추어 볼 때, 양자점 큐비트는 4개 큐비트가 만들어져 있고, 가장 정밀한 게이트 정확도는 98%이다[12]. 그림 7과 같이 양자점을 위에 설명한 구조로는 2018년도에 2큐비트가 구현되었고, 2019년도에 4큐비트가 구현되어 빠른 속도로 양자점 큐비트가 늘어가고 있다. 뿐만 아니라 정확도 평가결과도 2018년에는 60~70% 수준에서 현재는 98% 수준으로 향상되어 빠르게 기술이 발달하고 있다. 그림 7의 단일 큐비트 게이트 정확도는 얽힘 큐비트 게이트의 정확도의 출처에서 찾을 수 있으며, 대부분의 구현 결과에서 99%를 이상의 게이트 정확도를 보이며, 일부 양자점의 경우는 99.9% 이상의 정확도를 보인다. 향후에는 개별 게이트 수준의 평가가 아닌 임의의 양자회로의 수행 능력을 평가할 수 있는 수준으로 확대되어 종합평가가 이루어져야 할 것이다.

Ⅳ. 반도체 양자점 기반의 양자컴퓨팅 전망

1. 반도체 양자점 큐비트의 전망

양자컴퓨팅을 수행하기 위한 구성요소로서 양자점 큐비트는 충분히 미래 투자가치가 있다. Intel 또한 십만 큐비트를 제작하기 위해 양자점 플랫폼을 활용한 큐비트 제작을 고려하고 있다[23].

양자점 큐비트의 강점은 다음과 같다. 첫 번째로 양자점 큐비트는 확장 가능성이 용이한 플랫폼으로 평가받고 있다. 양자점 큐비트는 실리콘 반도체 공정을 그대로 사용할 수 있다. 이에, 연구개발을 위하여 공정상의 차이가 매우 적어 참고할 선행연구가 많고, 설비의 확장에 따른 비용 소모가 적다. 또한, 반도체 공정의 정밀성 향상이 곧 양자점 공정의 향상으로 이어질 수 있다. 다음으로 양자점의 크기는 대략 100×100nm2으로, 소자의 크기에 비교하여 매우 작아 다수의 양자점을 집적하기에 용이하다. 특히 앞서 분석한 확장 방식이 구체적으로 구현될 경우, 큐비트 수에 대한 확장이 월등히 뛰어날 것으로 기대된다. 게다가 양자점 큐비트는 큐비트간 물리적 거리가 100나노미터로 매우 가깝기 때문에 연산을 곧바로 수행할 수 있으며, 상호작용이 용이하므로 연산속도를 매우 빠르게 만들 수 있다.

2. 범용 양자컴퓨팅의 현재와 미래

양자컴퓨팅은 컴퓨팅 속도와 역량에서 큰 발전을 불러일으킬 것으로 기대하여, 기존의 비트기반 컴퓨터로 계산하기 어려운 문제들에 대한 대안으로 여겨진다. 특히 과학기술 난제 해결, 신산업에의 응용, 양자 인공지능으로의 활용 등 여러 가지 활용분야로의 적용이 기대된다.

현재의 기술수준으로 전 분야에서 혁신적인 기술로 양자컴퓨팅을 활용하는 것은 아직 어렵다. 큐비트를 활용한 계산 시간이 한정적이며, 계산 정확도 또한 높지 않기 때문이다. 현재는 이를 위한 중간 도약 지점으로 오류가 있는 50~100큐비트 수준에서 여러 가지 활용방안을 찾는 NISQ(Noisy Intermediate-Scale Quantum) 시대이며, 현재의 양자컴퓨팅을 활용할 수 있으며 기존의 비트기반 컴퓨터에 비하여 강점을 보일 수 있는 영역을 탐색하고 있다[24].

최종적으로는 양자 정보에 발생한 오류를 정정함으로써 결함이 허용되는 양자컴퓨팅(FTQC: Fault-Tolerant Quantum Computing)으로 도약하고자 한다[25]. 이를 위하여, 양자 오류 정정 부호를 활용하여 이상적인 큐비트로 작용하는 논리적 큐비트를 생성해야 한다. 논리적 연산이 수행 가능하면, 충분한 큐비트를 활용하여 연산량이 비약적으로 커질 것으로 기대하고 있다. 이 시기에는 고전적인 컴퓨터와 마찬가지로, 수행할 큐비트에 적용 가능 수준으로 변환하여 줄 수 있는 컴파일러 기술, 큐비트의 내부 구조를 반영하여 최소한의 연산과 시간을 갖도록 하는 시스템 맵핑 기술, 큐비트의 실시간 배치와 연산을 관장하는 양자컴퓨팅 시스템 운영체제 등이 필요할 것으로 보인다.

V. 결론

본고에서는 양자점 큐비트 기반 양자컴퓨팅의 최근 연구 동향과 발전 가능성에 대하여 살펴보았다. 최근 양자점 큐비트를 활용한 양자컴퓨팅 기술은 빠르게 발전 중이다. 양자점 큐비트는 실리콘을 기반으로 제작되어 산업적인 활용 가능성을 크게 높였고, CNOT과 C-Phase 등 다양한 얽힘 게이트 연산을 구현하였다. 특히, 양자점 큐비트는 단기적 및 장기적 관점에서 다수의 큐비트로의 확장할 수 있는 로드맵을 제시하였다.

미래의 양자컴퓨팅은 현재의 NISQ 시대를 넘어서 결함허용 양자컴퓨팅의 시대로 도달할 것으로 보인다. 결함허용 양자컴퓨팅의 시대에서는 큐비트를 어떤 방식으로 구현하였는지에 대한 것보다는 어떤 방식으로 활용할 것인지가 중요해질 것이다. 그러나 이를 위해서는 큐비트가 충분한 수로 늘어날 수 있고, 간단하고 신속하게 제어할 수 있어야 할 것이다. 반도체 양자점 기반의 큐비트 제작 기술은 아직 주요 큐비트 플랫폼에 비하여는 부족한 편이나, 궁극적으로 이러한 문제점을 가장 빠르게 해결 가능할 것으로 기대된다. 반도체 기술은 우리나라의 먹거리 기술인만큼, 향후 양자컴퓨팅 시대에서도 먹거리 기술로 활용될 수 있을 것으로 기대된다. 다양한 분야에 적용 가능한 양자컴퓨팅 기술의 전반에 걸친 기초 연구 및 원천 기술에 대한 연구가 미래 우리나라의 신산업 동력을 구성할 것을 기대한다.

용어해설

양자컴퓨팅 양자역학적 현상 기반의 양자비트(큐비트)를 이용하는 컴퓨팅 방식으로 비트기반 컴퓨팅에 비하여 빠른 계산이 가능할 것으로 기대됨

양자점 3차원으로 양자구속효과를 보여 전자 등이 공간적으로한 점에 위치할 수 있는 반도체 구조로 인공 원자와 같은 물리현상을 만들 수 있음

얽힘 게이트 2개 이상의 큐비트의 상태가 서로 의존적인(얽힌) 상태로 만드는 양자게이트. 단일큐비트 게이트로는 얽힘 게이트를 만드는 것이 불가능함

약어 정리

E. Martin, "4 Amazing Quantum Computing Applications," DevOps.com, Apr. 20, 2018. [https://devops.com/4-amazingquantum-computing-applications/]

F. Lardinois, "UK government invests $194M to commercialize quantum computing," TechCrunch, June 1, 2019. [http://techcrunch.com/2019/06/13/uk-governmentinvests-194m-to-commercialize-quantum-computing]

Japan S&T Agency, "光·量子飛躍フラッグシッププログラム(QLEAP)," Jan. 2019. [https://www.jst.go.jp/stpp/q-leap/]

S. Chen, "China building world’s biggest quantum research facility," South China Morning Post, Sept. 11, 2017.

J. Kelly, "A preview of Bristlecone, Googles’s new quantum processor," Google AI Blog, Mar. 5, 2018.

M. Friesen et al., "Spin Readout and Initialization in a Semiconductor Quantum Dot," Phys. Rev. Lett., vol. 94, 2004, pp. 037901:1-4.

T. Fujisawa et al., "Allowed and forbidden transitions in artificial hydrogen and helium atoms," Nature, vol 419, 2002, pp. 278-281.

J. R. Petta et al., "Coherent Manipulation of Coupled Electron Spins in Semiconductor Quantum Dots," Science, vol. 309, no. 5744, 2005, pp. 2180-2184.

W. Huang et al., "Fidelity benchmarks for two-qubit gates in silicon,"Nature, vol. 569, 2019, pp. 532-536.

J.M. Nichol et al., "High-fidelity entangling gate for doublequantum-dot spin qubits," npj Quantum Information, vol. 3, 2017, pp. 3:1-3.

T.F. Watson et al., "A programmable two-qubit quantum processor in silicon,"Nature, vol. 555, 2018, pp. 633-637.

J. Yoneda et al., "A quantum-dot spin qubit with coherence limited by charge noise and fidelity higher than 99.9%," Nature Nanotechnology, vol. 13, 2018, pp. 102-106.

D.M. Zajac et al., "Resonantly driven CNOT gate for electron spins," Science, vol. 26, 2018, pp. 439-442.

A. Noiri et al., "A fast quantum interface between different spin qubit encodings," Nature Communications, vol. 9, 2018, pp. 5066:1-7.

A.R. Mills et al., "Shuttling a single charge across a onedimensional array of silicon quantum dots," Nature Communications, vol. 10, 2019, pp. 1063:1-6.

A.J. Sigillito et al., "Site-Selective Quantum Control in an Isotopically Enriched 28Si/Si0.7Ge0.3 Quadruple Quantum Dot," Phys. Rev. Applied, vol. 11, no. 6, 2019, article no. 061006.

R. Li et al., "A crossbar network for silicon quantum dot qubits," Science Advances, vol. 4, no. 7, 2018, pp. eaar3960:1-10.

X. Mi et al., "Circuit quantum electrodynamics architecture for gate-defined quantum dots in silicon," Appl. Phys. Lett., vol. 110, no. 4, 2017, article no. 043502

F. Borjans et al., "Resonant microwave-mediated interactions between distant electron spins,"Nature, 2020, 195

S.K. Moore and A. Nordrum, "Intel’s New Path to Quantum Computing," IEEE Spectrum, June 2018. [https://spectrum.ieee.org/nanoclast/computing/hardware/intelsnew-path-to-quantum-computing]

J. Preskill, "Quantum Computing in the NISQ era and beyond," Quantum, 2018. [https://doi.org/10.22331/q-2018-08-06-79]

그림 3

하이브리드 큐비트 표면의 전자 현미경 사진. 빨간색이 단일전자 큐비트(왼쪽), 파란색이 전자쌍 큐비트(오른쪽

출처 A. Noiri et al., “A fast quantum interface between different spin qubit encodings.” Nat. Commun., vol. 9, 2018, 5066 (CC BY 4.0)

그림 4

양자점 큐비트의 선형 배열에 대한 전자 현미경 사진 및 전자 이동 모식도

출처 A. R. Mills et al., “Shuttling a single charge across a one-dimensional array of silicon quantum dots.” Nat. Commun., vol. 10, 2019, 1063 (CC BY 4.0)

그림 5

2차원 배열을 통한 양자점 큐비트 수 확장 방법 모식도

출처 R. Li et al., “A crossbar network for silicon quantum dot qubits.” Sci. Adv., vol. 4, 2018, eaar3960 (CC BY-NC 4.0)

그림 6

공진기를 기반으로 한 장거리 양자정보 전송 소자의 광학 현미경 사진

출처 X. Mi et al., “Circuit quantum electrodynamics architecture for gate-defined quantum dots in silicon.” Appl. Phys. Lett., vol. 110, 2017, 043502 (CC BY 4.0)

그림 7

양자점 기반의 큐비트 개발 현황

* 실용적 양자컴퓨팅을 위하여 많은 큐비트수와 높은 게이트 정확도가 필요함. 구분을 용이하게 하기 위하여 배열을 조정함. 비어있는 구분 기호는 게이트 정확도 측정 결과가 없음

표 1 단일 게이트 성능 지표

| 구분 | 구동시간 (나노초) | 연산수(1초) | 정확도 | 출처 |

|---|---|---|---|---|

| 1 | 1,400 | 715,000 | 99.9% | [12] |

| 2 | 70 | 1,400,000 | 98.6% | [13] |

| 3 | 500 | 2,000,000 | 98.8% | [14] |

| 4 | 65 | 16,600,000 | 99.9% | [15] |

| 5 | 210 | 4,800,000 | 99.7% | [16] |

- Sign Up

- 전자통신동향분석 이메일 전자저널 구독을 원하시는 경우 정확한 이메일 주소를 입력하시기 바랍니다.