광통신 III-V/Si 레이저 다이오드 기술 동향

III-V/Si Optical Communication Laser Diode Technology

- 저자

-

김호성광통신부품연구실 hosung.kim@etri.re.kr 김덕준광통신부품연구실 djkim@etri.re.kr 김동철광통신부품연구실 dchankim@etri.re.kr 고영호양자광학연구실 yhko@etri.re.kr 김갑중양자광학연구실 k.j.kim@etri.re.kr 안신모광통신부품연구실 shinmo.an@etri.re.kr 한원석광통신부품연구실 wshan@etri.re.kr

- 권호

- 36권 3호 (통권 190)

- 논문구분

- 차세대 반도체

- 페이지

- 23-33

- 발행일자

- 2021.06.01

- DOI

- 10.22648/ETRI.2021.J.360303

본 저작물은 공공누리 제4유형: 출처표시 + 상업적이용금지 + 변경금지 조건에 따라 이용할 수 있습니다.

본 저작물은 공공누리 제4유형: 출처표시 + 상업적이용금지 + 변경금지 조건에 따라 이용할 수 있습니다.- 초록

- Two main technologies of III-V/Si laser diode for optical communication, direct epitaxial growth, and wafer bonding were studied. Until now, the wafer bonding has been vigorously studied and seems promising for the ideal III-V/Si laser. However, the wafer bonding process is still complicated and has a limit of mass production. The development of a concise and innovative integration method for silicon photonics is urgent. In the future, the demand for high-speed data processing and energy saving, as well as ultra-high density integration, will increase. Therefore, the study for the hetero-junction, which is that the III-V compound semiconductor is directly grown on Si semiconductor can overcome the current limitations and may be the goal for the ideal III-V/Si laser diode.

Share

Ⅰ. 서론

실리콘 반도체 관련 산업은 끊임없는 연구 개발을 통하여 소재 제조 기술, 소자 공정 기술 및 공정장비 등 관련 모든 분야에서 기술의 정점에 도달하여 우리 일상을 빠르게 변화시키고 있다.

최근 스마트폰, 5G, 전기자동차, 자율주행, 인공지능 등 새로운 산업이 급부상하면서 에너지 효율 증대, 빅데이터 전송, 고속 데이터 처리 등에 대한 요구가 높아지면서 실리콘 반도체만으로는 극복할 수 없는 물질 한계에 도달하게 되었다. 이로 인하여 실리콘 물질의 한계를 극복하기 위한 이종 반도체와 융합하려는 시도가 빠르게 발전하고 있다. 특히, 실리콘 반도체로는 구현할 수 없는 광원 부분에 있어서 III-V 화합물 반도체와 이종접합연구가 빠르게 발전하고 있다. 실리콘 반도체 소자와 화합물 반도체 소자를 집적하는 방법으로 1) 실리콘 기판상에 III-V 화합물 반도체를 직접 적층하는 직접성장기법(Direct Growth Epitaxy), 2) 실리콘 기판의 특정 위치에 화합물 반도체 소자를 접합하는 소자접합(Chip Bonding)과 실리콘 기판상에 III-V 화합물 반도체 완충층을 이식 후 소자를 재성장하는 재성장기법(Regrowth Epitaxy) 등이 있다. 실리콘 포토닉스분야에서는 광원소자접합 기법을 활용한 상용제품이 출시되었고, 최근에는 재성장기법을 활용한 기술도 빠르게 발전하고 있다. 그러나 직접 성장기법의 경우에는 실리콘과 화합물 반도체의 기본물성(격자상수, 열팽창계수) 등의 차이로 인하여 집적성장을 위해서는 아직도 해결해야 할 문제가 많이 있다. 집적성장법은 광소자 산업에 있어서 고가의 소면적 화합물 반도체 기판을 저렴한 대면적 실리콘 기판으로 대체할 수 있으므로 화합물 반도체 소자 생산 단가를 획기적으로 낮출 수 있는 파급력을 가지고 있어 광통신 분야에서도 매우 중요한 연구 분야이다.

본 고에서는 실리콘 기판상에 III-V 화합물 반도체를 이용한 광통신용 레이저 광원을 구현하는 다양한 이종접합 기술에 대한 연구 동향에 대하여 알아보고자 한다.

Ⅱ. 기술 동향

1. Direct Epitaxial Growth

가. III-V/Si 성장 기술

빛을 발광시키는 데 특화된 III-V 화합물 반도체를 Si 기판 위에 직접적으로 성장하는 기술은 여러 가지 문제가 있다. III-V 화합물과 Si 기판의 격자 상수 불일치(Si 기판과 GaAs 물질 간의 4% 차이, Si 기판과 InP 물질 간의 8% 차이), 물질의 열팽창 계수의 차이(Si: 2.6×10-6K-1, GaAs: 5.7×10-6K-1, InP: 4.56×10-6K-1) 그리고 격자의 극성 불일치(III-V는 극성 반도체, Si는 비극성 반도체)가 가장 대표적인 문제이다. 이러한 많은 문제를 완화하는 기술이 활발하게 전 세계적으로 연구 중에 있다. 가장 대표적으로 극성 불일치에 의한 Anti-Phase Boundary(APB) 문제를 해결하기 위해 Si 기판으로 off cut 기판을 이용하는데, 이러한 해결책은 실리콘 기판 제작의 공정 단가를 높이게 되고 CMOS 공정과 호환되기 어렵다. 격자 상수 불일치와 물질 간의 열팽창 계수 차이는 결함(Dislocation)을 발생시키는데, 이 결함은 소자 특성을 저하시키는 주된 요인이 된다. 무엇보다 열팽창 계수 차이에 의한 보잉(Bowing)과 크랙(Crack) 발생은 소자 공정의 수율을 낮추고 소자 특성을 저하시키게 된다.

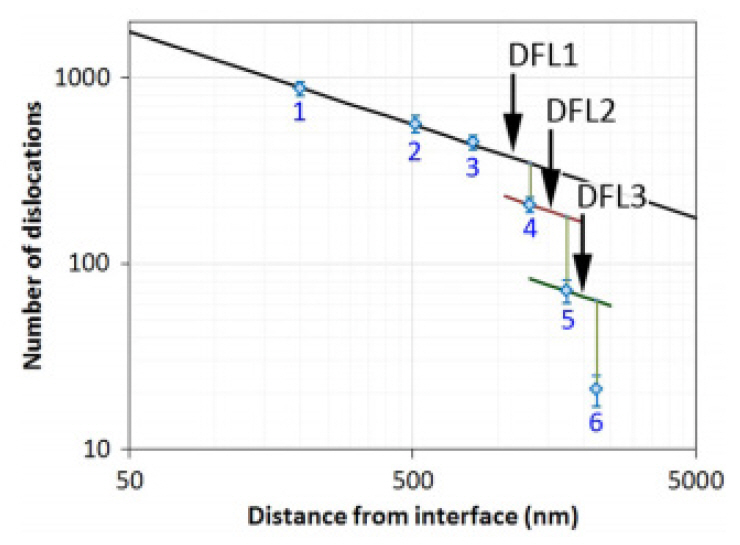

이러한 직접성장방법 대신 웨이퍼 본딩(Wafer Bonding)을 이용하여 III-V 화합물과 Si를 집적화하는 연구도 활발히 진행 중이다. 하지만 직접성장 방식인 모놀리식(Monolithic) 성장은 저비용, 고수익 및 대량 생산으로 이어질 것으로 전망되기 때문에 더욱 선호 받는 기술이다. 직접성장은 버퍼층을 최소의 두께로 얼마나 효율적으로 결함을 최소화하는 것이 핵심 기술이다. 표 1은 버퍼를 성장할 때 사용하는 기술들을 정리한 표이다. 첫 번째에서 세 번째까지의 기술들은 결함을 줄이기 위해 사용하는 기술들이며, 네 번째에서 일곱 번째까지의 기술들은 APB를 최소화하기 위해 사용하는 기술이다. 2단 성장 기술은 Si 기판 위에 낮은 온도에서 GaAs Seed 층을 수 nm 두께 성장한 뒤 고온에서 성장을 시작하는 기술 방법이다. 저온에서 성장을 하는 이 첫 단계는 얇은 비정질 GaAs 층의 고체상 결정화라고 할 수 있다. 열처리 기법은 MOCVD(Metal Organic Chemical Vapor Deposition) 챔버 내에서 기판 온도를 300℃에서 900℃를 3~5회 반복하는 방법으로 결함을 감소하는 데 매우 효과적이다. GaAs와 Si 기판과의 큰 열전도 계수 차이로 인해, 큰 온도 변화를 받는 GaAs 층은 압축 상태와 확장 상태가 주기적으로 변하면서 결함의 방향을 반대로 바꾸게 되어 결함 밀도가 감소하게 된다. 결함억제층(DFL: Dislocation Filter Layer)은 얇은 초격자 층을 버퍼 성장 시 삽입하는 방법으로 최근에는 Strained InGaAs/GaAs DFL 구조가 가장 많이 사용되고 있다. Strained DFL 구조에서 Relaxation이 일어나면 Misfit Dislocation이 발생하는데, Threading Dislocation이 Misfit Dislocation과 만나면 방향을 바꾸거나 소멸할 수 있는 가능성이 많아지기 때문이다. 그림 1은 DFL 세트마다 줄어드는 Threading Dislocation Density(TDD)를 ECCI로 측정하여 나타낸 그래프이다[12]. APB를 최소화하기 위한 방법으로 여러 가지 방법이 사용되고 있는데, MOCVD 챔버 안에서 insitu 방식으로 문제를 해결한 방법은 아직 연구가 미미하다.

표 1 III-V/Si 버퍼 성장 기술

| 기술 | 연구방법 | 효과 |

|---|---|---|

| 2단 성장(two-step growth) | 처음 III-V 성장 단계에서 저온 성장 후 고온 성장[1-5] | 결함 감소 |

| 열처리(thermal cycle annealing) | 300~900℃ 주기적 열처리를 3~5회 반복[6-8] | |

| 결함억제층(dislocation filter layer) | 초격자 구조를 버퍼층에 삽입[9-13] | |

| Si off-cut 기판 이용 | Si off-cut 기판 위 성장[14-16] | APB 억제 |

| Ge 버퍼 이용 | Ge 버퍼를 Si 기판 위 성장[17,18] | |

| GaP/Si 기판 이용 | 얇은 45nm GaP layer를 Si 기판 위 성장[19,20] | |

| V-groove Si 기판 이용 | 나노 스케일의 V-groove를 Si 기판 위에 형성[21-24] |

그림 1

DFL 마다 줄어드는 TDD를 나타낸 그래프

출처 I. George et al., “Dislocation filters in GaAs on Si,” Semicond. Sci. Technol. vol. 30, no. 11, 2015, 114004. CC BY 3.0.[12]

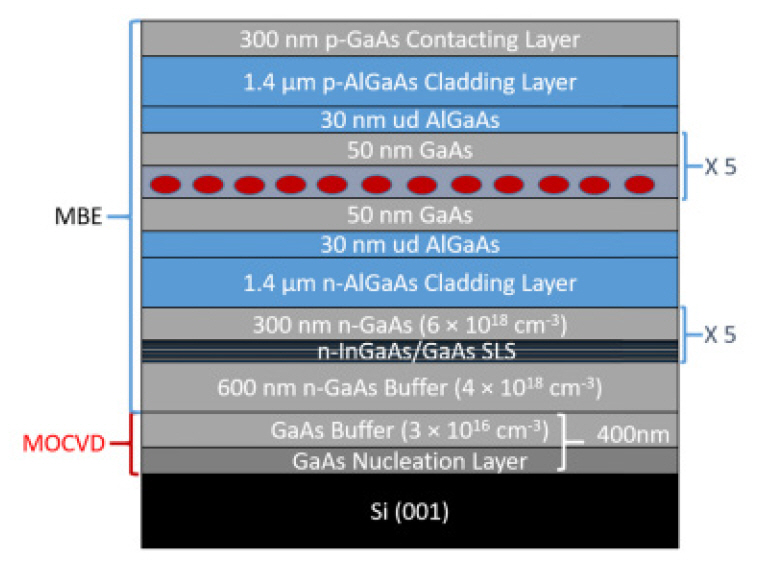

나. 1.3μm O-band 레이저

영국의 UCL과 프랑스의 Grenoble Alpes는 최초로 InAs/GaAs 양자점 레이저 소자 박막을 MOCVD와 MBE(Molecular Beam Epitaxy)를 사용하여 Si(001) 기판 위에 성장 및 발진에 성공하였다[26]. MOCVD로는 Si 기판 위 GaAs Buffer를 성장하였고, MBE로는 양자점 레이저 구조를 성장하였다. 양자점은 양자점 고유의 물리적 특성으로 인하여 레이저 구동 문턱전류가 낮다는 장점도 있지만 Si 기판 위에서 레이저 다이오드를 성장할 때, 필연적으로 발생하는 Threading Dislocation으로부터 양자우물에 비해 영향이 다소 적다는 장점이 있다. Si 기판은 BOE(Buffered Oxide Etch) 용액에 담가 산화막을 제거한 뒤, 900℃에서 열로 산화막을 다시 한번 제거하고 2단 성장 방법으로 GaAs 버퍼를 성장하였다. 그 뒤 MBE 챔버에서 Threading Dislocation을 차단하는 InGaAs/GaAs DFL를 이용하여 GaAs 버퍼를 성장하고 위에 Dots-in-well(DWELL) 구조를 활성층으로 하는 양자점 레이저 다이오드 구조를 성장하였다(그림 2).

그림 2.

Si(001)에서 성장한 양자점 레이저 구조의 개략도

출처 S. Chen et al., “Electrically pumped continuous-wave 1.3μ DWELL 구조를 이용하여 Si 기판상에 1.3μm에서 m InAs/GaAs quantum dot lasers monolithically grown on on-axis Si(001) substrates,” Optics Express, vol. 25, no. 5, 2017, pp. 4632–4639, CC BY 4.0.[26]

소자는 일반적인 포토리소그래피와 금속 증착 과정을 통해 완성하였다. GaAs 기판 위에 성장한 양자점 레이저 다이오드와 Si 기판 위에서 성장한 레이저 다이오드의 문턱전류밀도는 각각 210A/cm2와 425A/cm2으로, Si 기판 위에서 성장한 양자점 레이저 다이오드의 문턱전류밀도가 2배 높다. 경사 효율 및 외부 양자 효율도 GaAs와 Si에서 각각 0.12W/A, 12.7%와 0.068W/A, 7.2%로 GaAs에서 2배 특성이 우수하다. 이는 양자점을 사용하더라도 Si 위 GaAs를 성장할 때 발생하는 결함으로 인해 소자 특성이 저하가 존재함을 알 수 있다. Si 소자는 CW 모드에서 25℃ 상온에서 42mW의 출력을 보였고 100℃까지 발진 특성을 보였다.

MBE 장비는 MOCVD 장비보다 물질의 증착 두께를 Monolayer 두께로 매우 정밀하게 조절하는 것이 가능하기 때문에 정확한 두께를 요구하는 양자점 성장은 MBE를 사용하는 것이 유리하다. 이러한 이유로 양자점 레이저 다이오드는 MBE를 이용한 연구가 활발히 진행되었다. 하지만 MBE는 대량 생산에 한계가 있다. 최근 미국 UCSB 대학에서 Si(001) 기판 위 V-groove를 나노미터 스케일로 형성한 기판을 이용하여 MOCVD 장비만을 이용해 양자점을 성장한 연구 결과가 발표되었다[21]. V-groove 방식은 나노미터 수준의 V-groove 형성을 위해 EUV(Extreme Ultraviolet) 공정 또는 E-beam Lithography가 필요하다는 단점이 있다.

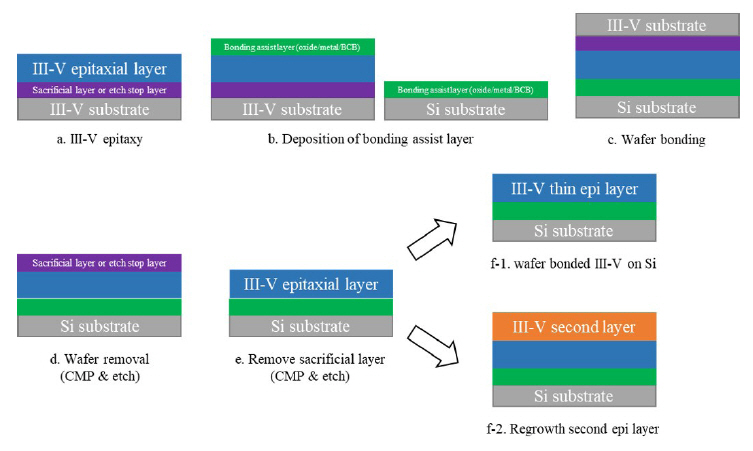

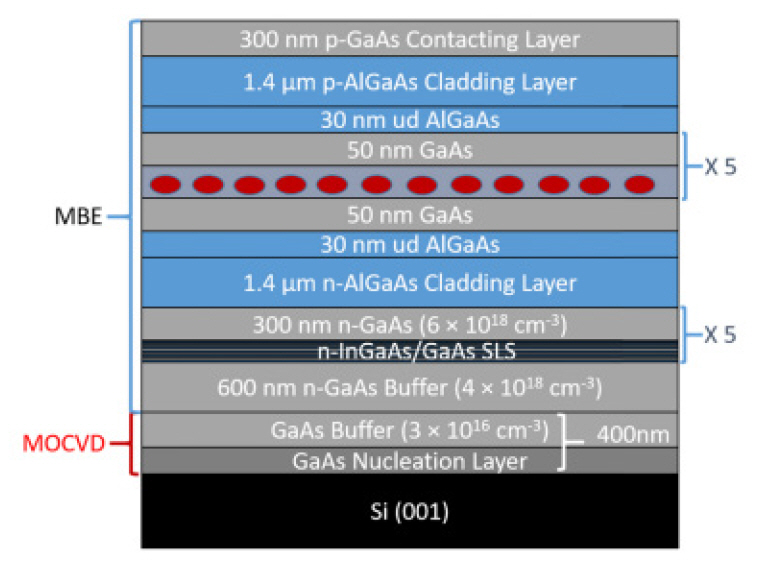

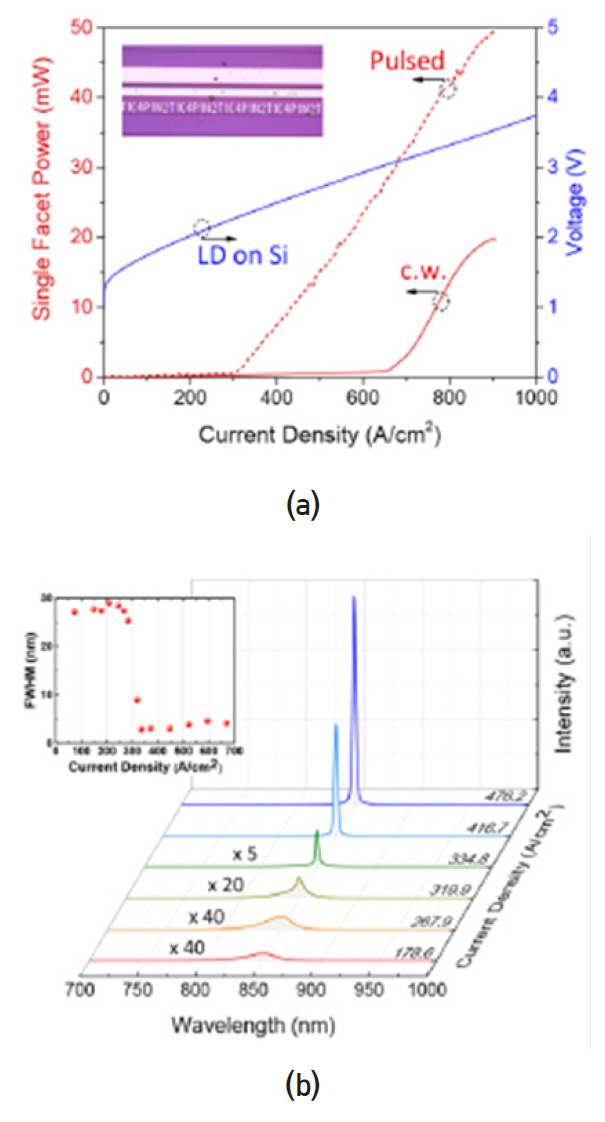

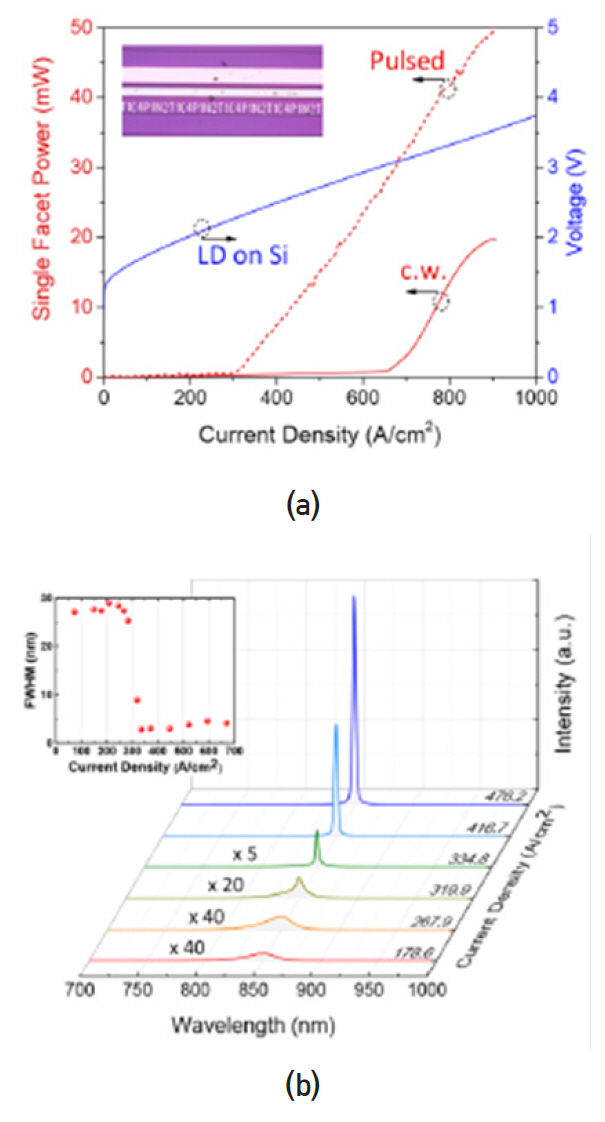

ETRI에서는 Si(001) 4° off cut된 기판을 이용하여 직접성장방법을 이용하여 그림 3과 같이 Si 기판 상에 850nm 양자우물 레이저 구조를 성장하고 발진하는 데 성공하였고[14,15], 현재는 InAs/InGaAs DWELL 구조를 이용하여 Si 기판상에 1.3μm에서 발진하는 양자점 레이저 다이오드를 연구하고 있다. 또한 Si(001) Exact 기판 위 GaP를 성장하여 APB 문제를 해결하여 양자점 레이저 다이오드를 제작하는 연구도 진행 중이다.

그림 3.

(a) 실리콘 GaAs/AlGaAs 레이저 다이오드의 LIV 그래프 (b) 실리콘 GaAs/AlGaAs 레이저 다이오드의 발진 스펙트럼

출처 Y.H. Ko, K.J. Kim, and W.S. Han, “Monolithic growth of GaAs laser diodes on Si(001) by optimal AlAs nucleation with thermal cycle annealing,” Optical Materials Express, vol. 11, no. 3, 2021, pp. 943–951. © 2021 Optical Society of America.[15]

다. 1.55μm C-band 레이저

일반적으로 1.55μm에서 발진하는 III-V 레이저 소자는 InP 기판 위에서 양자우물 또는 양자점을 이용하여 성장하는데, 실리콘 기판 위 1.3μm InAs/GaAs 양자점 레이저와 같은 원리로 1.55μm InAs/InP 양자점을 이용하여 실리콘 기판 위에 레이저를 만들 경우 양자 우물에 비해 결함에 대한 높은 내성과 우수한 광학적 특성을 가진 소자를 제작할 수 있다. InP 물질과 Si 물질 간의 격자 상수 차이가 8%로 크게 차이나기 때문에 InP 물질을 Si 기판 위에 바로 성장하게 되면 격자 부정합으로 인해 고품질의 단결정막이 성장이 되지 않게 된다. 이를 극복하기 위해 GaAs 버퍼를 먼저 2~3μm 성장한 뒤 InP 버퍼를 성장하여 InAs/InP 양자점 레이저 다이오드를 성장하는 방식을 사용한다.

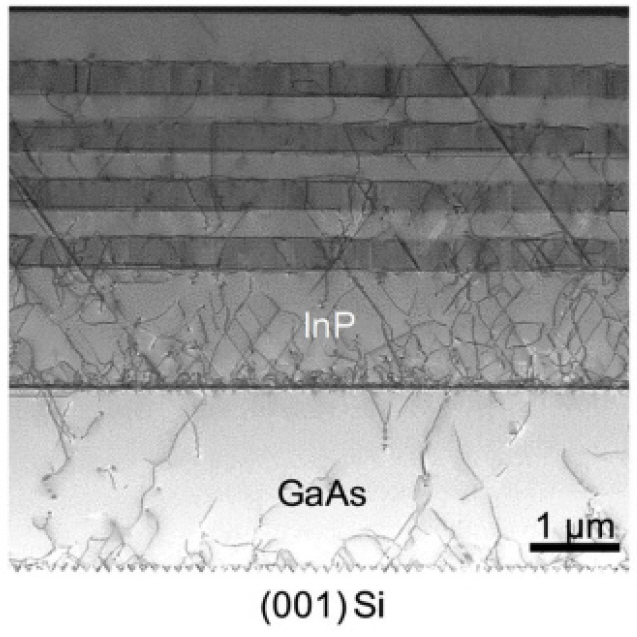

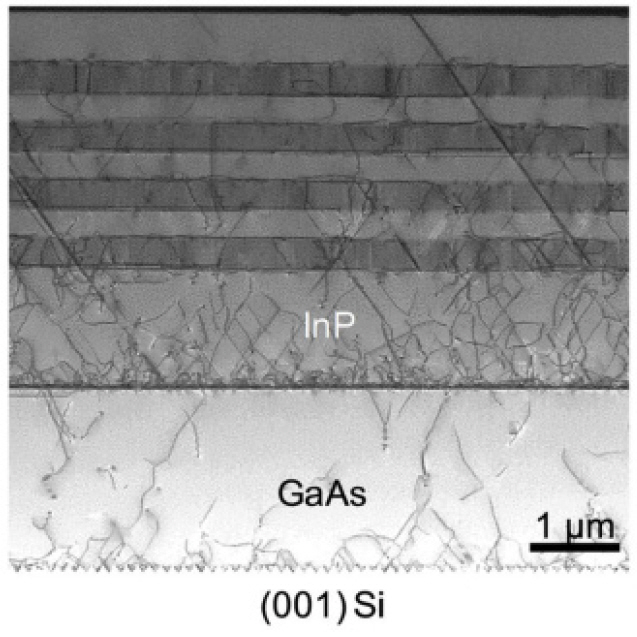

미국 UCSB 대학에서는 InGaAsP MQW를 on-axis 실리콘 V-groove가 형성된 기판 위에 직접 성장하여 1.55μm에서 CW 모드로 발진하는 레이저 다이오드를 제작하는 데 성공하였다[22]. V-grooved Si 기판은 SiO2 마스크를 이용하여 나노 미터 스케일의 간격을 가지는 평행 스트라이프에 수산화칼륨 용액으로 식각하면 제작이 가능하다. 나노 패턴된 V-grooved Si 기판은 APB 형성을 억제할 뿐만 아니라 dislocation의 종횡비 트래핑(Aspect Ratio Trapping)을 가능하게 한다. InP 버퍼를 성장하기 전에 중간 버퍼로 GaAs 2μm를 성장한 뒤, InP 버퍼는 tree step 성장 모드로 처음에 seed 형성을 위해 435℃에서 30nm 성장하고 540℃에서 45nm를 성장하여 평탄화한 뒤, 온도를 630℃까지 올려 고온에서 1μm 두께의 InP를 성장한다. InGaAs/InP DFL 구조와 300nm InP 스페이서 층을 가진 구조를 4~5회 반복해 전체 InP 버퍼의 두께가 4μm 정도 되게 성장한다. 그림 4는 3.9μm InP 버퍼를 V-grooved Si 기판 위 성장한 단면의 STEM 이미지이다.

그림 4.

V-grooved (001) Si에서 성장한 3.9 μm InP 버퍼의 단면 STEM 이미지

출처 B. Shi et al., “Continuous-wave electrically pumped 1550 nm lasers epitaxially grown on on-axis (001) silicon,” Optica, vol. 6, no. 12, 2019, pp. 1507–1514. © 2019 Optical Society of America.[22]

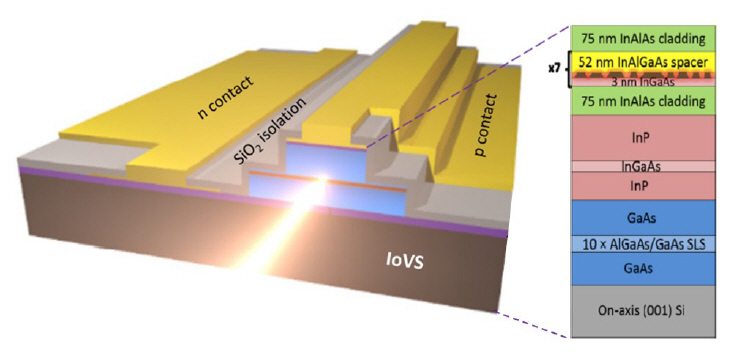

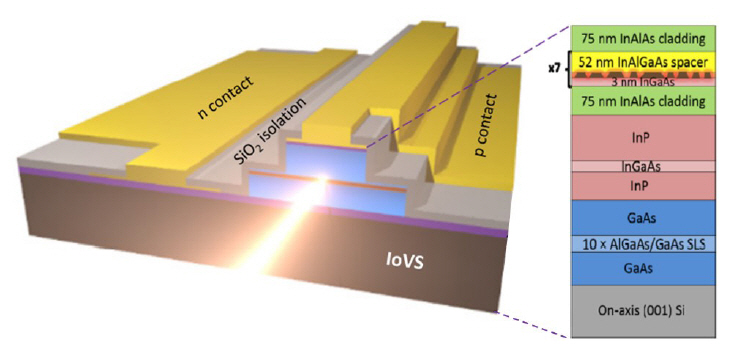

InP 버퍼를 성장한 뒤, 7층의 InGaAsP/InGaAsP MQW를 활성층으로 가지는 레이저 구조를 성장하였고, 일반적인 Ridge Waveguide 레이저 다이오드를 제작하였다. 제작한 레이저 다이오드의 문턱 전류밀도는 2.05kA/cm2이고 18mW의 출력을 보였고 CW 모드에서 65℃까지 동작특성을 보였다.

홍콩 과학 기술 대학교(HKUST)에서는 InAs/InP 양자점 레이저를 On-axis 실리콘 V-groove가 형성된 기판 위에 직접 성장하여 1.55μm에서 발진하는 레이저를 발표하였다[23]. InP 버퍼를 형성하는 것은 기본적으로 GaAs 버퍼를 형성한 뒤, Straind InGaAs/InP DFL을 삽입한 InP 버퍼를 성장하여 TDD를 최대한 줄인 후, 5층의 InAs 양자점을 활성층으로 가지는 Ridge Waveguide 구조를 제작하였다(그림 5). 제작한 레이저 다이오드는 문턱전류밀도 1.6kA/cm2, 출력 110mW 그리고 펄스 모드에서 80 ℃까지 동작특성을 보였다. 1.55μm 실리콘 레이저는 InP/GaAs/Si에서 발생하는 상대적으로 많은 결함으로 인해 양자점을 사용하더라도 문턱전류밀도가 매우 높은 특성을 보인다.

그림 5.

실리콘 기판상의 InAs/InAlGaAs/InP 양자점 레이저 개략도 및 구조 (그림은 출처의 논문에서 수정함)

출처 Reproduced from S. Zhu et al., “Room-temperature electrically-pumped 1.5μm InGaAs/InAlGaAs laser monolithically grown on on-axis (001) Si” Opt. Express, vol. 26, no. 11, 2018, pp. 14514–14523[24], S. Zhu et al., “Parametric study of high-performance 1.55μm InAs quantum dot microdisk lasers on Si” Opt. Express, vol. 25, no. 25, 2017, pp. 31281–31293[25] © 2021 Optical Society of America.

2. Wafer Bonding (Non-Epitaxial Integration Techniques)

가. 웨이퍼 본딩을 이용한 박막 전사 기술

웨이퍼 본딩은 벌크 또는 III-V 화합물 반도체 박막을 다양한 기판에 붙이는 것을 의미한다. 웨이퍼 본딩은 상온에서 서로 다른 두 반도체를 직접 결합할 수 있으며 이를 위해, 거울면과 같은 매우 깨끗한 표면이 필요하다. 원자적으로 평평한 두 면을 웨이퍼 본딩을 이용하여 붙이면 표면에서 반데르발스(Van-der-Waals) 힘을 이용해 원자들끼리 결합하여 붙게 된다. 두 표면을 성공적으로 직접 결합하려면 평탄화 공정 과정을 포함하여, 표면의 오염 제거, 표면 거칠기 최소화 그리고 조심스러운 기판 제거 공정이 필요하다.

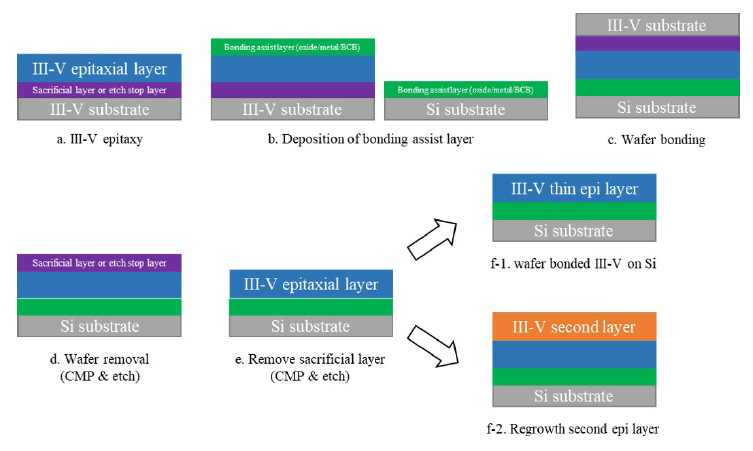

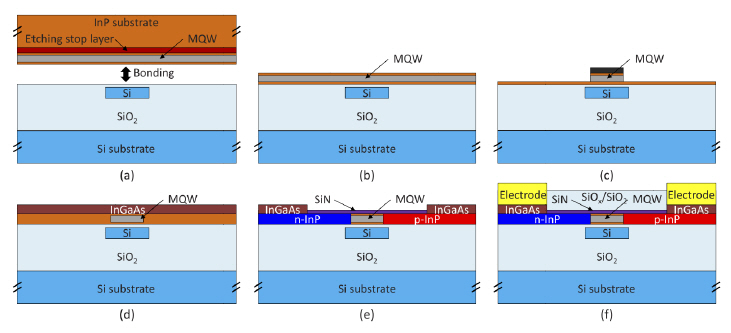

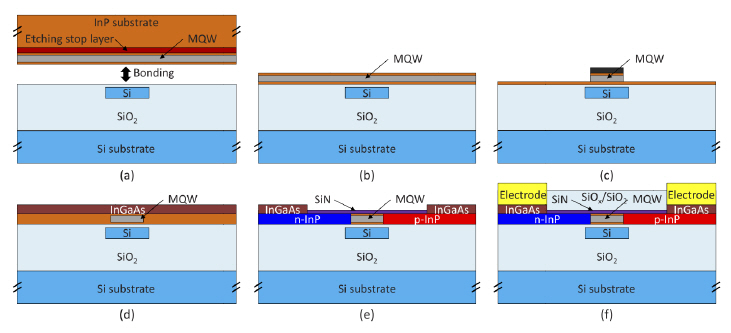

그림 6은 III-V 박막을 Si 기판에 전사하는 공정 과정을 나타낸 모식도이다. 이 기술의 또 다른 핵심 기술은 III-V 기판을 제거하는 방법이다. 기판을 제거하기 위해 III-V 기판 위에 선택적 식각이 가능한 얇은 희생층(Sacrificial Layer)을 성장하거나, 기판만 식각되고 박막은 식각되지 않은 소위 Etch Stop Layer를 성장하는 것이 필수이다. 이 층은 III-V 기판과 격자 상수가 동일한 박막층을 사용하여야 그 위에 성장하는 실제 소자의 결정성에 해로운 영향을 미치지 않는다. 일반적으로 GaAs 기판을 사용 시 AlAs 층을 사용하고, InP 기판의 경우 InGaAs Etch Stop Layer를 사용한다. AlAs 층의 경우 Epitaxial Lift-Off(ELO) 공정에서는 희생층으로 사용되며, 단순 기판 제거 공정 과정 에서는 Etch Stop Layer로 사용이 가능하다. 성장이 완료된 III-V 기판과 Si 기판 위에 옥사이드, 메탈 또는 폴리머 물질인 BCB 와 같은 접착을 도와주는 물질을 활용한 물질을 증착한 뒤 본딩을 할 수 있다(그림 6(b,c)). 접착 재료를 이용한 접착 본딩 방법을 활용할 경우 직접 본딩 방법에 비해 열과 기계적 힘에 대해 안정적이다는 장점이 있다.

III-V 기판을 제거하기 위해 기판의 뒷면을 Lapping 공정으로 기판을 얇게 한 다음 선택적 식각 공정 과정을 통해 기판을 제거(그림 6(d))한 후 Etch Stop Layer만 다시 선택적 식각(그림 6(e))하여 전사하고자 하는 에피층만 본딩 후 식각 공정을 통해 Si 기판 위에 남게 한다(그림 6(e)). 그림 6(f1)과 같이 전사된 에피층 위에 소자를 제작할 수 있고, 그림 6(f2)와 같이 재성장을 통해 원하는 소자 구조를 성장할 수도 있다.

웨이퍼 본딩은 직접성장방법에 비해 추가적인 공정 과정이 필요하다는 단점이 있지만, 성공적으로 전사가 된 경우 결함이 없는 우수한 특성을 가지는 소자를 flexible 기판을 포함한 어떠한 다른 기판에서 구현할 수 있다는 장점이 있다.

나. 웨이퍼 본딩을 이용한 하이브리드 실리콘 레이저

하이브리드 실리콘 레이저라 불리는 실리콘 위 III-V 물질을 웨이퍼 본딩 기술을 이용하여 이종 접합한 레이저는 UCSB에서 처음으로 제안되었고 광펌핑 방식으로 실현되었다[27]. InAlGaAs MQW 구조를 가지는 III-V 물질과 미리 광도파로가 형성된 실리콘 웨이퍼는 저온 산소 플라즈마 웨이퍼 본딩을 이용하여 붙여졌으며, 레이저의 cavity는 실리콘 도파로의 연마된 양단면이 되었다. 웨이퍼 본딩을 이용할 경우, Stamp 방식 또는 Roller 방식을 이용하는 경우 보다 III-V 층 전사 시 매우 엄격한 정렬이 필요 없이, III-V 층을 웨이퍼 단위로 전사한 뒤 실리콘 기판 위에서 리소그라피 공정을 통해 소자를 제작할 수 있다는 장점이 있다. 웨이퍼 본딩 방법 중 반도체 끼리 직접 본딩하는 Direct 웨이퍼 본딩(Molecular Wafer Bonding)을 이용하여 FPLD[28] 및 DBR laser[29], DFB laser[30], Microring Laser[31], MLL[32]를 제작하여 발표하였고, 벨기에 IMEC에서는 BCB 물질을 이용한 Adhesive 본딩을 이용해 FPLD[33], DFB Laser[34]를 제작해 발표하였다. BCB 물질 이외에도 일본에서 처음으로 메탈을 이용한 본딩으로 QDLD on Si을 발표하였고[35], 이후 FPLD를 제작해 발표하였다[36]. 표 2에 다양한 웨이퍼 본딩 방식을 이용하여 제작한 하이브리드 실리콘 레이저를 묘사하였다.

표 2 웨이퍼 본딩 방식을 이용한 대표적 하이브리드 실리콘 레이저

다. 웨이퍼 본딩과 재성장방법을 이용한 III-V/Si 레이저

전체 p-i-n 다이오드 구조가 수직 방향으로 존재하는 III-V 박막을 Si 또는 SOI(Silicon-On-Insulator) 기판에 본딩한 후 III-V 박막의 식각 및 메탈 전극 형성 공정을 진행하여 레이저 다이오드 소자를 제작하는 Hybrid Silicon Laser 기술 이외에도, Si 또는 SOI 기판 상부에 웨이퍼 본딩 기술을 적용하여 두께가 1μm 이하로 얇은 InP 박막을 형성한 후 레이저 다이오드 제작에 필요한 활성층이 포함된 여러 가지 III-V 물질의 재성장 공정을 추가하여 레이저 다이오드를 제작하는 본딩/재성장 결합 기술이 알려져 있다.

일본 소피아 대학은 Si 기판에 1μm 두께의 InP 박막을 형성한 후 III-V 재성장 공정을 추가하여 Vertical p-i-n 구조의 1.2μm 파장에서 발진하는 InGaAsP 레이저 다이오드를, 그리고 미국 HP는 SOI 기판에 150nm 두께의 n-InP 박막을 형성한 후 MQW 활성층이 포함된 재성장 공정을 추가하여 1.3μm 파장에서 발진하는 InGaAsP 레이저 다이오드를 제작한 결과를 각각 보고하였다[37,38]. 한편, 이러한 Vertical p-i-n 구조에서는 III-V 광도파로 모드가 상부 p-contact 메탈의 영향을 받지않도록 해야 하는 설계상의 이유로 전체 III-V 박막의 두께가 일반적으로 2μm를 초과하게 된다. 그리고 이러한 두꺼운 III-V 박막의 경우에는, 600℃ 전후의 재성장 온도에서 냉각되는 과정에서 결함이 급격하게 생성될 우려가 있으며 SOI 기판에 형성되는 Si 광도파로의 두께를 실리콘포토닉스 소자에서 일반적으로 사용되는 220nm가 아닌 450~500nm로 설계하여 Si 광도파로의 유효 굴절률을 III-V 광도파로의 유효 굴절률에 근접시키는 방식을 취하고 있다.

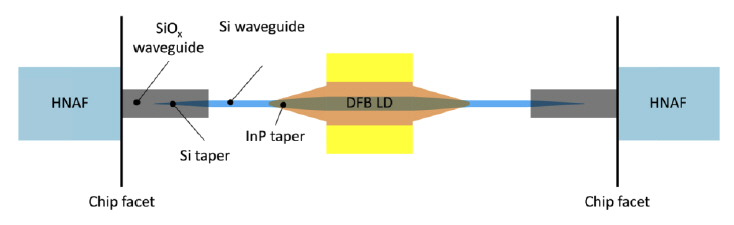

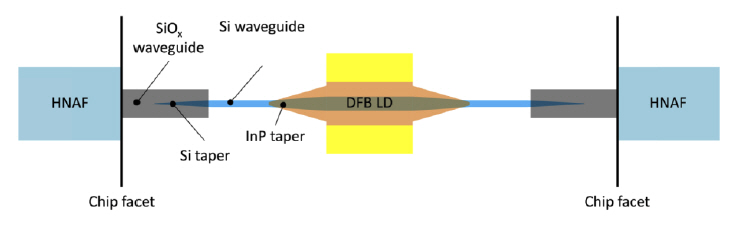

일본 NTT는 Si 광도파로의 두께가 220nm인 경우에도 하부 Si 광도파로와 상부 III-V 광도파로의 유효 굴절률 매칭이 가능한 본딩/재성장 결합 기술을 적용하여 멤브레인 레이저 다이오드 소자 및 광집적 소자를 개발한 결과를 2014년부터 지속적으로 보고하고 있다[39-41]. 이러한 NTT의 본딩/재성장 결합 기술에 사용되는 전체 III-V 박막의 두께는 이론적으로 600℃ 전후의 재성장 온도에서 냉각되는 과정에서 결함이 생성되지 않는 임계 두께보다 작은 230nm 정도이며, 이와 같이 얇은 III-V 박막에서는 Lateral p-i-n 다이오드 구조를 적용할 수밖에 없다. 한편, 그림 7의 BH(Buried-Heterostructure) DFB 레이저 다이오드 소자 제작을 위한 공정 순서 개념도에서 확인할 수 있듯이, NTT는 이러한 Lateral p-i-n 구조 형성을 위한 p- 및 n-타입 도핑을 위해 일반적으로 기존 레이저 다이오드 소자 제작 시 사용하지 않는 Zn 확산 및 Si 주입 공정을 사용하였다.

그림 7.

Si 광도파로 상부에 멤브레인 BH DFB

출처 T. Aihara et al., “Membrane buried-heterostructure DFB laser with an optically coupled III-V/Si waveguide,” Optics Express, vol. 27, no. 25, 2019, pp. 36438–36448, © 2019 Optical Society of America.[40]

그림 8은 상기 멤브레인 III-V 레이저 다이오드에서 발진하는 광이 평면 테이퍼 구조의 InP 및 Si 광도파로를 거쳐 전체 소자 칩의 양단에 형성된 출력 SiOx 광도파로를 통해 큰 개구수를 갖는 단일모드 광섬유와 결합되는 것을 보여주는 광집적 소자에 대한 평면 개념도이다. 그리고 상기 SiOx 광도파로의 광모드가 하부 Si 기판의 영향을 받지 않도록 하기 위해 NTT는 Si 기판과 Si 광도파로 사이에 존재하는 SiO2 막의 두께를 2μm로 두껍게 하였는데, 이러한 두꺼운 SiO2 막의 큰 열저항은 레이저 다이오드의 고온 동작 특성을 열화시키는 원인으로 작용할 수 있다. 그러나 NTT는 큰 열저항에도 불구하고 35mA의 전류를 주입하여 120℃의 고온에서 동작하는 멤브레인 레이저 다이오드 제작 결과를 보고하였으며, 활성층 단면적이 매우 작기 때문에 25℃의 상온에서 문턱전류가 7.5mA로 작아 결과적으로 소비 전력이 줄어들었기 때문에 120℃의 고온 동작이 가능한 것으로 설명하였다.

그림 8.

큰 개구수를 갖는 단일모드 광섬유와의 광결합을 위한 멤브레인 BH DFB 레이저 다이오드 집적 소자의 평면 개념도

출처 T. Aihara et al., “Membrane buried-heterostructure DFB laser with an optically coupled III-V/Si waveguide,” Optics Express, vol. 27, no. 25, 2019, pp. 36438–36448, © 2019 Optical Society of America.[40]

한편, NTT는 2020년에 2μm 두께의 열산화막이 존재하는 Si 기판 상부에 O-band LAN WDM용 8 채널 멤브레인 레이저 다이오드 소자 어레이를 선택적 영역 성장 기법을 도입하여 제작하고 PAM4 방식으로 직접 변조하여 56Gbit/s 속도로 전송한 결과를 보고하였다[41].

Ⅲ. 결론

실리콘 기판상에 광통신용 레이저 다이오드 소자를 구현하는 다양한 기술 동향에 대하여 살펴보았다. 현재까지는 실리콘 기판상에 III-V 화합물 반도체 박막이나 소자를 접합하는 방식으로 실리콘 반도체 소자와 III-V 화합물 반도체 광소자를 결합한 실리콘 포토닉스 소자 개발이 진행되고 있다. 그러나 아직까지 접합공정이 복잡하고 대량 생산이 어려운 문제가 있어 간결하고 획기적인 접합공정 개발이 시급하다.

앞으로 계속적으로 고속데이터 처리와 에너지 절감뿐만 아니라 초고집적도에 대한 요구가 높아지게 될 것이므로 실리콘 물질의 한계를 극복하기 위한 실리콘 반도체와 III-V 화합물 반도체 이종 반도체 간의 접합에 대한 연구가 더욱더 활발하게 이루어질 것이다.

용어해설

MOCVD 금속 유기 원료를 사용해 기판 위에 박막을 형성시키는 화학증착법

MQW 여러 층의 나노크기의 2차원적 평판 초미세구조로 전자의 움직임이 2차원의 우물에 속박되어 있고, 이때 전자의 파장이 구속포텐셜의 크기와 상응하여 전자의 에너지 준위가 양자화되는 구조

APB 결정 영역 내의 원자가 완벽한 격자 시스템의 원자와 반대 순서로 구성되는 평면 결정학 결함

hybrid silicon laser 실리콘과 III-V족 화합물 반도체 재료로 제조된 반도체 레이저

약어 정리

BCB

Benzocyclobutene

DBR

Distributed Bragg Reflector

DFB

Distributed-Feedback

ECCI

Electron Channeling Contrast Imaging

FPLD

Fabri-Perot Laser Diode

MBE

Molecular Beam Epitaxy

MLL

Mode-Locked Lasers

MOCVD

Metal Organic Chemical Vapor Deposition

MQW

Multi Quantum Well

QDLD

Quantum Dot Laser Diode

WDM

Wavelength Division Multiplexing

V. Joshkin et al., "Biaxial compression in GaAs thin films grown on Si," J. Cryst. Growth, vol. 147, 1995, pp. 13-18.

P.J. Taylor et al., "Optoelectronic device performance on reduced threading dislocation density GaAs/Si," J. Appl. Phys., vol. 89, 2001, pp. 4365-4375.

K. Akahori et al., "Improvement of the MOCVD-grown InGaPon-Si towards high-efficiency solar cell application," Solar Energy Mater. Solar Cells, vol. 60, 2001, pp. 593-598.

W.-Y. Uen et al., "Heteroepitaxial growth of GaAs on Si by MOVPE using a-GaAs/a-Si double buffer layers," J. Cryst. Growth, vol. 295, 2006, pp. 103-107.

K. Ma et al., "Low-temperature growth of GaAs on Si used for ultrafast photoconductive switches," IEEE J. Quantum Electron., vol. 40, 2004, pp. 800-804.

J.W. Lee et al., "Defect reduction by thermal annealing of GaAs layers grown by molecular beam epitaxy on Si substrates," Appl. Phys. Lett., vol. 50, 1987, pp. 31-33.

M. Yamaguchi et al., "Analysis of strained-layer superlattice effects on dislocation density reduction in GaAs on Si substrates," Appl. Phys. Lett., vol. 54, 1989, pp. 24-26.

M. Yamaguchi et al., "Dislocation density reduction in heteroepitaxial III-V compound films on Si substrates for optical devices," J. Mater. Res., vol. 6, 1991 pp. 376-384.

N. Havafuji et al., "Effectiveness of AlGaAs/GaAs superlattices in reducing dislocation density in GaAs on Si," J. Cryst. Growth, vol. 93, 1988, pp. 494-498.

Y. Shi et al., "Optimization of the GaAs-on-Si substrate for microelectromechanical systems(MEMS) sensor application," Materials, vol. 5, pp. 2917-2926.

B.L. Sharma and R.K. Purohit, "Characterization of the Grown Layers," in Semiconductor-heterojunctions, Pergamon Press, Oxford, UK, 1974, pp. 57–76.

L. George et al., "Dislocation filters in GaAs on Si," Semicond. Sci. Techno., vol. 30, no. 11. 2015, 114004.

M. Tang et al., "Optimizations of defect filter layer for 1.3-μm InAs/GaAs quantum-dot lasers monolithically grown on Si substrates," IEEE J. Quantum Electron., vol. 22, 2016, 1900207.

Y.H. Ko et al., "High quality GaAs epitaxially grown on Si (001) substrate through AlAs nucleation and thermal cycle annealing," Solid State Electron., vol. 166, 2020, 107763.

Y.H. Ko, K.J. Kim, and W.S. Han, "Monolithic growth of GaAs laser diodes on Si(001) by optimal AlAs nucleation with thermal cycle annealing," Optical Materials Express, vol. 11, no. 3, 2021, pp. 943-951.

J. Wang et al., "1.3μm InAs/GaAs quantum dot lasers on silicon with GaInP upper cladding layers," Photonics Res., 2018, vol. 6, no. 4, pp. 321-325.

O. Abouzaid et al., "O-band emitting InAs quantum dots grown by MOCVD on a 300 mm Ge-buffered Si (001) substrate," Nanomaterials, 2020, vol. 10, no. 12, pp. 321-325.

J. Yang et al., "All-MBE grown InAs/GaAs quantum dot lasers with thin Ge buffer layer on Si substrates," J. Phys. D: Appl. Phys., vol. 54, no. 3, 2021, 035103.

A.Y. Liu et al., "Electrically pumped continuous-wave 1.3μm quantum-dot lasers epitaxially grown on on-axis (001) GaP/Si," Optics Letters, vol. 42, 2017 pp. 338-341.

D.H. Jung et al., "High efficiency low threshold current 1.3μm InAs quantum dot lasers on on-axis (001) GaP/Si," Appl. Phys. Lett., vol. 111, 2017, 122107.

B. Shi et al., "MOCVD grown low dislocation density GaAs-on-V-groove patterned (001) Si for 1.3μm quantum dot laser applications," Appl. Phys. Lett., vol. 114, 2019, 172102.

B. Shi et al., "Continuous-wave electrically pumped 1550 nm lasers epitaxially grown on on-axis (001) silicon," Optica., vol. 6, 2019, 1507.

S. Znu et al., "1.5 μm quantum-dot diode lasers directly grown on CMOS-standard (001) silicon" Appl. Phys. Lett., vol. 113, 2018, 221103.

S. Zhu et al., "Room-temperature electrically-pumped 1.5μm InGaAs/InAlGaAs laser monolithically grown on on-axis (001) Si" Opt. Express, vol. 26, no. 11, 2018, pp. 14514–14523.

S. Zhu et al., "Parametric study of high-performance 1.55μm InAs quantum dot microdisk lasers on Si" Opt. Express, vol. 25, no. 25, 2017, pp. 31281–31293.

S. Chen et al., "Electrically pumped continuous-wave 1.3μm InAs/GaAs quantum dot lasers monolithically grown on onaxis Si (001) substrates," Opt. Express. vol. 25, 2017, 4632.

H. Park et al., "Hybrid silicon evanescent laser fabricated with a silicon waveguide and III-V offset quantum wells," Opt. Express. vol. 13, 2005, pp. 9460-9464.

B. Bakir et al., "Electrically driven hybrid Si/III-V Fabry-Perot lasers based on adiabatic mode transformers," Opt. Express, vol. 19, 2011, pp. 10317-10325.

A.W. Fang et al., "A distributed bragg reflector silicon evanescent laser," IEEE Photonics Technol. Lett., vol. 20, 2008, pp. 1667-1669.

A.W. Fang et al., "A distributed feedback silicon evanescent laser," Opt. Express, vol. 16, 2008, pp. 4413-4419.

D. Liang et al., "Hybrid silicon evanescent approach to optical interconnects," Appl. Phys. A, vol. 95, 2009, pp. 1045-1057.

A. W. Fang et al., "A racetrack mode-locked silicon evanescent laser," Opt Express. vol. 16, 2008, pp. 1393-1398.

S. Stankovic et al., "1310-nm hybrid III-V/Si Fabry-Perot laser based on adhesive bonding," IEEE Photonics Technol. Lett., vol. 23, 2011, 2169397.

S. Stankovic et al., "Hybrid III-V/Si distributed-feedback laser based on adhesive bonding" IEEE Photonics Technol. Lett., vol. 24, 2012, 2223666.

K. Tanabe et al., "Electrically pumped 1.3 room-temperature InAs/GaAs quantum dot lasers on Si substrates by metal-mediated wafer bonding and layer transfer," Opt. Express, vol. 18, 2010, pp. 10604-10608.

T. Hong et al., "A selective-area metal bonding InGaAsP-Si laser" IEEE Photonics Technol. Lett., vol. 22, 2010, pp. 1141-1143.

K. Matsumoto et al., "Room-temperature operation of GaInAsP lasers epitaxially grown wafer-bonded InP/Si substrate," Phys. Status. Solidi A, vol. 215, no. 8, 2018.

Y. Hu et al., "III/V-on-Si MQW lasers by using a novel photonic integration method of regrowth on a bonding template," Light: Sci. Appl., vol. 8, no. 93, 2019.

S. Matsuo et al., "Directly modulated buried heterostructure DFB laser on SiO2/Si substrate fabricated by regrowth of InP using bonded active layer," Opt. Express, vol. 22, no. 10, 2014.

T. Aihara et al., "Membrane buried-heterostructure DFB laser with an optically coupled III-V/Si waveguide," Opt. Express, vol. 27, no. 25, 2019.

그림 1

DFL 마다 줄어드는 TDD를 나타낸 그래프

출처 I. George et al., “Dislocation filters in GaAs on Si,” Semicond. Sci. Technol. vol. 30, no. 11, 2015, 114004. CC BY 3.0.[12]

그림 2.

Si(001)에서 성장한 양자점 레이저 구조의 개략도

출처 S. Chen et al., “Electrically pumped continuous-wave 1.3μ DWELL 구조를 이용하여 Si 기판상에 1.3μm에서 m InAs/GaAs quantum dot lasers monolithically grown on on-axis Si(001) substrates,” Optics Express, vol. 25, no. 5, 2017, pp. 4632–4639, CC BY 4.0.[26]

그림 3.

(a) 실리콘 GaAs/AlGaAs 레이저 다이오드의 LIV 그래프 (b) 실리콘 GaAs/AlGaAs 레이저 다이오드의 발진 스펙트럼

출처 Y.H. Ko, K.J. Kim, and W.S. Han, “Monolithic growth of GaAs laser diodes on Si(001) by optimal AlAs nucleation with thermal cycle annealing,” Optical Materials Express, vol. 11, no. 3, 2021, pp. 943–951. © 2021 Optical Society of America.[15]

그림 4.

V-grooved (001) Si에서 성장한 3.9 μm InP 버퍼의 단면 STEM 이미지

출처 B. Shi et al., “Continuous-wave electrically pumped 1550 nm lasers epitaxially grown on on-axis (001) silicon,” Optica, vol. 6, no. 12, 2019, pp. 1507–1514. © 2019 Optical Society of America.[22]

그림 5.

실리콘 기판상의 InAs/InAlGaAs/InP 양자점 레이저 개략도 및 구조 (그림은 출처의 논문에서 수정함)

출처 Reproduced from S. Zhu et al., “Room-temperature electrically-pumped 1.5μm InGaAs/InAlGaAs laser monolithically grown on on-axis (001) Si” Opt. Express, vol. 26, no. 11, 2018, pp. 14514–14523[24], S. Zhu et al., “Parametric study of high-performance 1.55μm InAs quantum dot microdisk lasers on Si” Opt. Express, vol. 25, no. 25, 2017, pp. 31281–31293[25] © 2021 Optical Society of America.

그림 7.

Si 광도파로 상부에 멤브레인 BH DFB

출처 T. Aihara et al., “Membrane buried-heterostructure DFB laser with an optically coupled III-V/Si waveguide,” Optics Express, vol. 27, no. 25, 2019, pp. 36438–36448, © 2019 Optical Society of America.[40]

그림 8.

큰 개구수를 갖는 단일모드 광섬유와의 광결합을 위한 멤브레인 BH DFB 레이저 다이오드 집적 소자의 평면 개념도

출처 T. Aihara et al., “Membrane buried-heterostructure DFB laser with an optically coupled III-V/Si waveguide,” Optics Express, vol. 27, no. 25, 2019, pp. 36438–36448, © 2019 Optical Society of America.[40]

표 1 III-V/Si 버퍼 성장 기술

| 기술 | 연구방법 | 효과 |

|---|---|---|

| 2단 성장(two-step growth) | 처음 III-V 성장 단계에서 저온 성장 후 고온 성장[1-5] | 결함 감소 |

| 열처리(thermal cycle annealing) | 300~900℃ 주기적 열처리를 3~5회 반복[6-8] | |

| 결함억제층(dislocation filter layer) | 초격자 구조를 버퍼층에 삽입[9-13] | |

| Si off-cut 기판 이용 | Si off-cut 기판 위 성장[14-16] | APB 억제 |

| Ge 버퍼 이용 | Ge 버퍼를 Si 기판 위 성장[17,18] | |

| GaP/Si 기판 이용 | 얇은 45nm GaP layer를 Si 기판 위 성장[19,20] | |

| V-groove Si 기판 이용 | 나노 스케일의 V-groove를 Si 기판 위에 형성[21-24] |

표 2 웨이퍼 본딩 방식을 이용한 대표적 하이브리드 실리콘 레이저

출처 X. Luo et al., “High-throughput multiple dies-to-wafer bonding technology and III/V-on-Si hybrid lasers for heterogeneous integration of optoelectronic integrated circuites,” Frontiers in Materials, vol. 2, no. 28, 2015, CC BY 4.0.

- Sign Up

- 전자통신동향분석 이메일 전자저널 구독을 원하시는 경우 정확한 이메일 주소를 입력하시기 바랍니다.