양자컴퓨터 제어 기술

Technical Trend and Challenging Issues for Quantum Computing Control System

- 저자

-

정용화양자컴퓨팅연구실 jyh31823@etri.re.kr 최병수양자컴퓨팅연구실 bschoi3@etri.re.kr

- 권호

- 36권 3호 (통권 190)

- 논문구분

- 일반논문

- 페이지

- 87-96

- 발행일자

- 2021.06.01

- DOI

- 10.22648/ETRI.2021.J.360309

본 저작물은 공공누리 제4유형: 출처표시 + 상업적이용금지 + 변경금지 조건에 따라 이용할 수 있습니다.

본 저작물은 공공누리 제4유형: 출처표시 + 상업적이용금지 + 변경금지 조건에 따라 이용할 수 있습니다.- 초록

- Quantum computers will be a game-changer in various fields, such as cryptography and new materials. Quantum computer is quite different from the classical computer by using quantum-mechanical phenomena, such as superposition, entanglement, and interference. The main components of a quantum computer can be divided into quantum-algorithm, quantum-classical control interface, and quantum processor. Universal quantum computing, which can be applied in various industries, is expected to have more than millions of qubits with high enough gate accuracy. Currently, It uses general-purpose electronic equipment, which is placed in a rack, at room temperature to make electronic signals that control qubits. However, implementing a universal quantum computer with a low error rate requires a lot of qubits demands the change of the current control system to be an integrated and miniaturized system that can be operated at low temperatures. In this study, we explore the fundamental units of the control system, describe the problems and alternatives of the current control system, and discuss a future quantum control system.

Share

Ⅰ. 서론

양자컴퓨터의 역사는 1982년, 리처드 파인만이 처음으로 개념을 제시하며 시작되었다[1]. 그 후, 쇼어 알고리즘과 그로버 알고리즘 등으로 양자컴퓨터가 고전 컴퓨터보다 특정 부분에서 계산을 빠르게 할 수 있음이 수학적으로 증명되며 양자컴퓨팅에 대한 기대감을 증폭시켰다[2,3]. 고전 컴퓨터와 비교하여 양자컴퓨터는 ‘중첩’, ‘얽힘’, ‘간섭’ 등 양자역학적 특징을 응용하는 컴퓨터이다. 이를 이용해 연산량 및 연산속도가 크게 증가하여, 양자컴퓨팅 기술은 암호학, 신소재 개발 등에 큰 도움이 될 것으로 기대된다[4]. 이처럼 다양한 분야에서 게임 체인저가 될 가능성이 대두되면서 수많은 기업과 국가에서 양자컴퓨터를 연구·개발하기 시작했다. 2019년, IBM에서는 초전도 방식의 상용 양자컴퓨터를 공개하였으며[5], Google은 53큐비트 규모의 양자컴퓨터를 이용하여 난수 증명 문제에서 고전 컴퓨터보다 양자컴퓨터가 더 빠른 연산을 보일 수 있음을 확인하였다[6]. 이러한 양자컴퓨팅 관련 연구는 각 국가마다 핵심 기술로서 연구개발을 지원하고 있다. 미국은 2018년 양자컴퓨터 부분의 기술우위 및 정책 방안 제시를 위해 5년간 한화 약 1조 4,000억 원을 투자하고 있다[7]. 또한 중국은 2018년부터 5년간 한화 약 16조 5,000억 원을 투자하여 양자 정보 과학 국가 연구소를 설립해, 양자 통신망 구축과 양자컴퓨터 개발에 착수하였다[8]. 이외에도 EU와 일본 등 선진국들 또한 양자컴퓨팅 분야를 포함한 양자 기술 부분에 투자 규모를 늘려나가고 있다[9,10].

다만 양자컴퓨터를 다양한 분야에서 범용적으로 사용할 수 있게 하려면, 양자 오류 정정을 활용하여 수백만 개 이상의 큐비트를 활용할 수 있어야 한다[11]. 이에 따라 양자 알고리즘을 수행할 때, 논리적 연산을 처리하는 부분과 하위 부분 등으로 분리하여 대규모 시스템을 계층화하여 손쉽게 사용할 수 있어야 한다. 하지만 현재 양자컴퓨팅 제어 방식으로는 수백만 큐비트 이상의 확장 가능한 양자컴퓨터를 제어하기가 어렵다. 최근 몇몇 연구기관들은 현재의 큐비트 제어 방법에서 탈피한 새로운 제어 방법을 고안하고 있다.

본 고에서는 큐비트를 제어하는 데 필요한 양자컴퓨팅 제어 기술 동향을 알아보고 기술의 주요 이 슈들과 전망을 살펴본다. Ⅱ장에서는 양자컴퓨팅 구성요소를 서술한다. Ⅲ장에서는 반도체 양자점 양자컴퓨팅 제어구조를 서술한다. Ⅳ장에서는 범용 전자 장비 기반의 신호 생성 및 제어 기술의 문제점을 살펴본다. Ⅴ장에서는 Ⅳ장에서 드러난 문제의 해결책과 산업체 동향을 살펴본다. Ⅵ장에서는 전망 및 내용을 요약하며 본 고를 마무리한다.

Ⅱ. 양자컴퓨팅 구성요소

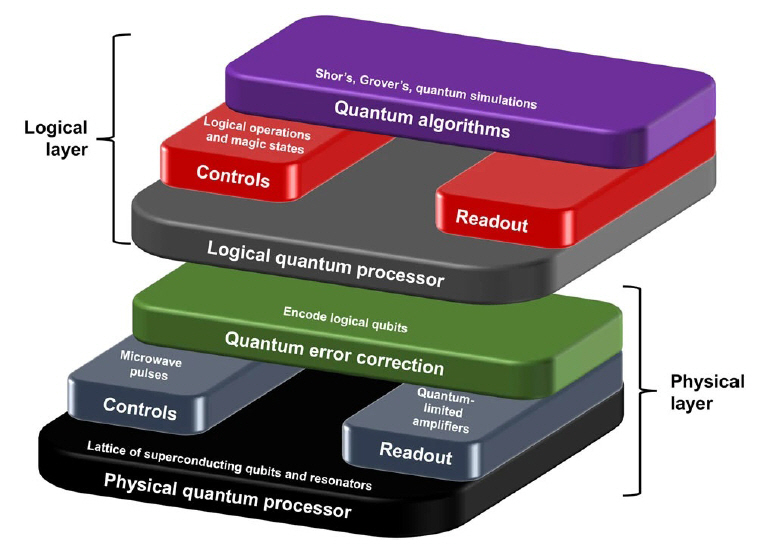

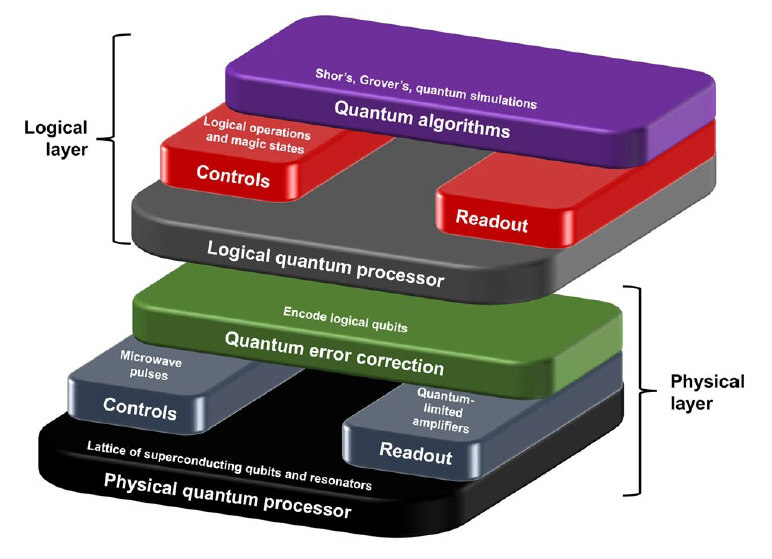

양자컴퓨터의 시스템 구조는 크게 물리적 계층과 논리적 계층으로 나눌 수 있다(그림 1). 물리적 계층은 양자 오류 정정 프로세서를 이용하여 양자역학에 기반한 연산을 수행하는 곳이다. 이러한 연산은 양자오류정정 과정을 거쳐 하나의 단위를 형성하여 논리적 계층과 연결된다. 논리적 계층은 양자 알고리즘에서 요구하는 논리 연산을 수행할 수 있도록 양자 연산을 재조정하거나 물리적인 배치를 고려하여 양자 알고리즘을 효과적으로 수행할 수 있도록 조절한다. 이 중 양자 알고리즘, 양자칩, 그리고 양자 프로세서 제어를 간략히 소개하고자 한다.

그림 1

양자컴퓨팅 구성요소

출처 J.M. Gambetta et al., “Building logical qubits in a superconducting quantum computing system,” NPJ Quantum Inf. vol. 3, no. 2, 2017, CC BY 4.0.

1. 알고리즘

대표적인 양자 알고리즘에는 쇼어 알고리즘[2]과 그로버 알고리즘[3]이 있다. 예컨대, 쇼어 알고리즘은 빠른 소인수 분해를 통해 암호 해독을 가능케 하고, 그로버 알고리즘은 탐색 및 최적화를 빠르게 할 수 있게 한다. 이러한 양자 알고리즘은 양자 정보의 차원이 큐비트의 개수에 따라 기하급수적으로 증가하는 것을 이용하여 고전 알고리즘 대비 매우 빠른 연산 능력을 가능하게 한다.

가. 쇼어 알고리즘

쇼어 알고리즘은 양자 푸리에 변환을 이용하여 현재 범용적으로 쓰이는 암호키인 RSA(Rivest-Shamir-Adleman) 암호를 빠르게 풀 수 있다. 쇼어 알고리즘이 적용된 양자컴퓨터는 고전 컴퓨터가 해독하는 데에 수만 년이 걸리는 2,048비트 RSA 암호를 대략 8시간 만에 해독할 수 있을 것으로 기대한다[12].

가. 그로버 알고리즘

그로버 알고리즘은 찾고자 하는 값의 확률진폭을 증폭시키는 과정을 반복하여 고전 알고리즘 대비 복잡도를 최대

2. 양자 칩

양자 칩에 있는 큐비트를 구현하는 방법의 종류는 매우 다양하다. 반도체 양자점, 초전도 등을 활용하는 방식이 있고, 각각 그에 맞는 제어 방식이 존재한다. Google, IBM, Intel 등 많은 기업이 개발하고 있는 양자컴퓨터의 양자 칩은 100mK 이하의 극저온에서 작동한다. 이처럼 극도로 낮은 저온에 큐비트를 위치시키는 이유는 큐비트가 작은 열에너지에도 매우 민감하게 반응하기 때문이다.

여러 가지 큐비트 구현 방법 중 반도체 양자점 큐비트는 양자점의 크기가 대략 100×100nm2 (1nm는 10억분의 1m)로 매우 작아 다수의 양자점을 집적하는 것이 가능할 것으로 예상되며, 기존의 고도화된 반도체 산업 기술들을 이용할 수 있다는 장점이 있다[13].

3. 제어

전자 제어 장치는 양자컴퓨터를 제어하기 위해 전자기파 형태의 아날로그 신호를 사용하는데, 이러한 전자 제어 장치의 근본적인 성질인 열잡음, 외부 방사원의 간섭, DAC(Digital to Analog Converter) 장치의 변동으로 인해 제어 장치의 성능이 크게 저하될 수 있다. 본 고에서는 반도체 양자점 큐비트의 제어 방식에 국한하여 서술하도록 하겠다.

Ⅲ. 반도체 양자점 양자컴퓨팅 제어구조

이 장에서는 제어구조와 구성요소에 관하여 서술하고 이들이 어떠한 원리로 작동되는지 구체적인 예시를 통해 알아본다.

1. 제어구조

제어는 큐비트 형성, 초기화, 게이트 제어 그리고 측정 등 여러 단계에서 필수적으로 쓰인다. 예를 들어, 반도체 양자점 큐비트에서는 반도체 구조를 이용해 양자점이라는 인공 원자를 구현하여 양자정보처리를 한다. 또한 양자 회로를 구현하기 위해서는 초기 큐비트 상태를 0 상태로 만들 수 있어야 하는데, 이를 초기화라고 한다. 앞서 언급한 양자 회로의 구현을 위해서는 X 게이트, Z 게이트와 같은 단일 큐비트 게이트 이외에 CNOT 게이트와 같은 다중 큐비트 게이트들이 필요하게 된다. 마지막으로 양자 회로의 결괏값을 측정하기 위해 측정 과정이 필요하게 된다.

이러한 일련의 과정에서 제어는 DCS(DC Source), AWG(Arbitrary Waveform Generator), 그리고 MWS(Microwave Source) 등을 조합하여 큐비트 형성, 게이트 제어, 초기화 및 측정 등을 수행한다.

2. 주요 구성요소

가. 큐비트 형성

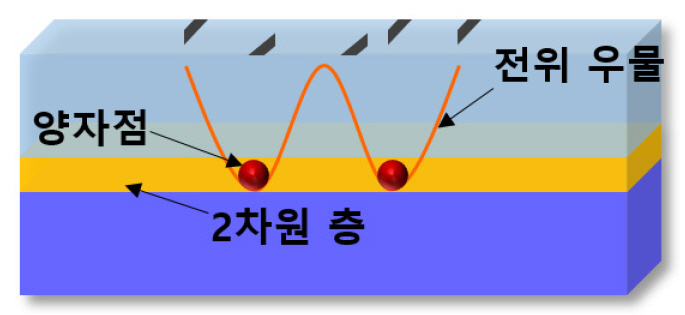

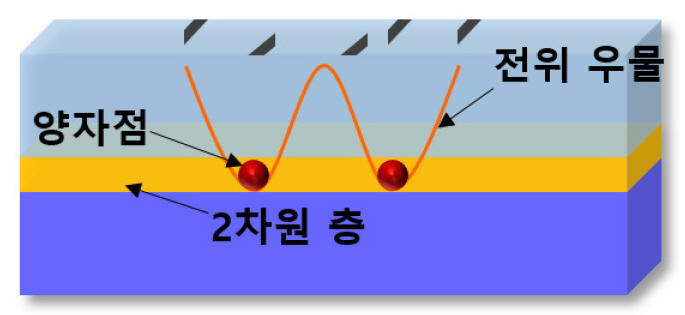

반도체 양자점 양자컴퓨팅에서 양자점 큐비트를 만드는 데에는 DCS 제어장비가 필요하다. 서로 다른 반도체 물질인 AlGaAs와 GaAs를 접합시키면 두 물질의 경계면에 2차원 층이 생긴다. 전자들은 이때의 2차원 층에서 자유롭게 움직일 수 있다. 여기서 정전압을 반도체 표면에 가하게 되면 전위 우물이 만들어진다. 전위 우물들로부터 갇힌 전자들은 양자점을 형성하여 인공 원자와 같이 양자화된 상태를 가지게 되어 양자정보처리가 가능하다. 즉, 반도체 양자점 양자컴퓨팅에서 DCS는 이러한 양자점을 형성하기 위한 전위 우물을 만드는 데 이용된다(그림 2).

나. 게이트 제어

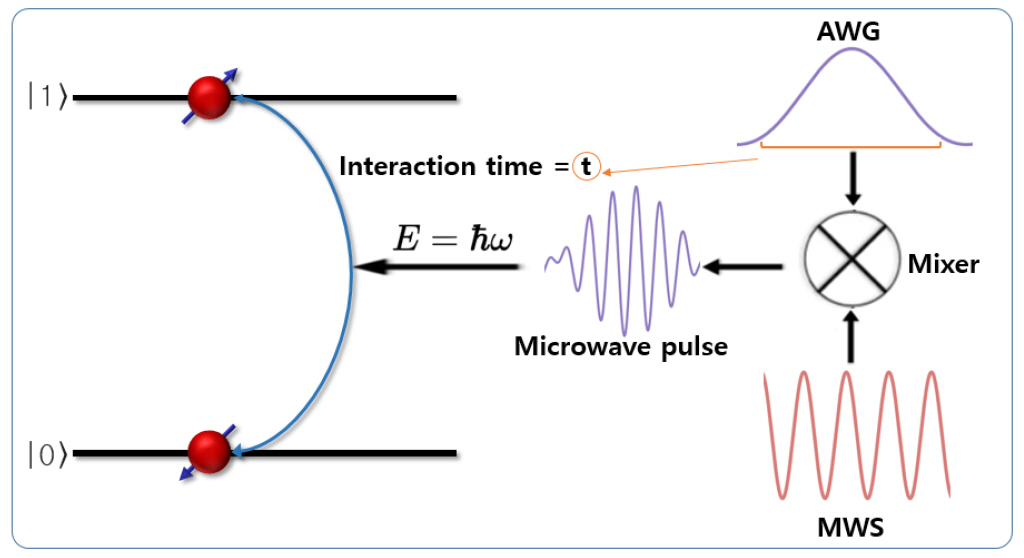

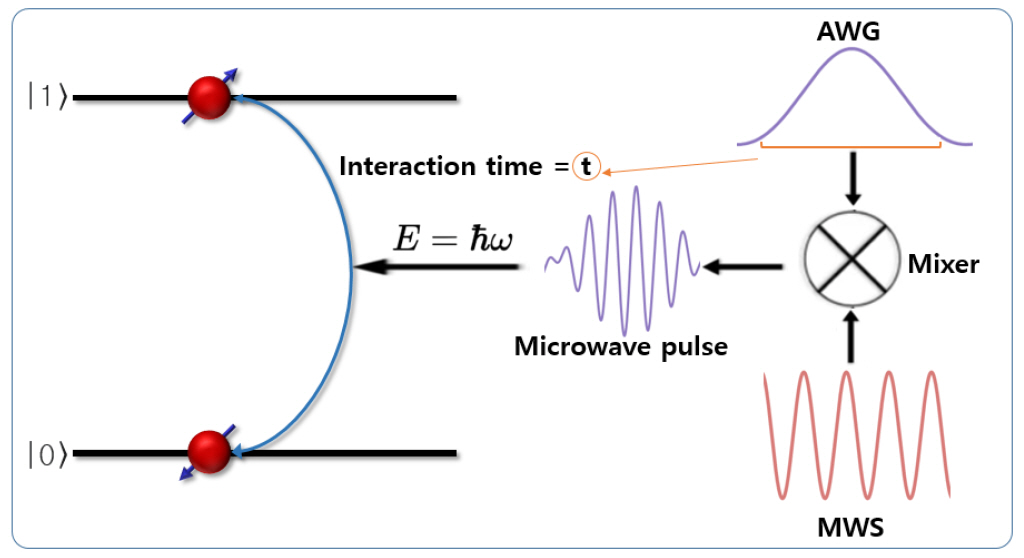

단일 큐비트 게이트 및 다중 큐비트 게이트용 제어 신호를 생성하기 위해서는 AWG와 MWS, 그리고 그 두 파형을 합치는 역할을 하는 믹서 등이 필요하다.

큐비트는 제어 신호의 주파수, 모양, 지속시간에 따라 특정한 상태로 바뀌게 된다. X 게이트로 예를 들어보자. X 게이트는 논리 회로의 NOT 게이트 역할과 동일하여 0은 1로, 1은 0으로 바꿔주는 역할을 한다. X 게이트를 구현하기 위해서는 MWS가 두 상태의 에너지 차이인 E = hω만큼의 에너지를 가해야 한다. 그러므로 이때 가해지는 MWS의 마이크로파 주파수는 두 상태의 에너지 차이에 따라 정해진다. 상호작용하는 시간 또한 중요한데, X 게이트와 같은 단일 큐비트 게이트는 대략 10ns~1μs의 상호작용 시간을 가지게 된다. 이러한 시간을 조정해 주는 역할을 AWG가 한다(그림 3).

이러한 파형의 주파수와 상호작용 시간 등 여러 요구 조건은 큐비트, 시스템, 게이트의 종류에 따라 상이하다[14].

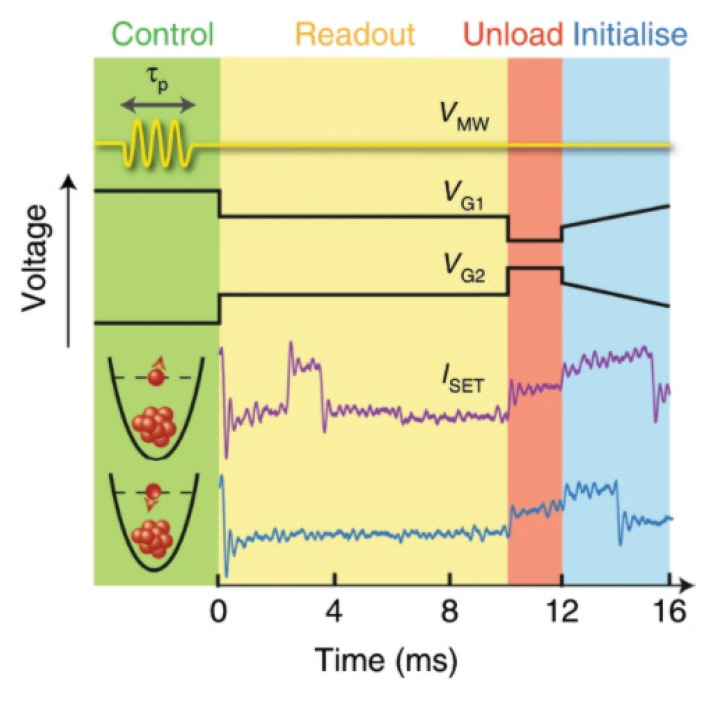

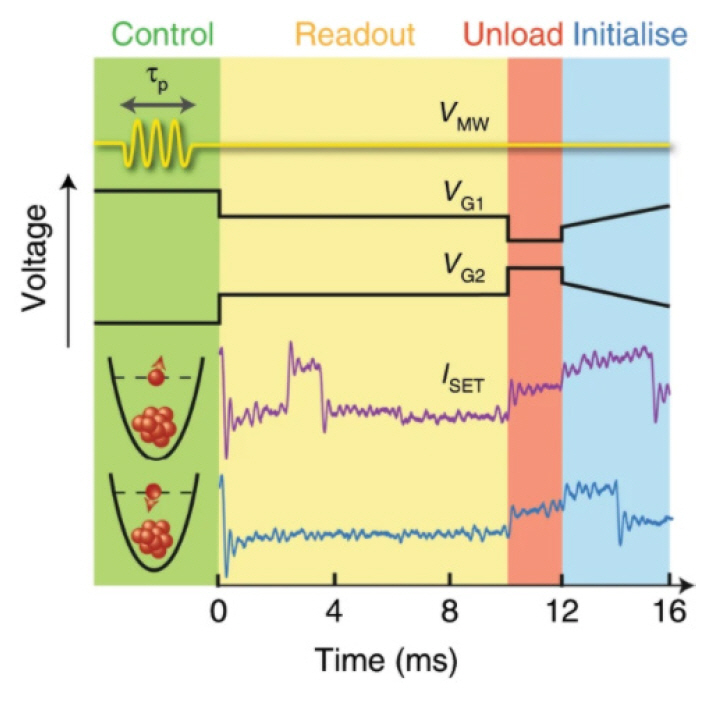

다. 측정 및 초기화

큐비트의 상태는 DCS를 이용하여 큐비트 근처에 측정되는 전류의 파형으로 확인한다. 측정 이후, 큐비트는 측정값과 관계없이 무조건 0으로 바뀌게 된다. 이러한 특성 이용하여 큐비트의 측정값을 역산할 수 있다. 가령 측정값이 1이면 큐비트가 0으로 변하면서 DC가 가해지는 회로의 저항을 순간적으로 변화시켜, 회로에 흐르는 전류가 펄스 형태로 흔들리게 된다. 하지만 측정값이 0이면 큐비트가 0으로 그대로 있으므로 회로의 저항 변화가 발생하지 않는다. 그러므로 측정값이 0이면 회로에 흐르는 전류는 일정하게 유지된다. 이를 이용해 회로에 흐르는 전류가 일정하게 유지되면 측정값이 0, 펄스 형태로 흔들리게 되면 측정값이 1임을 알 수 있다. 예를 들어, 그림 4에서 보이는 보라색 파형처럼 약 2~4ms 부근에서 펄스가 발생하는 것을 측정하면 1로, 하늘색 파형처럼 펄스가 발생하지 않는 것을 측정하면 0으로 측정됐다고 간주한다.

그림 4

반도체 양자점 큐비트 제어 및 초기화 방법

출처 R.C.C. Leon et al., “Coherent spin control of s-, p-, d-, and f-electrons in a silicon quantum dot,” Nat. Commun., vol. 11, no. 797, 2020, CC BY 4.0.

초기화는 측정과 메커니즘과 같다. 큐비트 측정 후 모든 큐비트는 0으로 바뀌게 된다. 이를 이용하여 양자 회로를 구현하기 위해서 초기 큐비트 상태를 0 상태로 만든다.

Ⅳ. 범용 전자 장비 기반의 전자 신호 생성 및 제어 기술의 문제점

Ⅲ장에서 DCS, MWS, AWG 등 범용적인 신호 생성 장비를 활용하여 큐비트 형성, 측정 및 초기화와 게이트 제어를 수행하는 방법에 대하여 살펴보았다. 이 장에서는 현재의 상온 양자 제어 방식을 살펴보고 이러한 방식에서 나타날 향후 문제점이 무엇인지 알아보겠다.

1. 범용 전자 장비 기반의 전자 신호 생성 및 제어 방식

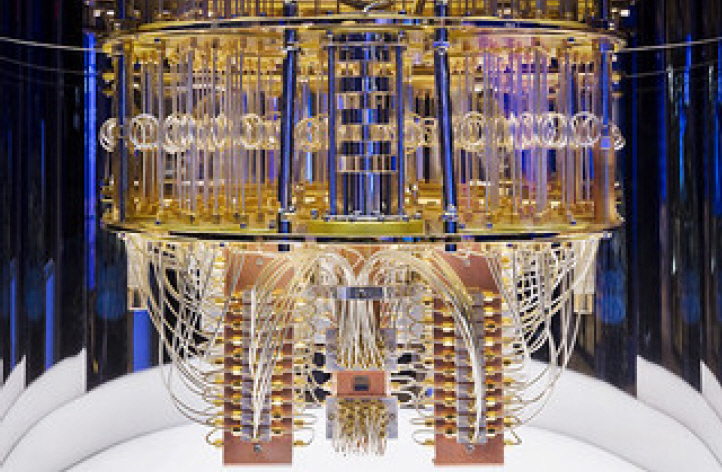

현재 대부분의 양자컴퓨터를 제어하기 위해 DAC, MWS 등 범용 실험 장비로 쓰이는 장비들이 냉각기 외부(상온)에서 신호를 생성하여 직접적으로 냉각기 내부(약 100mK 이하)에 있는 양자 칩과 케이블로 연결하여 양자 연산을 수행하고 있다. 이러한 방식은 IBM 양자컴퓨터에서 볼 수 있듯이 많은 수의 케이블과 복잡성이 요구된다(그림 5).

그림 5

양자컴퓨터의 실제 모습

출처 IBM Research, https://www.flickr.com/photos/ibm_research_zurich/50252942522/in/album-72157663611181258/, CC BY-ND 2.0.

반도체 양자점 양자컴퓨터의 경우에는 전위 장벽을 만들기 위해 큐비트마다 대략 2~3개의 DC 케이블이 필요하다. 또한 큐비트마다 적어도 하나의 대역폭 채널이 필요하다[14]. 하나의 큐비트마다 여러 개의 케이블이 필요한 것은 초전도 양자컴퓨터에서도 해당한다.

하나의 예로, Google의 양자컴퓨터 구조[6]를 살펴보면 하나의 큐비트마다 1개의 XY 채널과 3개의 Z 채널, 그리고 약 10큐비트마다 하나의 측정 채널이 필요하다. 그로 인해 54큐비트 규모의 Google의 양자컴퓨터는 약 200개의 동축 케이블로 수십 개의 전자 장비들과 하나의 양자 칩 사이를 연결하고 있다. 즉 현재의 양자컴퓨터의 모습은 트랜지스터가 발명되기 전, 수많은 장비와 복잡한 선들에 둘러싸인 고전 컴퓨터와 비슷하게 보인다.

2. 문제점

가. 물리적 규모

양자 알고리즘을 이용하여 의미 있는 결과를 얻기 위해서는 수백만 큐비트를 이용하여 결함이 매우 적은 양자컴퓨팅을 수행하는 것이 필요하다[11]. 하나의 큐비트당 대략 4~5개의 케이블이 필요한 현재 제어 방식으로 대규모 양자컴퓨터를 제어하려면 케이블의 규모가 커져, 냉각기 내부 공간의 한계를 뛰어넘을 것이다. 또한 복잡도가 높아져 양자컴퓨터 유지보수와 시스템화에 어려움을 겪을 것이다.

나. 성능

아주 낮은 오류율과 민감도를 가지는 비트와 달리 큐비트는 작은 노이즈 신호에도 크게 반응하며 오류율이 매우 높다. 즉, 양자 제어 신호는 낮은 잡음을 가지는 고품질의 신호가 필요하다. 하지만 현재 제어 방식으로는 케이블에서의 불가피한 손실과 열잡음 등이 발생하여 대규모 양자컴퓨터로 확장하게 되면 양자 회로의 오류율이 높아질 위험이 있다.

다. 속도

범용 전자 장비 기반의 전자 신호 제어 방식으로 신호 생성 후 신호를 전송한 다음 그 신호를 추론하고 트리거링을 하는 데는 500~1,000ns 정도 걸린다. 이러한 시간으로 인해 양자컴퓨터의 클록 속도가 제한된다[15]. 클록 속도가 길면 양자 오류 정정을 수행하게 될 때 빠른 오류 측정과 오류 정정이 요구되므로 이는 큰 어려움을 초래할 수 있다.

Ⅴ. 극저온 양자 제어 칩 기술 동향

Ⅳ장에서 언급한 기술적 난제들을 해결하기 위해 많은 연구진은 극저온 양자 제어 칩이라는 기술을 주목하고 있다.

이 장에서는 극저온 양자 제어 칩 기술이 무엇이고 기존의 방식 대비 어떠한 장점이 있는지 서술한다. 또한 현재 산업계에서 어느 수준까지 구현했고 공통점으로 해결해야 할 이슈가 무엇인지 살펴보도록 하겠다.

1. 극저온 양자 제어 칩 기술

가. 극저온 양자 제어 칩 제약 조건

양자 칩(반도체 양자점 혹은 초전도체 방식)을 상온에서 작동시키게 하는 것은 이론적으로 거의 불 가능하기에 제어 장비를 소형화하여 냉각기에 넣는 방법으로 접근 중이다. 여기서 극저온 양자 제어 칩 기술에는 크게 두 가지 제약 조건이 있다. 첫 번째로 극저온 장치 내에서 극저온을 유지하기 위해 극저온 제어 칩에는 냉각 전력보다 낮은 발열만이 허용된다는 것이고(표 1)[16], 두 번째는 제어 칩이 극저온에서도 정상적으로 동작할 수 있어야 한다는 것이다.

나. 극저온 양자 제어 칩 장점

CMOS와 MOSFET과 같은 반도체 구조는 약 4K에 가까운 극저온에서도 동작할 수 있다[17,18]. 이를 이용해 극저온에서 동작하는 반도체 구조를 이용한 ASIC(Application-Specific Integrated Circuit) 기반의 제어 방식을 적용하게 되면 기존의 제어 방식(범용 전자 장비 기반)에서보다 더 좋은 특성을 가질 수 있다. 기본적으로 ASIC는 특정 기능에 최적화되어 소형화, 고효율, 저전력으로 작동할 수 있다. 그러므로 범용 전자 장비들을 ASIC로 만들어, 소형화한다면 물리적인 크기와 복잡성을 획기적으로 줄일 수 있다.

또한 냉각기 내부와 같은 극저온에서 ASIC가 동작하게 되면 좋아지는 특성들이 존재한다. 극저온에서 트랜지스터의 트랜스컨덕턴스 및 이득은 증가한다[19,20]. 또한 저항과 게이트 지연이 감소하며 문턱전압이하 스윙(Subthreshold Swing)이 낮아져 전력 손실이 낮아진다[21]. 그러므로 극저온에서의 ASIC는 전력 손실로 인한 발열이 적게 생기므로 제어 칩이 냉각기 내부에 들어가더라도 냉각기는 극저온 상태를 유지할 수 있다.

2. 산업체 동향

가. Google

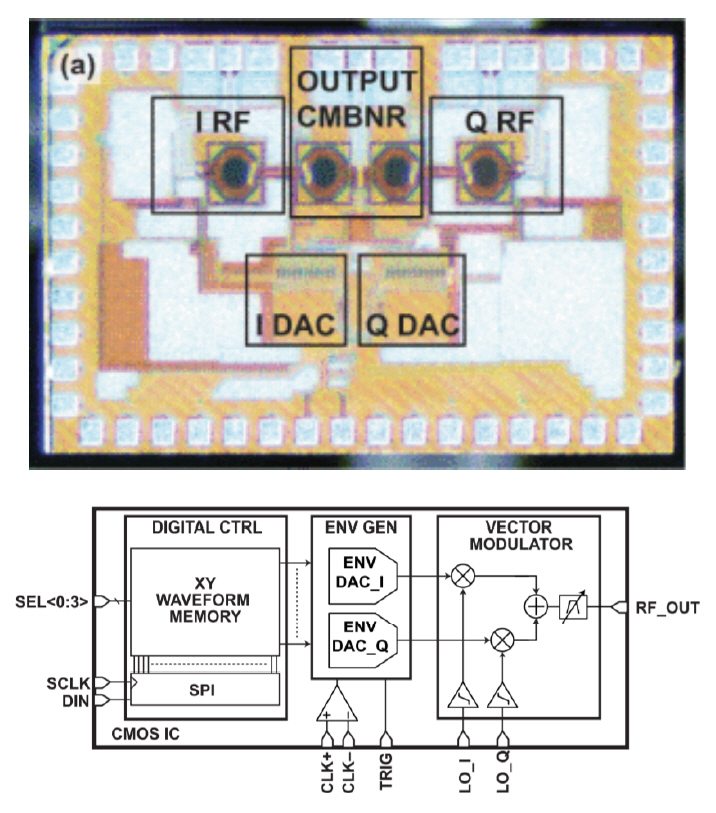

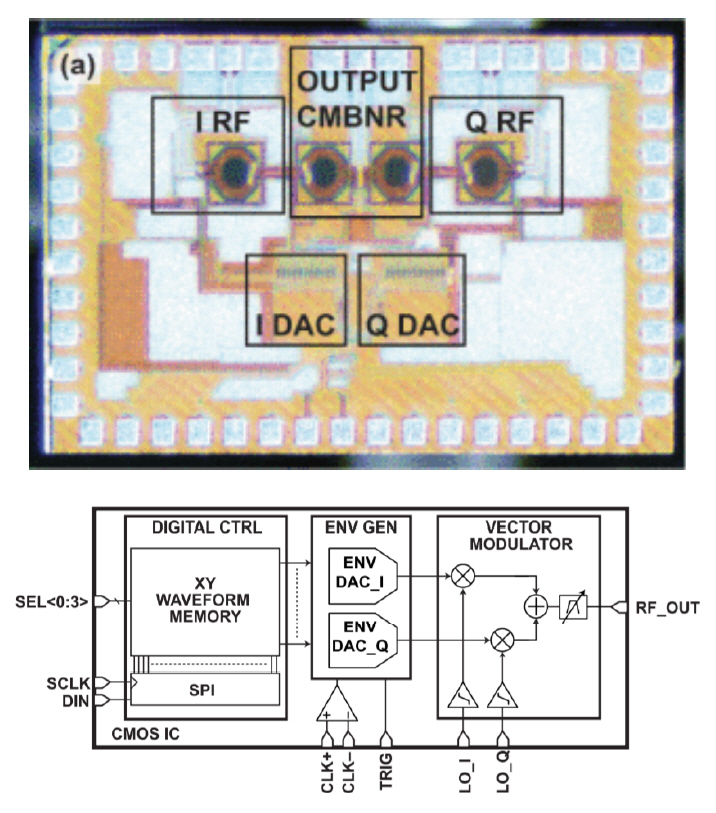

2019년 매사추세츠 대학교 조제프 바르딘 교수와 Google의 공동 연구진은 3K에서 동작하는 신호 생성기를 ASIC로 구현했다(그림 6)[22]. 이 ASIC는 단일 큐비트 게이트인 X 게이트, Z 게이트 등을 수행하기 위한 펄스를 생성할 수 있다. 기존 제어 방식은 1W 이상의 전력을 소비하지만, 이 ASIC는 2mW 이하의 전력만을 소비한다. 고안한 ASIC는 기존 제어 방식과 비교했을 때, 결맞음 시간이 크게 달라지지 않았으며 펄스의 진폭을 변화시켜 가시성 높은 라비 진동을 구현할 수 있었다. 실험에서 3개 게이트를 연산했을 때의 오류율이 기존의 제어 방식 대비 약 4.7배 증가한 11.7%로 높아지는 것을 관측했다. 연구진은 대략 12%의 오류율은 향후 IC칩에 맞는 보정 알고리즘(Calibration Algorithm) 개발이 되면 충분히 낮출 수 있다고 주장한다.

그림 6

Google 극저온 제어 칩의 실물과 회로도

출처 J.C. Bardin et al., “Design and Characterization of a 28-nm Bulk-CMOS cryogenic quantum controller dissipating less Than 2 mW at 3 K,” IEEE J. Solid-State Circuits, vol. 54, no. 11, 2019, pp. 3043–3060, CC BY 4.0.

나. Intel

Intel과 QuTech의 공동 연구진은 2020년 극저온 양자 제어 칩인 ‘Horse Ridge’를 공개하였다[23]. Horse Ridge는 Google의 ASIC의 데이터 대역폭이 400MHz임에 반해 1GHz를 보장하여 Google의 극저온 ASIC[22]와 비교하여 더 많은 데이터 전송이 가능하다. 또한 Horse Ridge는 4개의 무선 주파수 채널과 FDMA(Frequency Division Multiple Access) 방식을 통해 하나의 칩으로 128개의 큐비트를 제어할 수 있다. 큐비트의 규모가 커지면 양자 시스템에 부하가 생기면서 큐비트의 성능이나 정확성이 떨어지는 문제가 생긴다. 예를 들어, 여러 주파수로 많은 수의 큐비트를 제어할 때 큐비트 간 간섭을 유발하는 위상 변이가 있다. 위상 변이를 방지하기 위해 공동 연구진은 FDMA 기술을 최적화했다. 이를 바탕으로 Intel은 하나의 Horse Ridge로 안정적으로 128개의 큐비트 제어를 한다고 주장한다.

다. Microsoft

2021년, 시드니 대학교 데이비드 라일리 교수의 연구팀과 Microsoft의 공동 연구진은 제어 칩을 크게 두 부분으로 나눴다. 한 부분은 2K에서 트리거링 조작 및 데이터 처리를 하는 범용 컴퓨팅 코어를, 나머지 부분은 양자 칩이 위치 할 수 있는 100mK 정도에서 I/O 관리와 루팅의 역할을 하는 ‘Gooseberry’라는 이름의 제어 칩을 위치시켰다[24]. 연구진이 고안한 제어 칩 내부에 있는 셀(Cell)은 극저온에서의 트랜지스터의 낮은 누설 전류를 이용하여 플로팅 커패시터 사이의 전하를 저장하고 섞어서 큐비트를 조작하기 위한 DC 신호를 생성할 수 있다. 이러한 방법은 여러 전자 장비마다 최소 하나 이상의 케이블이 필요한 이전의 제어 방식과 달리 케이블의 수를 줄일 수 있어 케이블의 복잡도를 낮출 수 있으며 발열을 크게 낮춘다. 또한 그들은 양자 칩으로의 열전도를 줄이기 위해 제어 장치와 냉각기 사이를 도금된 구리선으로 연결했다. 구리선은 제어 장치에서 발생한 열을 우회시켜 양자 칩으로의 직접적인 열전도를 감소시키는 역할을 한다. 즉 연구진은 양자 칩으로의 열전도를 극단적으로 낮춰, I/O와 같은 일부 구성 요소들과 양자 칩을 하나로 통합할 수 있도록 환경을 조성했다.

3. 향후 연구개발 이슈

앞 절에서 언급한 것처럼 현재 연구는 신호를 생성, 전송하기 위한 믹서, I/O 등 일부 구성요소를 따로 칩으로 제작하여 극저온에서 동작시키는 연구에 진행 중이다. 또한 대부분 테스트는 수십 큐비트에 달하는 최신 양자 칩이 아닌 몇 큐비트 또는 단일 큐비트에서의 동작을 모델링하는 장치에서 제한적으로 수행되고 있다. 이처럼 극저온 양자 제어 칩 모듈화 기술은 이제 갓 태동기에 들어섰다고 볼 수 있으며, 아직 넘어야 할 산들이 많다.

이를테면 온도에 따른 반도체 소자의 특성에서 예상치 못한 난관이 생긴다. 예를 들어, 극저온에서의 반도체 소자는 높은 임계 전압, 더 낮은 출력 저항 등 여러 원치 않는 저하에 직면한다. 또한 반도체 소자의 자체 발열, 푸아송 노이즈 및 플리커 노이즈는 제어 신호의 동기화와 큐비트 측정에서의 오류를 악화시킨다. 따라서 앞서 언급한 문제들을 해결하려면 현재보다 보완된 IC 구조 설계와 전략이 필요하다[25].

Ⅵ. 전망 및 결론

본 고에서는 큐비트를 제어하는 데 필요한 양자컴퓨팅 제어 기술 동향을 알아보고 향후 진행해야 하는 주요 이슈들을 살펴보았다. 장기적으로 양자컴퓨터 개발에서 중요한 것은 대규모의 큐비트를 제어하는 시스템을 개발하는 것이다. 여러 연구를 통해 대규모의 큐비트를 제어하려면 궁극적으로는 현재 방식과 확연히 다른 제어 방식이 필요하다는 것을 보았다. 본 고에서는 양자 칩과 같거나 비슷한 온도에서 동작하는 제어 칩을 설계하여 전자 장비와 케이블의 규모를 줄이고자 한다고 서술했다. 이미 Google, Intel, Microsoft 등 수많은 세계적 기업들은 극저온 양자 제어 칩 개발에 많은 연구개발을 하고 있다. 대규모 양자컴퓨터의 상용화는 암호학과 신소재 개발 등 다양한 분야에서 엄청난 파급력을 가질 것이 분명하다. 양자컴퓨팅 분야에서 극저온 양자 제어 칩 연구는 아직 태동기에 불과하다. 다르게 말하면 우리나라가 극저온 양자 제어 칩 기술에 대한 연구개발에 투자하는 것이 아직 늦지 않았다는 것이다. 이에 우리나라가 극저온 양자 제어 칩 분야의 연구개발에 집중해 미래 양자컴퓨팅 개발의 핵심 기술 보유국 중 하나로 손꼽히기를 기대한다.

용어해설

큐비트 0과 1만을 표현할 수 있는 Bit와 달리 양자역학적 현상을 이용해, 0과 1이 동시에 존재하는 상태로 표현 가능함

ASIC 주문형 반도체로써 고객이나 소비자가 요구하는 특정한 기능만을 수행하도록 설계된 집적회로임

FDMA 사용 가능한 대역을 중첩하지 않도록 여러 대역으로 나눈 후, 분할된 대역을 각각의 채널에 할당하는 방식임

약어 정리

R.P. Feynman, "Simulating physics with computers," Int. J. Theor. Phys., vol. 21, no. 6-7, June 1982, pp. 467–488.

P.W. Shor, "Algorithms for quantum computation: Discrete logarithms and factoring," in Proc. Annu. Symp. Found. Comput. Sci., Santa Fe, NM, USA, Nov. 1994, pp. 124-134.

L.K. Grover, "A fast quantum mechanical algorithm for database search," in Proc. Annu. ACM Symp. Theory Comput., Philadelphia, PA, USA, May 22-24 1996, pp. 212-219.

K.M. Svore et al., "The quantum future of computation," Comput., vol. 49, no. 9, Sept. 2016, pp. 21-30.

F. Arute et al., "Quantum supremacy using a programmable superconducting processor," Nature, vol. 574, 2019, pp. 505–510.

EU Digital Single Market, "EU funded projects on quantum technology," https://ec.europa.eu/

A.G. Fowler et al., "Surface codes: Towards practical large-scale quantum computation," Phys. Rev. A, vol. 86, 2012, Article no. 032324.

C. Gidney and M. Eker, "How to factor 2048 bit RSA integers in 8 hours using 20 million noisy qubits," 2019, arXiv: 1905.09749.

J.C. Bardin et al., "Microwaves in quantum computing," IEEE J. Microw., vol. 1, no. 1, 2021, pp. 403-427.

National Academies of Sciences, Engineering, and Medicine, Quantum Computing: Progress and Prospects, The National Academies Press, Washington, DC, USA, 2018.

G. Batey et al., "A new ultra-low-temperature cryogen-free experimental platform," J. Phys.: Conf. Ser. vol. 568, 2014, Article no. 032014.

A. Beckers, F. Jazaeri, and C. Enz, "Characterization and modeling of 28-nm bulk CMOS technology down to 4.2 K," IEEE J. Electron Devices Soc., vol. 6, 2018, pp. 1007-1018.

A.H. Coskun and J.C. Bardin, "Cryogenic small-signal and noise performance of 32nm SOI CMOS," IEEE MTT-S Int. Microw. Symp. Dig., June. 2014, pp. 1–4.

S. Weinreb, J.C. Bardin, and H. Mani, "Design of cryogenic sige low noise amplifiers," IEEE Trans. Microw. Theory Tech., vol. 55, no. 11, Nov. 2007, pp. 2306-2312.

J.D. Cressler, "Silicon-germanium as an enabling technology for extreme environment electronics," IEEE Trans. Device Mater. Reliab., vol. 10, no. 4, Dec. 2010, pp. 437-448.

R.M. Incandela et al., "Characterization and compact modeling of nanometer CMOS transistors at deep-cryogenic temperatures," IEEE J. Electron Devices Soc., vol. 6, 2018, pp. 996-1006.

J.C. Bardin et al., "29.1 A 28nm bulk-CMOS 4-to-8GHz ¡2mW cryogenic pulse modulator for scalable quantum computing," in Proc. IEEE Int. Solid- State Circuits Conf. (ISSCC), San Francisco, CA, USA, Feb. 2019, pp. 456-458.

B. Patra et al., "19.1 A scalable cryo-CMOS 2-to-20GHz digitally intensive controller for 4×32 frequency multiplexed spin qubits/transmons in 22nm FinFET technology for quantum computers," in Proc. IEEE Int. Solid- State Circuits Conf. (ISSCC), San Francisco, CA, USA, Feb. 2020, pp. 304-306.

S.J. Pauka et al., "A cryogenic CMOS chip for generating control signals for multiple qubits." Nat. Electron., vol. 4, 2021, pp. 64–70.

그림 1

양자컴퓨팅 구성요소

출처 J.M. Gambetta et al., “Building logical qubits in a superconducting quantum computing system,” NPJ Quantum Inf. vol. 3, no. 2, 2017, CC BY 4.0.

그림 4

반도체 양자점 큐비트 제어 및 초기화 방법

출처 R.C.C. Leon et al., “Coherent spin control of s-, p-, d-, and f-electrons in a silicon quantum dot,” Nat. Commun., vol. 11, no. 797, 2020, CC BY 4.0.

그림 5

양자컴퓨터의 실제 모습

출처 IBM Research, https://www.flickr.com/photos/ibm_research_zurich/50252942522/in/album-72157663611181258/, CC BY-ND 2.0.

- Sign Up

- 전자통신동향분석 이메일 전자저널 구독을 원하시는 경우 정확한 이메일 주소를 입력하시기 바랍니다.