정성근 (Jeong S.K.)

황인록 (Hwang I.)

양용석 (Yang Y.S.)

이명래 (Lee M.L.)

서동우 (Suh D.)

Ⅰ. 서론

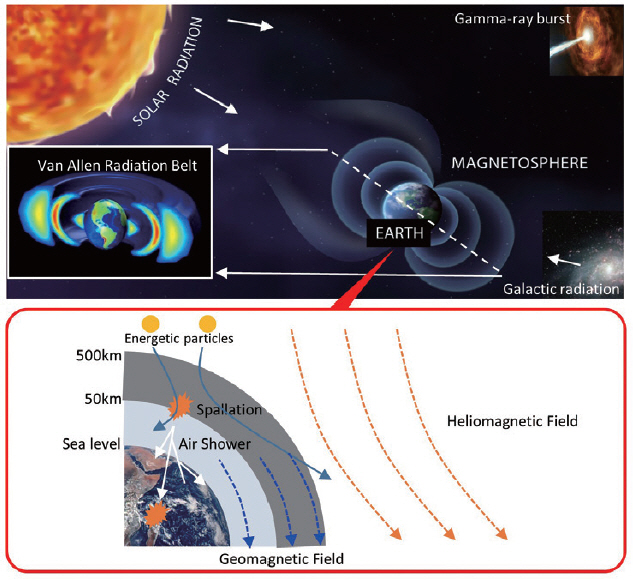

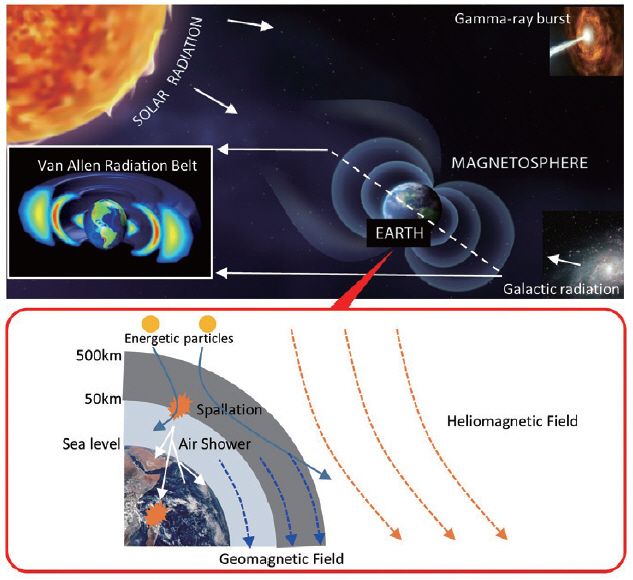

지금까지 우주로 간 전장품의 오작동 원인 중 약 30%가 우주방사선의 영향으로 알려져 있다. 우주 환경에서의 방사선은 심우주로부터의 고에너지 우주입자(Galactic Cosmic Ray), 태양으로부터의 고에너지 우주입자(Solar Cosmic Ray), 지구 자계에 포획된 고에너지 입자 띠(Van Allen Radiation Belts) 등으로 분류되며, 약 85% 양성자들이 주를 이루고 있다. 또한, 이러한 우주방사선이 지구 초기 대기권에 충돌해 2차 우주방사선을 만들며 또다시 다른 대기권 기체와 충돌을 일으켜 중성자, 알파, 베타, 감마 등 연쇄적으로 2차 방사선을 발생시킨다(그림 1). 이들 우주방사선의 에너지 입자들은 랜덤하게 전장품과 충돌하여 오작동에 영향을 끼치며 ICT(Information Communication Technology) 부품이 고집적화될수록 고준위 우주방사선 노출 영향에 대한 우려도 커지고 있다. 고신뢰성을 요구하는 우주, 항공, 원자력, 의료 분야에서 내방사화 기술의 부재는 우주탐사의 임무 실패뿐만 아니라 사회 기반 시설의 오작동으로 이어져 막대한 물적·인적 손실을 초래할 수 있다. 따라서 ICT 소자의 우주방사선 환경의 영향을 검토하며 개발 동향을 고찰한다.

Ⅱ. 우주방사선의 영향

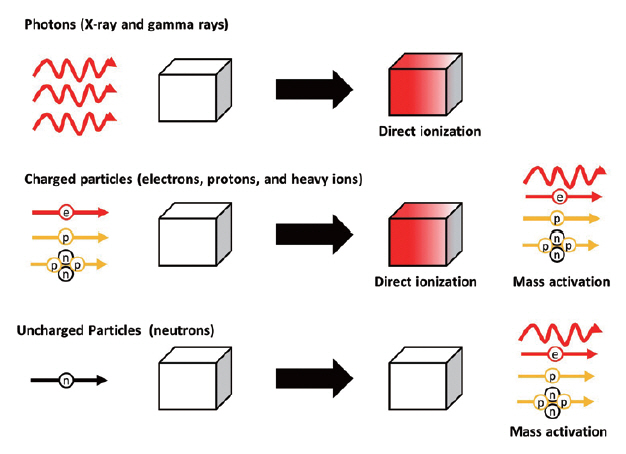

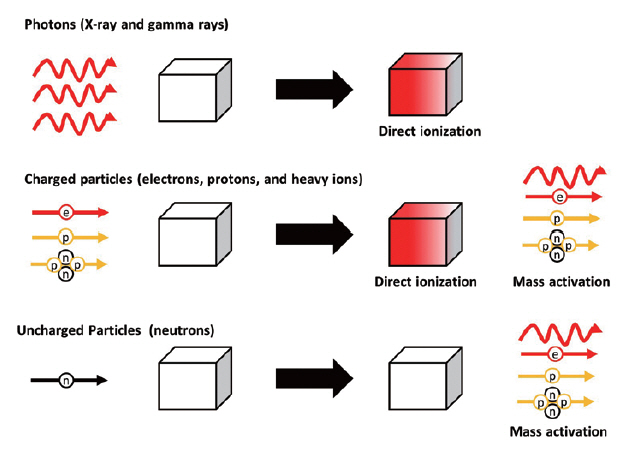

태양 플레어, 초신성, 감마선 폭발 등 다양한 천문 사건을 통해 가속되어 방출되는 방사선은 높은 운동에너지를 가지며(~수백 MeV), 원자의 궤도전자 또는 원자핵과 충돌하여 상호작용하게 된다. 물질과 방사선원별 충돌 시 상호작용은 그림 2에 나타내었다.

높은 에너지 준위를 갖는 감마선 전자파는 물질과 상호작용하여 흡수되는 경우 대부분 매질을 전리시킨다. 하전 입자 역시 물질을 전리시키며 2차 방사선을 발생한다. 중성자선은 직접적으로 물질을 이온화시키지 않지만, 원자와 충돌하여 2차 방사선을 발생한다. 이러한 방사선 상호작용은 발생빈도가 비교적 높은 우주, 고고도 지구 대기 환경에서 전자부품에 치명적인 문제를 야기할 수 있다.

1. 단위소자 방사선 영향(TID, SEE etc.)

방사선이 단위 소자에 충돌하여 발생하는 손상 메커니즘은 방사선의 종류와 에너지에 따라서 매질이 전리되어 발생하는 이온화 영향(Ionizing Effects)과 원자와 충돌하여 발생하는 격자 변위(Lattice Displacement) 두 가지로 크게 나뉜다. 이러한 기작으로 인해 전장부품은 다양한 오작동 현상들이 발생하게 된다. 표 1에서는 대표적인 반도체 손상 유형을 정리하였다.

표 1 방사선으로 인한 대표적 전장품 오작동

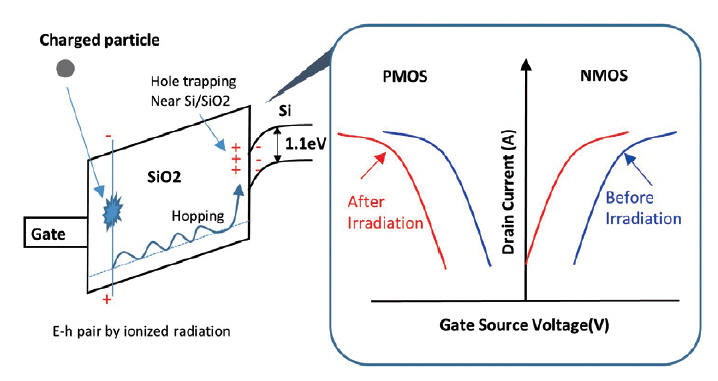

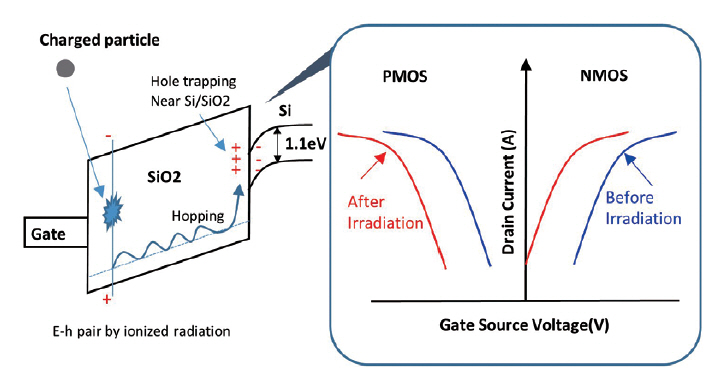

표 1의 오작동들 중 전자장비를 지속적으로 손상시키는 TID(Total Ionizing Dose; 총이온화 선량) 효과는 방사선에 노출된 시간 동안 반도체 소자의 손상이 누적되는 현상으로, 지속적으로 반도체 소자의 성능을 서서히 저하시킨다. 그림 3과 같이 CMOS 소자 게이트 절연층에 방사선이 충돌하게 되면 전자 쌍들이 생성되고 계면과 절연층에 정공 트랩이 생겨 트랜지스터의 문턱 전압이 조금씩 변하게 된다. 이러한 영향은 누적되어 트랜지스터의 기능장애를 발생시키며 영구적으로 소자가 손상되는 결과를 가져온다[1]. 지속적으로 방사선 환경에 노출되는 우주 공간이나 원자력 발전소에서 이러한 문제가 발생하게 된다.

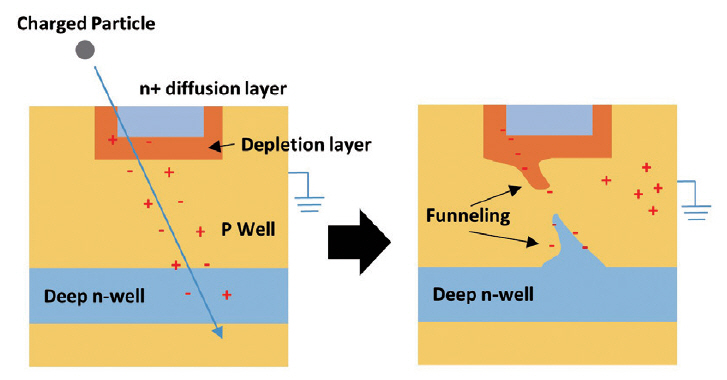

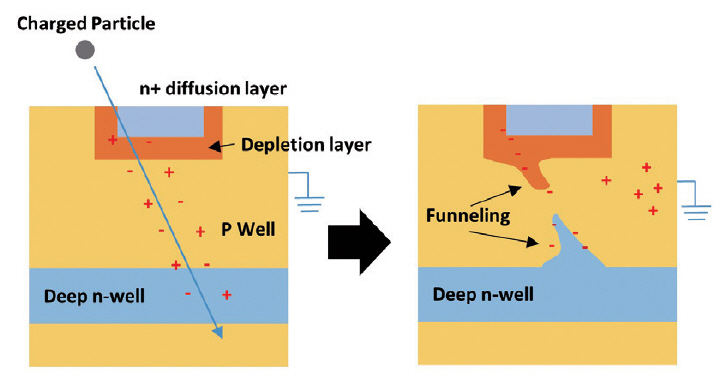

SEE(Single Event Effect; 단일사건 효과)의 경우 에너지를 가지는 입자가 단위 소자에 입사하여 발생되는 전자 정공 쌍이 회로에 펄스를 발생시킴에 따라(그림 4), 메모리 소자의 경우 저장되어 있는 Bit가 반전되어 Upset이 일어나거나(SEU: Single Event Upset), 과도한 전류가 흐르는(SEL: Single Event Latch-up) 상태가 발생하는 것을 말한다. 과도한 경우 회로가 Burning되어 영구적으로 파괴되기도 한다.

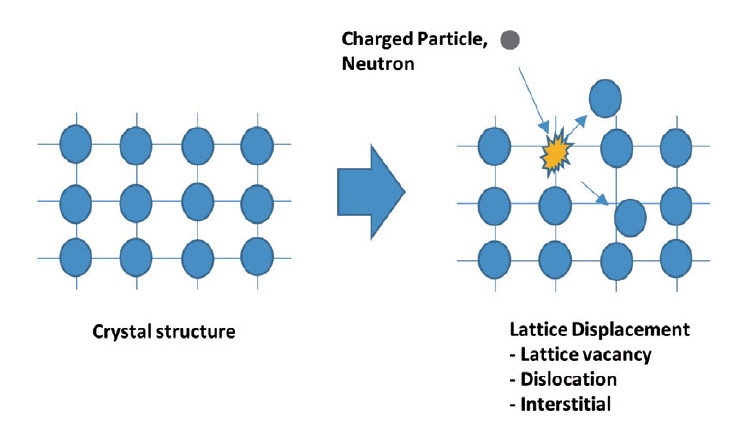

DD(Displacement Damage; 격자결함)는 중성자 혹은 하전 입자 충돌에 의해 발생된 격자 변위로, 결함준위를 생성하여 캐리어의 라이프타임을 감소시킨다(그림 5). 이러한 결함 준위의 영향은 집적도가 높아짐에 따라 영향력이 더 커진다. 특히, GaAS 기반 광전 커플러가 이러한 손상에 취약하다고 알려져 있다.

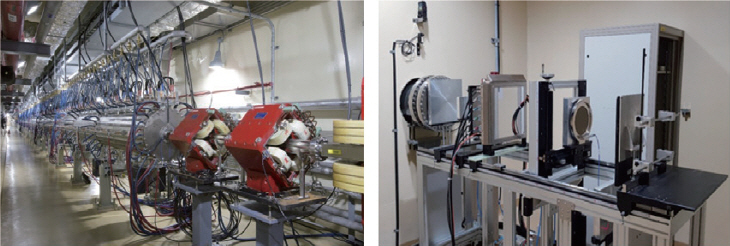

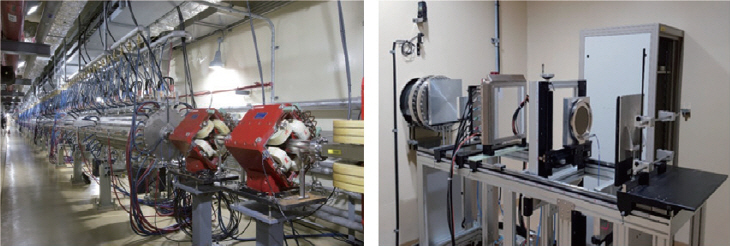

우주방사선의 영향 평가는 인공 방사선 조사 실험을 통하여 확인된다. 한국원자력연구원(KAERI)의 인프라를 통하여 실험하며 TID 경우 정읍 분원 감마선 조사시설을 통하여(그림 6)[2], SEE 경우 양성자 가속시설을(그림 7)[3] 이용하여 측정된다.

현재, 경주 분원을 통해 100MeV 이하의 양성자 조사 실험이 가능하다. 우주방사선 준위와 유사한 100MeV 이상의 양성자 조사 실험, 중이온 조사 실험 등은 선진 해외 기관을 통하여 수행되고 있다.

2. 내방사선 소자 연구동향

우주, 항공, 원자력, 군사 등의 기반 기술을 가지고 있는 선진국에서는 이미 오래전부터 주요시설 핵심 전자모듈에 대하여 내방사화 연구들을 수행하고 있다. 특히 미국의 경우 대표적으로 항공우주국(NASA) 산하의 여러 기관, 에너지부(DOE) 산하 핵 관련 국립 연구소, 고등연구기획국(DARPA) 산하 조직 등에서 관련 전략 연구를 수행하고 있다. 대표적으로 내방사선 소자와 관련하여 Northrop Gruman 방산 업체와 BAE System 등의 위성 시스템 업체가 있다. 일본은 JAXA에서 우주 개발 사업을 수행하고 있으며 위성, 발사체 제조사로 미쓰비시 그룹(전기, 중공업) 등이 있다.

국내 현황은 선진국과 비교하여 시작 단계이며 주로 한국원자력연구원과 한국항공우주연구원 그리고 일부 대학(한국과학기술원, 경희대학교 등)에서 연구를 수행하고 있으며, 본원에서는 질화갈륨(GaN)을 이용한 내방사선 고주파 소자, 저차원 소재를 이용한 내방사선 센서 선행연구가 진행된 바가 있다. 산업계 역시 시작 단계이며, 한화 에어로 스페이스, SK하이닉스, 우주급 전장품 패키징 관련 엠아이디 등에서 연구 활동을 수행하고 있다.

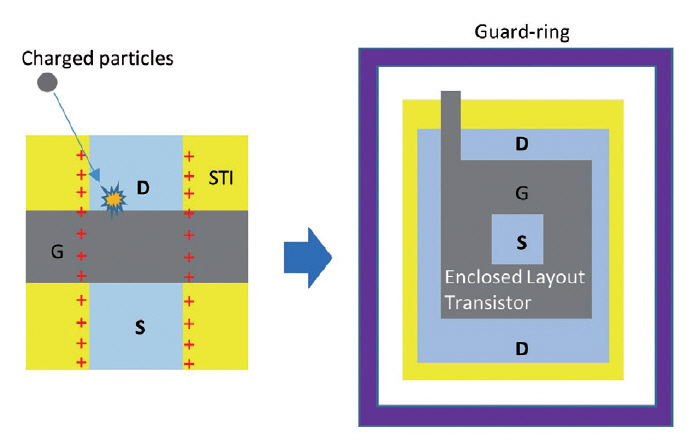

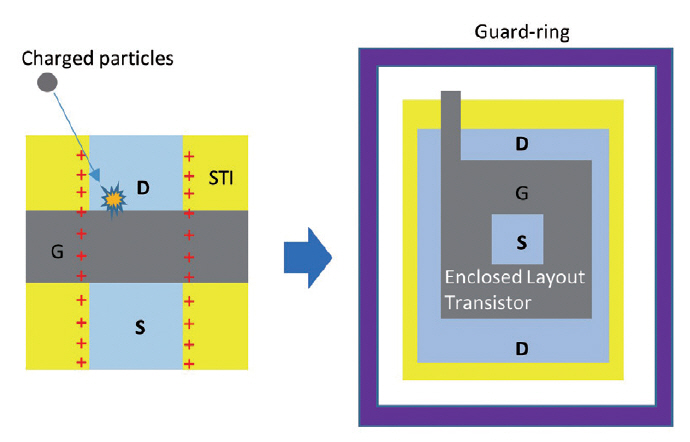

내방사선 소자 연구는 크게 소자/회로/시스템 레벨에서 구분되며, 소자 레벨에서 대표적으로, 원자 간 결합이 강한 반도체 물질(GaN, SiC, …) 기반, 또는 SOS(Silicon on Sapphire) 웨이퍼, SOI(Silicon on Insulator) 웨이퍼 기반의 내방사선 소자 구현 접근 방법이 있다. Layout 측면에서 Enclosed Layout Transistor, Guard Rings 등의 디자인 기술이 있으며[4], 회로 측면에서 DCC(Differential Charge Correction)[5], DICE(Dual Interlocked Cell)[6], TMR(Tripple Moduler Redundancy)[7]과 같은 대표적인 회로 설계 기술이 있다. 시스템 레벨에서는 소프트 에러를 수정하는 방법으로 EDAC(Error Detection and Correction) Technique[8] 등이 있다.

재료적 측면에서 일반적으로 격자 변위를 발생시키는 Ed(Displacement threshold energy; 격자변위발생 최소 에너지)가 높은 반도체 물질이 우주방선으로부터 야기되는 격자결함에 내성이 강하여 내방사선 특성이 우수하다고 알려져 있다. 이러한 격자변위발생 최소 에너지는 원자 간 결합에너지가 클수록 더 높으며, 원자 결합에너지는 원자 간 거리를 통해 가늠될 수 있다. GaN, SiC와 같은 넓은 밴드갭 물질이 Si의 Ed에 비하여 약 2배 크며, 고온/고전압에 안정한 물리적 특성으로 인해 우주 환경 소재로 주목받고 있다[9].

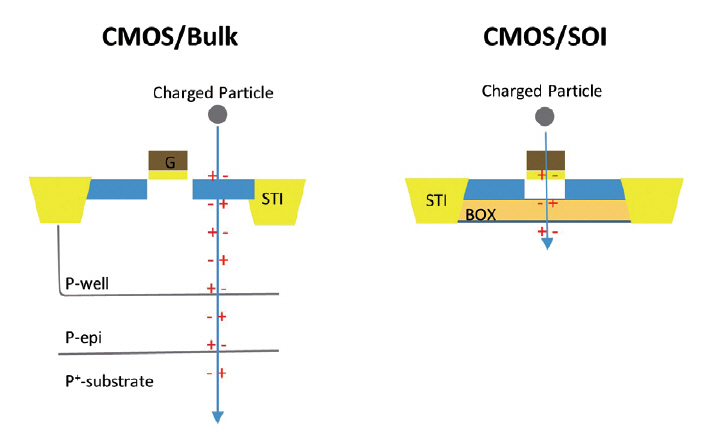

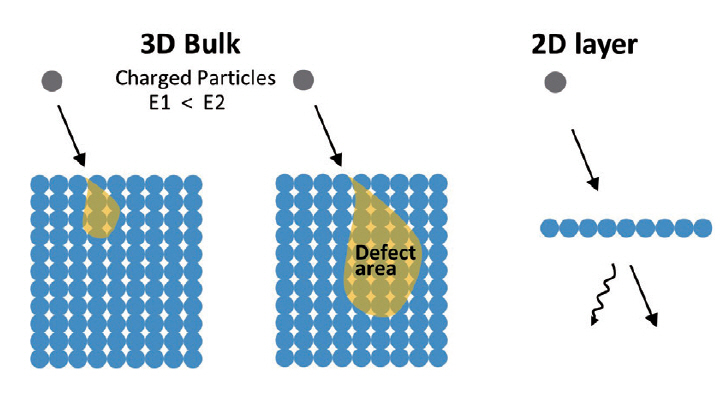

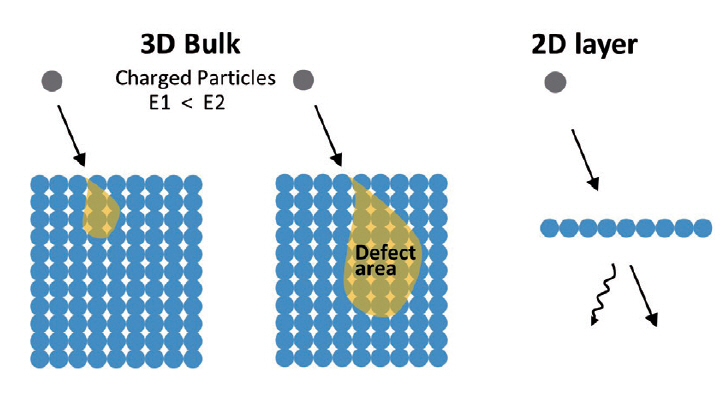

다음으로 웨이퍼 구조적 측면에서, SOI 웨이퍼 기반 소자가 방사선 환경에서 SEE에 강인하다는 것은 선행연구를 통해 알려져 있다[10]. 박막의 Si layer가 BOX(Buried OXide) 유전층 위에 놓여 있는 구조를 갖는다. 박막 실리콘의 구조적 특성으로 인해 짧은 SE 펄스와(벌크에 비해 방사선 궤적에 따라 전리되는 하전량이 작음; 그림 8) 방사선에 대한 작은 반응 볼륨으로 SEE 대한 내성의 특성을 갖는다[11].

Layout 관점에서, 그림 9와 같이 소자 간 누설전류를 차단하는 Guard-ring Layout 기술이 있다. 또한, 대표적으로 TID 개선을 위해 STI(Shallow Trench Isolation)-채널 컨택을 회피하는 ELT(Enclosed Layout Transistor) 디자인이 있다. TID 현상은 STI-채널 경계 지역뿐만 아니라 Gate 유전층의 볼륨 두께에 의존한다고 알려져 있다[12]. Gate 유전층은 두꺼울수록 방사선과 상호작용으로 결함 준위가 많아진다. 다음으로 3차원의 얇은 지느러미(Fin) 모양의 FinFET 구조에 대해 전자쌍 생성 확률이 낮을 것으로 기대되어 내방사선 연구가 이루어지고 있다[13].

국내, SK하이닉스에서는 방사선에 대한 메모리 반도체의 영향에 대하여 1990년대 학계 및 업계에 보고된 이후로 지속적으로 방사선이 반도체에 미치는 영향을 연구 중이며(NSER: Neutron Soft Error Rate, TID), 최근 반도체의 미세화와 저전력으로 개발되면서 SK하이닉스에서도 외부 방사선에 의한 영향을 줄이기 위한 소자, 소재적인 내방사선 특성 개발 및 평가 기술을 개발하는 데 국내외 다양한 가속기 시설활용을 검토하여 연구를 수행하고 있다.

한편, 그림 10과 같이 방사선 충돌 시 3D Bulk 물질에 비해 현저히 낮은 2D 구조 결함생성 특성으로 인하여 내방사선 특성을 탐구하는 기초 연구들이 있다[14].

2차원 반도체 물질을 이용하면, 방사선에 의해 물리적으로 발생할 수 있는 격자결함을 최소화[15]하며, 원자층 두께로 인해 방사선 궤적에 따라 유도되는 하전 입자를 무시할 수 있어 SEE, DD 현상을 근본적으로 해결할 수 있을 것으로 기대된다. 따라서, 본원의 소재부품원천연구본부에서는 이러한 근본적 문제들을 해결할 수 있는 나노 신소재를 활용하여 내방사선 소자 연구를 단계적 수행 중이다[16].

3. 방사선 차폐 소재 연구동향

우주환경 소자 개발 관점에서, 기존의 위성 구조물 혹은 전자장비 하우징에는 알루미늄 합금이 널리 사용되고 있으나, 우주 구조체의 경량화 요구가 증가하면서 알루미늄을 대체할 수 있는 경량 재료의 필요성이 증가하고 있다. 특히 프로세서, 메모리와 같은 고집적 소자는 방사선에 민감한 소자로 국부적으로 TID가 완화될 수 있게 차폐 소재, 패키징 기술 개발이 필요하다.

방사선의 차폐 설계 시 방사선원별 상호작용 특성이 고려되어야 한다. 포톤의 종류인 감마선은 물질과 광핵반응, 전자쌍생성, 광전효과와 같은 흡수 상호작용을 가지며 원자 궤도의 전자와 탄성 충돌하여 컴프턴산란 현상이 나타난다. 수 MeV 영역에서는 컴프턴산란, 그 이상에서는 전자쌍 생성이 높은 반응확률을 갖는다. 일반적으로 원자번호가 크고 밀도가 높은 물질일수록 감마선 차폐에 용이하다.

중성자는 전기적으로 중성을 띠므로 원자의 쿨롱장에서 직접적으로 상호작용이 일어나지 않으며 매질을 방사화시킨다. 산란과 중성자를 흡수하는 기작을 적절히 이용하여 차폐하는 것이 필요하다. 대표적인 중성자 차폐제로 물, 파라핀, 폴리에틸렌, 리튬, 카드뮴, 붕소, 콘크리트 등이 있으며, 수소의 함유량과 중성자 흡수 단면적이 크게 영향을 끼친다.

하전 입자들은 매질 내 원자와 충돌하여 이온화시키고 에너지가 감소하게 된다. 고준위 하전 입자는 물질과 상호작용 후 2차 방사선을 발생시킨다. 따라서 차폐 설계 시 이러한 방사선원별 특성이 고려되어야 하며, 상호작용이 복잡하여 몬테칼로와 같은 전산모사를 통한 추측이 필요하다. 효과적 차폐를 위해서는 다중 차폐가 요구된다. 그러나, 방사선의 높은 에너지 준위로 인한 물리적 한계로 인해 활발히 차폐 연구가 진행되고 있지 않다. 국내에서는 한국원자력연구원, 서울대 등에서 금속성 나노 분말 혼합제를 이용하여 경량화한 차폐제 특성을 보고하고 있다[17]. 한국과학기술원 인공위성연구소에서는 탄소섬유 복합재를 이용하여 국부적 차폐가 가능함을 보였다[18]. 의료용 차폐제는 계명대 등에서 연구가 이루어지고 있다.

Ⅲ. 우주급 EEE 규격, 패키징 기술

인공위성 개발에 적용되는 모든 부품은 시스템 특성상 개발 완료된 제품에 대한 운용 중 추가 수정 및 보완이 어렵기 때문에 안정성과 신뢰성 확보가 매우 중요하게 요구된다. 이러한 인공위성에 사용되는 고신뢰성 우주급 EEE 부품은 우주산업 선진국인 미국, 유럽, 일본 등에서는 위성 통합시스템에서부터 서브시스템 및 단위부품에 이르기까지 신뢰도 수준을 정해 우주 품질 요건을 국가적 차원에서 제작에서 검증 시험까지 모든 절차에 대해 매우 엄격한 품질 규격을 규정 및 요구하고 있다. 우주급 EEE 소자 중에서 가장 대표적으로 사용되는 IC(Integrated Circuit)에 대한 인증시험 규격인 MIL-PRF-38535 (미국), ESCC 9000(유럽) 등이 있다.

그러나, 최근 스타링크를 포함하여 전 세계적으로 개발되는 (초)소형위성들은 저비용 및 경량의 군집위성 특징을 가지고 있으므로, COTS(Commercial Off-The-Shelf) 부품 사용 및 위성 중량, 형상, 대량생산 등을 고려한 군집운용을 준비하고 있다.

우주급과 COTS는 기본적으로 생산량의 차이로 인해 제조업체에서는 생산 관리 기법을 다르게 적용하고 있다. 표 2는 이들 항목의 차이를 보여주고 있으며, 이러한 차이로 인해 전통적인 생산 방식으로 소량 제작의 고신뢰도를 유지해야 하는 우주급 부품 제조비용은 당연히 대량 생산을 하는 COTS보다 수십 배에서 수백 배 비용으로 이어질 수밖에 없다. 그러나, 최근 반도체 공정 기술 및 품질 관리 기법이 점점 발전함에 따라 COTS 생산 비용은 절감되면서 신뢰도는 상당한 수준으로 향상되어 이제는 환경조건이 열악하고 수명주기가 긴 자동차와 방산 제품에도 적용하는 결과를 가져왔다. 이러한 최신 COTS 생산 기술은 대량생산을 통해 지속적인 피드백과 생산 공정 향상으로 불량률을 최소화하게 함으로써 COTS임에도 저비용으로 충분한 고신뢰성의 품질을 갖는다.

표 2 우주급과 COTS 소자의 주요 차이점

최근 대표적으로 COTS 전자 부품 중에서 Automotive급의 AEC-Q100 규격을 만족하는 고신뢰성 부품이 양산되고 있다. 10년 이상의 수명을 보장하고 있어 소형 위성급에 대해서는 충분한 신뢰도를 확보해 줄 것으로 예상하고 있어, 국내외 인공위성 제조사에서 많은 연구와 적용 사례가 점차 생기고 있다.

해외 위성업체의 경우 회로 및 요구기능에 따라 COTS에서부터 Space급을 다양하게 활용하고 있으며, 유럽의 위성업체인 A社 경우 실용급 위성에 자체 Up-screening을 적용하여 COTS 부품을 적용하고 있으며, 실례로 국내 삼성전자의 FLASH 메모리가 적용된 바 있다.

국내 실용급 위성 개발에 사용되는 우주급 소자들은 현재 전량 수입에 의존하고 있으며, 이에 막대한 우주개발 관련 해외 수입액 중 우주급 EEE 소자 부분이 상당 부분 외화로 지출되고 있다. 특히, 우주급 IC류는 대부분 제조국가별 수출허가를 받도록 되어 있으며, 허가지연으로 인한 납기 지연이 수시로 발생되고 있어서, 국내 위성개발 일정에 영향을 주고 있다.

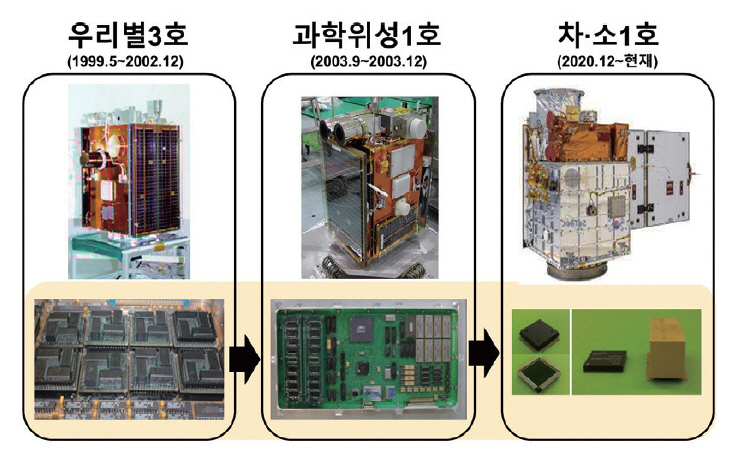

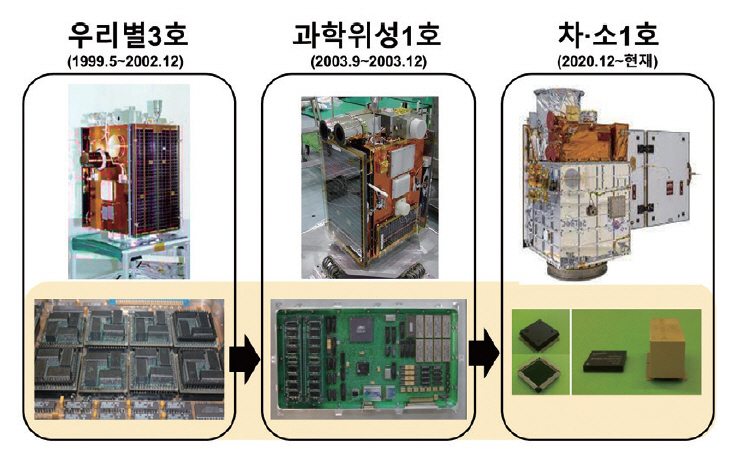

국산 메모리가 국내에서 개발된 인공위성에 적용된 사례는 그림 11에 나타내었다. 우리별3호와 과학위성1호에는 삼성전자의 SRAM, Flash 메모리, SDRAM이 적용되었으며, 차세대소형위성1호에는 SK하이닉스의 DDR SDRAM이 적용되었다. 세 가지 사례 모두 상용메모리를 적용하였지만 우주에서의 정상 동작이 확인되었으며, 이상 현상에 대비하여 EDAC 코드를 적용하여 에러를 복구할 수 있도록 설계되었다[19].

초소형 위성과 같은 무게와 공간적인 제약을 갖는 시스템의 패키징은 기존의 반도체 공정만으로 한계를 극복하기 힘들다. 최근에 해리스 사(Harris Co.)에서는 미니큐브 위성 내의 전자 부품들이 복잡한 구성 요소를 가짐에도 불구하고 소형화와 경량화가 중요한 점에 착안하여, Nano-dimension 사의 Dragonfly Pro 3D 프린팅 기술을 사용하여 소규모 위성에 사용되는 전자 부품을 3차원 패키징된 구조로 개발하였고[20], Mini-Cube, LLC 사는 초소형 PocketQube 위성(50 × 50 × 50mm) 내에 전자제품, 카메라, 라디오 시스템을 패키징하도록 탄소복합 재료를 적층 제조하여 차폐 특성과 강성, 낮은 질량, 매우 매끄러운 표면 마감을 동시에 만족하는 제품을 제작하였다[21]. 이밖에 제프 베이조스 아마존 창업자가 이끄는 우주기업 블루오리진도 뉴셰퍼드 로켓과 우주선에 금속 및 다중 차폐제, 전자부품을 포함하여 400개 이상의 3D 프린팅 부품 사용을 공언하고 있고, 호주의 스피드쓰리디(SPEED3D), 유럽의 판게아(PANGEA) 에어로스페이스 등도 잇따라 3D 프린팅 로켓 엔진 개발에 나서는 등 뉴스페이스를 맞은 세계 우주산업계에 3D 프린팅이 새로운 물결을 형성해가고 있다[22].

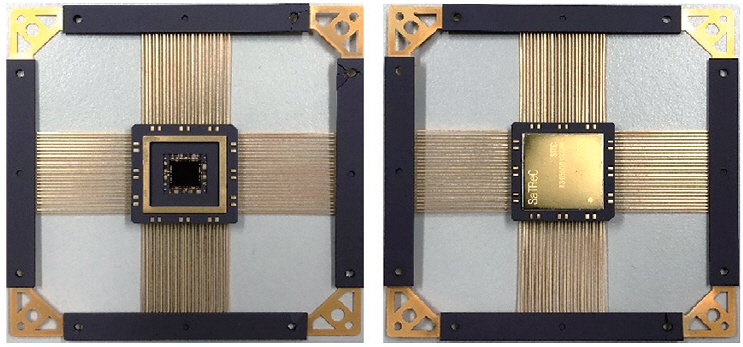

국산 메모리의 성공적인 인공위성 적용 경험이 있는 한국과학기술원 인공위성연구소와 국내 우주급 EEE 소자 전문업체인 (주)엠아이디는 우주용 메모리 부품 국산화 개발 경험을 바탕으로 국내 산업체의 우수한 상용급 메모리 칩을 이용하여 고신뢰성의 세라믹 형태의 Hermetic 패키징 기술(그림 12)과 우주기술 전문기관의 우주급 부품 검증 기술을 융합하여 고신뢰성 우주급 메모리 부품 국산화 개발 연구를 진행하고 있다.

특히 초소형, 경량, 저비용 우주 구조체로 민간 상업화될 New Space 시대 흐름을 고려하여, 비교우위의 신뢰성을 갖는 COTS 부품의 우주급 패키징을 통하여(TID 개선) 우주급 EEE 소자로 제고시킬 수 있는 기술 개발의 활성화가 요구된다.

Ⅳ. 결론

ICT 전장품이 고도화될수록 우주방사선 환경 영향이 커지고 있다. 유형별 우주방사선 영향을 검토하고 물질, 회로, 시스템에 해당하는 주요 내방사화 기술을 살펴보았다. 또한, 내방사선 기술과 분리할 수 없는 방사선 차폐 설계의 특성과 우주급 EEE 규격과 패키징 개발 현황을 알아보았다. 나아가 향후 본원의 신소재/소자 기술을 바탕으로 우주급 패키징 기술과 내방사화 기술 개발에 도움이 되길 기대한다.

용어해설

우주방사선 다양한 천문사건/환경에 의해 우주에서 끊임없이 지구로 날아오는 높은 에너지를 지닌 각종 입자와 전자파

내방사선 방사선 노출에 의해 반도체 물질이 전리되거나 결함이 생기는 이상 현상으로부터 전장품이 견디는 성질

방사선차폐 방사선 노출 시 전장품이나 생물체 등의 피폭을 방지하기 위해 방사선을 흡수하거나 차단하는 것

약어 정리

CMOS

Complementary Metal Oxide Semiconductor

COTS

Commercial off the Shelf

DCC

Differential Charge Correction

DD

Displacement Damage

DICE

Dual Interlocked Cell

EDAC

Error Detection And Correction

EEE

Electrical Electronic and Electromechanical

ELT

Enclosed Layout Transistor

FinFET

Fin Field Effect Transistor

ICT

Information Communication Technology

NSER

Neutron Soft Error Rate

SEE

Single Event Effect

SEL

Single Event Latch-Up

SEU

Single Event Upset

SOI

Silicon On Insulator

SOS

Silicon On Sapphire

STI

Shallow Trench Isolation

TID

Total Ionizing Dose

TMR

Tripple Moduler Redundancy

참고문헌

그림 1

그림 2

그림 3

그림 4

그림 5

그림 6

그림 7

그림 8

그림 9

그림 10

그림 11

그림 12