광집적화 기술 한계 극복: 실리콘 포토닉스 기반 광트랜시버 기술 동향

Overcoming Limitations of Optical Integration Technology: Trends of Silicon Photonics-Based Optical Transceiver Technology

- 저자

-

이정찬광네트워크연구실 jclee@etri.re.kr 유상화광네트워크연구실 sanghwa@etri.re.kr 서동준광네트워크연구실 sdj@etri.re.kr 박혁광네트워크연구실 parkh@etri.re.kr 이준기광네트워크연구실 juneki@etri.re.kr

- 권호

- 37권 3호 (통권 196)

- 논문구분

- 5G/6G 통신 및 미디어 기술

- 페이지

- 11-22

- 발행일자

- 2022.06.02

- DOI

- 10.22648/ETRI.2022.J.370302

본 저작물은 공공누리 제4유형: 출처표시 + 상업적이용금지 + 변경금지 조건에 따라 이용할 수 있습니다.

본 저작물은 공공누리 제4유형: 출처표시 + 상업적이용금지 + 변경금지 조건에 따라 이용할 수 있습니다.- 초록

- The development and application of silicon photonics technology to terabit optical transmission are expected in the future. Silicon photonics technology is recognized as the only technology focusing on increasing the bandwidth of data center switches. High-density integration-based small optical subassemblies, optical engines, and optical transceivers are converged with the silicon photonics technology to accelerate a revolution in optical interfaces.

Share

Ⅰ. 서론

바이오 헬스, AI(Artificial Intelligence), VR(Virtual Reality), 자율 로봇 기술 등의 도입과 비대면 업무·산업의 급증으로 인해 글로벌 ‘테크 트렌드’로 디지털 전환이 가속화되고, 초고속 인터넷 통신 인프라 구축은 사회, 기술, 경제, 환경을 포함한 우리 사회 전반에 필요한 국가적 임무로 더 강조되고 있다[1]. 이러한 사회적 환경 변화에 따라 데이터 센터 IP 트래픽은 기하급수적으로 증가하여 2~3년마다 이더넷 스위치와 연결 대역폭을 두 배로 늘려야 했다. 대역폭 확장은 전송률을 높이고 이더넷 스위치 패키지 당 물리적 데이터 레인 수를 늘림으로써 발전하고 있다[2].

지난 10여 년 동안의 스위치 ASIC(Application Specific Integrated Circuit) 대역폭, 라우터 및 전달망 장비 용량의 진화를 보여준다. 스위치 ASIC 대역폭은 2010년 0.64Tbps에서 2020년 25.6Tbps로 40배 증가했고, 2022년에는 51.2Tbps로 발전할 것으로 전망된다[3]. 라우터 및 전달망 장비 용량의 경우, 2017년 대비 2022년 각각 7배 및 5배 증가할 것이며, IEEE802.3-ck 표준[4] 기반의 106.25Gbps 512 레인 전기 인터페이스가 적용되고 있다. 2025년에는 각각 512Tbps 및 256Tbps로 발전할 것으로 전망되는데, 기술적으로 주목할 만한 점은 기존 ‘전기 신호 백 플레인 인터페이스’가 ‘광신호 백 플레인 인터페이스’로 대체될 것으로 전망되며, 이는 ‘광 인터페이스 변혁(Optical I/F Revolution)’을 예고하고 있다는 것이다[5,6].

2004년 인텔(Intel)사에서 CMOS(Complementary Metal-Oxide Semiconductor) 공정으로 1Gbps 실리콘 광변조기를 구현한 이래로 본격적인 실리콘 포토닉스 시대가 개막되었다[7]. 이후 관련 연구 논문 발표 건수가 매년 20배씩 증가할 정도로 발전을 거듭해 왔으며, 실리콘 포토닉스 공정과 산업체 및 관련 서비스 기반이 급속도로 발전하게 되었다[8]. 테라비트(Terabit) 광전송을 위한 기반 기술로 저손실 스위치 ASIC과 광학 소자들을 함께 패키징하여 전력 효율성을 높이는 연구가 진행되고 있는데, 실리콘 포토닉스 기술 기반 집적화된 소형 광학 엔진(Optical Engine)과 광트랜시버(Optical Transceiver)를 중요한 해결 방법으로 보고 있다[9].

본고에서는 ‘광집적화 기술 한계 극복: 실리콘 포토닉스 기반 광트랜시버 기술’ 관련해서 다음과 같은 관점에서 동향을 서술하고자 한다.

첫째, 실리콘 포토닉스 송신 소자

둘째, 실리콘 포토닉스 수신 소자

셋째, 실리콘 포토닉스 수동 소자

넷째, 실리콘 포토닉스 광학 엔진 및 광트랜시버

Ⅱ. 실리콘 포토닉스 송신 소자

1. 국내·외 동향

주요 선도업체에서는 채널당 100Gbps 속도의 실리콘 송신 소자를 개발하고, 채널 수를 확장해 400Gbps, 800Gbps 용량의 제품 개발 결과를 발표하고 있다. 상용화 관점에서는 저전압 구동이 가능한 마하젠더 광변조기, 링변조기의 안정성과 신뢰성 확보, LD 집적화, 광소자와 전자소자 간 패키징 구조 등이 주요한 이슈로 떠오르고 있다.

실리콘 송신 소자 관련 주요 산업체 및 연구기관의 최근 기술 동향은 다음과 같다.

Analog Photonics 사는 O-, C-, L-밴드의 실리콘 포토닉스 PDK(Process Design Kit) v3.0을 개발 완료하였으며, 세계 최고 수준 변조 효율(VπL ≤ 0.7Vcm)과 2Vppd 저전압 구동 마하젠더 광변조기를 통해서 100Gbps PAM-4(Pulse Amplitude Modulation 4-level) 광신호 변조 결과를 발표하였다[10,11].

Intel 사는 800Gbps 2×FR4, DR8 광송신 소자 개발을 완료하였다[12]. 800Gbps 광소자에는 8개(4×λs)의 이종접합(Heterogeneously Integrated) 레이저가 집적화되어 있다. 아울러, 링변조기를 이용해서 단일채널 200Gbps 동작 결과를 보고하였다[13].

CISCO 사는 EIC(Electronic Integrated Circuit) 칩과 PIC(Photonic Integrated Circuit) 칩이 집적화된 3차원 멀티-칩 모듈 형태의 100Gbps 광송신기를 개발하였다. III-V/Si 이종접합 레이저 기술과 3개의 세그먼트로 분할된 마하젠더 광변조기를 도입하여 1Vpp 저전압 구동 특성을 발표하였다[14].

Ayar Labs 사는 25Gbps×16채널 고집적 EPIC(Electronic-Photonics Integrated Circuit) 광 I/O 칩(TeraPHY) 기술을 개발하였다. TeraPHY는 45nm SOI CMOS 프로세스 공정을 사용하였으며, 2.5차원 CPO(Co-Packaged Optics) 패키징 형태를 가지고 있다. 최근 8개의 광출력 포트를 갖고 포트마다 8개 파장의 광신호를 다중화해서 출력하는 64채널 레이저 모듈(SuperNova)을 개발했으며, 파장당 16Gbps 속도로 총 1Tbps 용량의 전송 결과를 발표하였다[15,16].

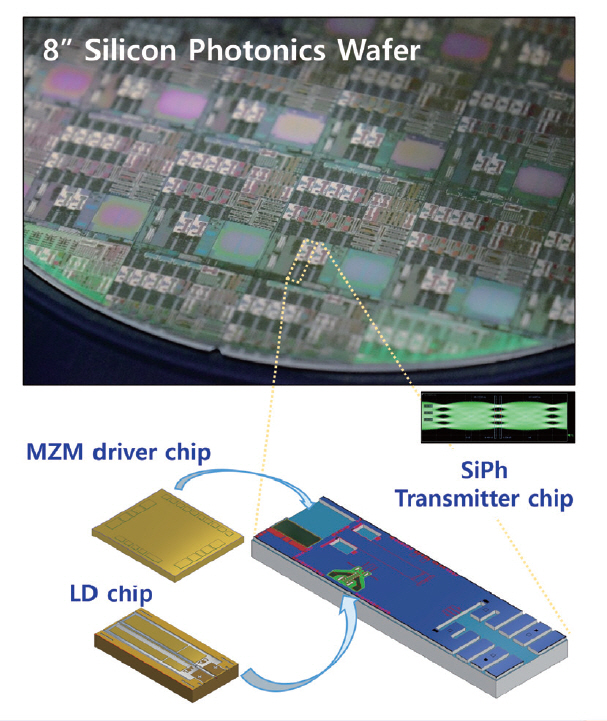

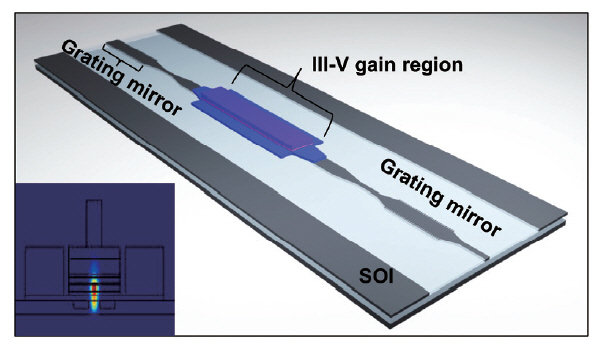

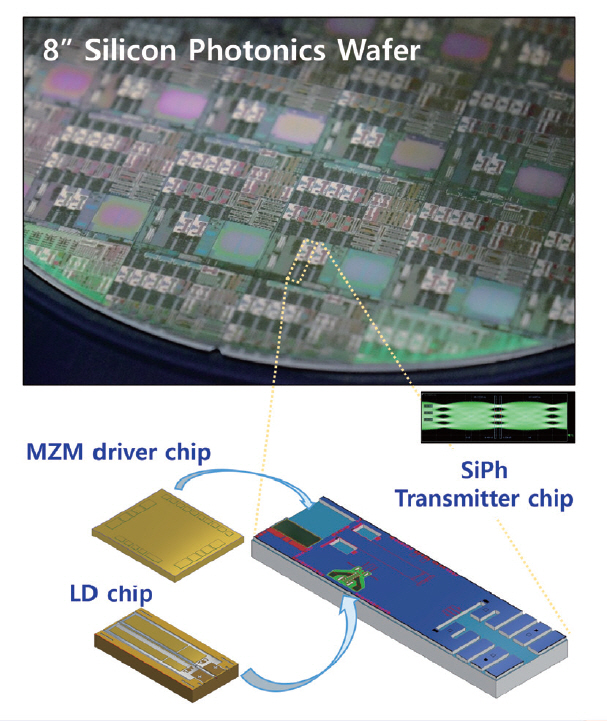

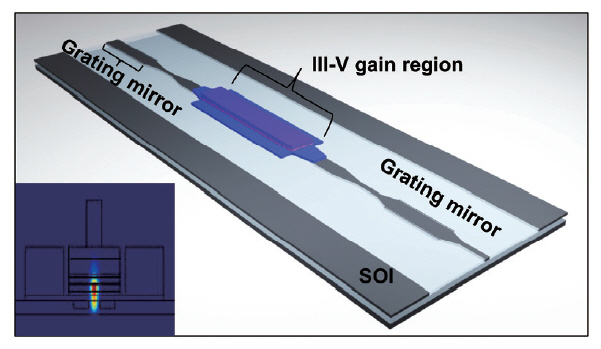

ETRI는 실리콘 포토닉스 파운드리와 공정 레시피 정립을 통해서 실리콘 포토닉스 소자 기술의 연구, 개발을 진행하고 있다. 그림 1과 같이 실리콘 포토닉스 광송신 칩에 구동 드라이버 칩을 3차원 집적화 및 와이어 본딩 연결 방식으로 접근하고 있으며, 렌즈가 필요 없는 III-V/Si 하이브리드(Hybrid) 레이저와 100Gbps 저전압 마하젠더 광변조기를 연구, 개발하고 있다. 테라비트(Terabit) 다채널 광송신 칩 광원 기술을 확보하기 위해 그림 2와 같이 III-V/Si 하이브리드 레이저의 이득 매질 III-V 에피와 SOI 웨이퍼에 형성된 실리콘 격자(Grating) 및 광도파로에 대한 연구가 진행 중이다.

2. 기술적 이슈

광원 기술 관련해서 실리콘은 간접 천이형(Indirect Band Gap) 물질로 빛을 생성하기 어렵다. 이에 실리콘 포토닉스 광원 솔루션으로 DFB-LD(Distributed Feedback-Laser Diode) 칩을 실리콘 칩에 플립-칩 본딩하여 광 커플링하는 하이브리드 집적화 방식 레이저와 III-V 에피를 실리콘 웨이퍼에 본딩하여 구현한 하이브리드 레이저가 연구되고 있다[17,18].

광변조기 기술 관련해서는 마하젠더 광변조기, 마이크로링 광변조기, 전계흡수 광변조기, LN(Lithium Niobate)/Si 하이브리드 및 TFLN(Thin-Film LN) 광변조기로 구분할 수 있으며, 다음과 같은 이슈들이 연구되고 있다.

첫째, 순수한 실리콘 기반 마하젠더 광변조기는 광도파로에 불순물을 도핑하여 전자와 정공 밀도 변화로 광인덱스가 변조되는 플라즈마 디스퍼전(Plasma Dispersion) 효과를 이용한다[19]. CMOS 표준공정을 이용할 수 있는 장점이 있지만, 낮은 전광 변환 효율로 인해 구동 전압이 높고, 대역폭이 좁은 단점이 있다. 하지만, 최근 광변조기 성능 메트릭스의 최적화를 통해 ~37GHz 수준의 대역폭과 1.7Vppd 저전압의 106Gbps 광신호 변조 및 편광 결합된 IQ(In-phase Quadrature) 광변조기 활용 단일 채널 테라비트급 광신호 전송 결과가 보고되었다[20,21].

둘째, 마이크로링 변조기(Micro-Ring Modulator)는 마하젠더 광변조기보다 크기가 작고 femtojoule(fj) 수준의 초저전력, 50GHz 이상의 변조 대역폭 장점이 있다. 이로 인해서 CPO(Co-Packaged Optics) 모듈의 광변조 솔루션으로 많이 고려되고 있다[22]. 그러나, 공진 파장이 민감하게 변하여 전력 소모가 큰 히터와 제어회로가 필수적으로 요구되는 문제점이 있다[21].

셋째, 전계흡수 광변조기(EAM: Electro-Absorption Modulator)는 전기장에 의해 밴드-에지가 이동하여 흡수 계수가 변하는 QCSE(Quantum Confined Stark Effect)로 인해 광신호를 변조한다[23]. 그동안 다중 양자우물 GeSi EAM은 C-, L-밴드 파장에서 많은 연구가 이루어졌다. 최근 O-밴드 파장 대역, 2Vpp 구동 전압, ~50GHz의 대역폭에서 60Gbps 광신호 변조에 성공하였다[24]. 이로써 GeSi EAM는 데이터 센터 내 광 인터커넥션으로 많은 활용 기대를 모으고 있다.

넷째, LN/Si 하이브리드 및 TFLN(Thin-Film Lithium Niobate) 광변조기는 광도파로가 큰 인덱스 차이(Δn >0.7)를 가지며, 삽입손실이 매우 작고, 전기장에 의해 광인덱스의 위상이 전기장의 세기에 선형으로 빠르게(~fs) 변화하는 포켈스 효과(Pockels Effect)를 이용한다[25]. 순수 실리콘을 이용해서 저전압, 100GHz 수준의 대역폭, 그리고 저손실의 요구사항을 동시에 만족하기 어렵다. 이를 극복하기 위한 해결책으로 LN(LiNbO3) 단결정 박막을 광도파로로 이용하는 LNOI(LN-On-Insulator) 플랫폼이 최근 급부상하고 있다. 순수 실리콘 광변조기의 성능 메트릭스 사이에서 트레이드-오프를 깨면서 대역폭과 변조 효율을 대폭 향상시킬 수 있다. BCB(Benzocyclobutene)로 SOI 웨이퍼와 LN 단결정 박막을 본딩하여 ~60GHz 대역폭 120Gbps 광변조가 가능한 LN/Si 하이브리드 광변조기가 발표되었다[26]. 이후 SOI 기판 없이 LNOI 웨이퍼에 편광결합 IQ 광소자를 구현하여 ≥100GHz 대역폭 성능으로 단일채널 1.3Tbps 64QAM(Quadrature Amplitude Modulation) 변조 결과가 발표되었다[27].

Ⅲ. 실리콘 포토닉스 수신 소자

1. 국내·외 동향

광검출기 구성에 주로 사용되는 저마늄(Germanium, Ge)은 실리콘과 같은 IV족 물질로 실리콘에 직접 성장시키는 것이 상대적으로 쉬울 뿐만 아니라 물질 내부에서 전자 이동성(Mobility)이 높고 광통신에 사용되는 파장 대역에서의 흡수 계수가 높은 장점이 있다.

실리콘 수신 소자 관련 주요 산업체 및 연구기관의 최근 기술 동향은 다음과 같다.

Intel 사는 표면 입사형 저마늄 25Gbps 광검출기를 구현하였으며, 이후 100Gbps까지 향상되었다[28]. 또한, 1,310nm 대역에서 35GHz 대역폭과 0.23A/W 응답도 성능을 얻었고, 100Gbps 초소형 실리콘 링 구조 광검출기를 발표하였다[29].

GlobalFoundries 사는 저마늄 전자 증식 영역(Multiplication Layer)을 포함하는 PIN(Positive-Intrinsic-Negative) 구조를 실리콘층에 형성하고 저마늄을 성장시켜 1,310nm 파장 대역에서 30GHz 이상의 대역폭과 26A/W의 TE(Transverse Electric) 응답도를 갖는 APD(Avalanche Photo-Detector)를 연구하였다[30].

IMEC 과 Ghent 대학 및 Eindhoven 대학 연구팀은 실리콘층 위에 금속층을 구현하고 poly-Si 재질의 구조물을 이용해 응답도 특성을 향상시킴으로써 1,310nm 파장에서 67GHz 이상의 대역폭, 0.93A/W의 높은 응답도 특성의 100Gbps RZ(Return-to-Zero) 신호 수신 결과를 발표하였다[31].

IHP와 Keysight, Berlin 공과대학 연구팀은 도핑된 실리콘을 저마늄 측면에 에피택시하여 PIN 접합의 진성영역의 폭을 획기적으로 줄이는 방법을 통해 110GHz 이상의 대역폭 성능을 내는 광도파로형 저마늄 광검출기를 개발하였다[32]. 또한, Virginia 대학과 함께 대역폭을 최대 265GHz까지 확장하였고, 1,550nm 파장에서 0.3A/W의 응답도 결과가 발표되어 Ⅲ-Ⅴ 물질 기반의 광검출기에 비해 대역폭 성능이 낮았던 저마늄 광검출기의 활용 가능성을 증명하였다.

ETRI는 저마늄 내의 전기장 세기 강화를 통해 대역폭을 증가시킨 광검출기 구조 연구결과를 발표하였으며[33], 실리콘 포토닉스 광검출기와 TIA(Trans-Impedance Amplifier)를 3차원 집적화한 실리콘 포토닉스 광수신 칩에 대한 연구가 진행 중이다.

2. 기술적 이슈

실리콘 포토닉스 기반의 광검출기 기술에 있어 기존의 화합물 기판을 사용하는 광검출기에 비해 저마늄 광검출기의 성능이 좋지 못하여 실리콘 포토닉스 기반 광검출기의 활용에 대해서 많은 의문이 있었으나, 최근 200GHz 이상의 대역폭을 갖는 저마늄 광검출기가 연구되어[32], 실리콘 포토닉스 기반의 광검출기가 채널당 100Gbps 이상의 고속 트랜시버 제작에 있어 주요한 솔루션이 될 가능성이 열린 상황이다.

Ⅳ. 실리콘 포토닉스 수동 소자

1. 국내·외 동향

파장 다중화는 광통신 용량을 증가시키기 위한 가장 유용한 방법으로 실리콘 포토닉스 기술과 같은 PIC 기술에 있어서 단일 집적 가능한 파장다중화기/역다중화기는 매우 중요하다. 실리콘 포토닉스 기술 연구 초기부터 실리콘 소자 층을 이용한 AWG(Arrayed Waveguide Grating), Echelle Grating, 마하젠더 간섭계나 링공진기, 혹은 Grating 기반의 광다중화기/역다중화기가 연구되어 왔다[34].

실리콘 수동 소자 관련 주요 산업체 및 연구기관의 최근 기술 동향은 다음과 같다.

PETRA에서는 비대칭적 마하젠더 간섭계를 직렬 연결한 Flat-Top 필터 결과를 발표하였다[35]. 마하젠더 간섭계로 이루어진 4채널 필터에 광검출기를 연결하여 마하젠더 간섭계 내부의 위상을 검출할 수 있는 구조를 제작하고, 제어를 위한 전자칩을 ASIC화 한 결과를 보여주었다. 이후 PIC 칩에 Controller 칩을 플립-칩 본딩으로 부착하여 50GHz 간격의 32채널 DWDM 광역다중화기에서 인접채널 잡음(Cross Talk)을 -38.5dB 이하로 제어할 수 있음을 보여주었다[36].

Texas A&M 대학교는 링(Ring) 위상 제어기와 마하젠더 간섭계 형태의 커플러로 이루어진 4차 필터에서 히터로 위상을 자동제어하는 방법을 제시하였다[37]. 이를 통해 온도 의존성 해소의 해법이 될 수도 있을 것으로 기대된다.

CISCO는 SiN 기반 마하젠더 타입의 필터에 있어서 도파로의 선폭 및 두께에 따라 굴절률의 선폭 및 두께에 대한 의존성이 달라진다는 점을 이용하여 중심파장 변이의 IQR(Inter-Quartile Range) 값은 0.4nm 이하로 기존 1.4nm보다 현저히 줄어든 결과를 발표하였다[38].

ETRI는 다채널 광송수신 모듈에 적용하기 위한 파장다중화/역다중화 기능을 가지는 소자로 AWG와 마하젠더 간섭계에 기반을 둔 필터를 개발하고 있다. 편광의존성을 줄이기 위하여 모드 혼합에 기반을 둔 PSR(Polarization Splitter Rotator) 소자 연구가 진행 중이다.

2. 기술적 이슈

실리콘 소자층을 이용하는 필터 소자는 크게 세 가지 해결해야 할 이슈를 가지고 있다.

첫째, 실리콘 도파로는 높은 굴절률 차로 인하여 공정 불완전성에 민감하다[39]. 도파로의 폭과 두께의 불균일성으로 투과 스펙트럼의 왜곡, 인접채널 잡음의 증가, 투과 대역 중심파장 변이가 발생할 수 있다. 공정 불완전성에 의한 위상 변동을 줄이기 위해 SiN을 이용한 연구가 진행된 바 있다[40]. 실리콘에 비해 SiN은 열광학 계수가 1/7 정도로 작아 온도 의존성을 완화할 수 있지만, SiN 기반의 도파로 역시 코어와 클래딩 굴절률 차가 약 0.5 정도 크므로 공정불완전성에 의한 문제가 여전히 존재한다[41].

둘째, 실리카(Silica)에 비해 20배에 달하는 실리콘의 높은 열광학 계수로 인하여 실리콘 도파로 AWG의 중심파장은 약 0.1nm/℃의 큰 온도 의존성이 있다[37,41,42].

셋째, 굴절률이 높고, 폭과 높이의 비가 큰 도파로 구성으로 인하여 편광의존성이 크다[43]. 이로 인해 높은 복굴절률이 존재하고, TE(Transverse Electric)/TM(Transverse Magnetic) 모드의 중심파장 불일치 이슈가 존재한다.

Ⅴ. 실리콘 포토닉스 광학 엔진 및 광트랜시버

1. 국내·외 동향

400Gbps급 CFP8, OSFP, QSFP-DD, 장거리 OpenZR+ 광트랜시버 표준, 800Gbps, 1.6Tbps급 COBO CPO/NPO/MWIS, OSFP-XD 광트랜시버 표준, IEEE, Ethernet alliance, OIF 국제 표준 등 다양한 단체와 기관에서 광학적, 전기적 규격 그리고 이들의 형상에 대한 표준화 작업이 활발히 진행되고 있다[44-52].

데이터 센터 내 400Gbps 광 인터페이스의 800Gbps, 1.6Tbps 광 인터페이스 수요 전망은 다음과 같다. 현재의 400Gbps 광 인터페이스는 4년 뒤 약 18% 수준으로 낮아지지만, 800Gbps, 1.6Tbps 광 인터페이스는 각각 60%, 23% 수준으로 비중이 높아질 것으로 전망된다[53]. 800G Pluggable와 OSFP-XD는 스위치 보드 전면에 실·탈장되는 반면, COBO, CPO, NPO는 스위치 보드 내부에 실·탈장되는 구조로 비트당 에너지 효율(Energy/bit)을 약 50% 절감할 수 있을 것으로 전망하고 있다[54].

앞서 전망은 COBO, CPO, NPO에 실리콘 포토닉스의 다양한 장점이 있어 가능하게 되었다.

첫째, 고성능(High Performance) 특성으로 실리콘 포토닉스는 25Gbps부터 100Gbps까지 신뢰할 수 있는 성능과 초소형(Ultra Compact) 칩으로 고밀도(High Density) 구성의 장점이 있다.

둘째, 저전력 소모(Low Power Consumption), 신호 무결성(Signal Integrity) 특성으로 전자소자와 결합한 저전력 패키지 구성의 장점이 있다.

셋째, 성숙한 실리콘 공정(Matured Silicon Process), 입증된 CMOS 공정으로 대량 양산 및 저가화가 가능한 장점이 있다.

실리콘 포토닉스 기술의 실 상용화에 있어 주목할 만한 국내·외 산업체로 다음과 같다.

SCINTIL Photonics 사는 실리콘 기판의 광 도파로와 Ⅲ-Ⅴ 화합물 반도체 광 능동 소자 및 광 수동 소자 Patterning/Metalization 기술을 연구, 개발하여 상용화를 위한 단계에 돌입하고 있다[55].

POET Technologies 사는 Ⅲ-Ⅴ 화합물 반도체 광 능동 소자와 실리콘 인터포져(Interposer) 간 본딩(Bonding)을 통한 광학 엔진 플랫폼을 구현하였다[56].

Rockley Photonics 사는 실리콘 포토닉스 기반 소자의 고밀도 패키지 기술을 구현하고 있어 여러 산업체와의 공동 협력을 활발히 진행 중이다[57].

LESSENGERS 사는 광소자 간 광연결에 있어서 기존의 렌즈 광학계에서 탈피하고 폴리머 와이어 구조를 웨이브 가이드로 하여 바로 광 연결하는 독창적인 Direct Optical Wiring 기술을 개발하고 이를 기반으로 소형 광학 엔진을 구현하고 있다[58,59].

실리콘 포토닉스 광학 엔진 및 광트랜시버 관련 주요 산업체 및 연구기관의 최근 기술 동향에 대해 표 1과 같이 정리하였다[5,11,12,14,60-63].

표 1 실리콘 포토닉스 기반 광트랜시버 주요 기술 동향

| Ref. | [60] | [61] | [11] | [5] | [62] | [14] | [12] | [63] |

|---|---|---|---|---|---|---|---|---|

| Affiliation | Intel Corp. | IME | Analog Photonics | Intel Corp. | Intel Corp. | CISCO | Intel Corp. | RANOVUS |

| Publish | IEEE 15th INTERNATIONAL CONFERENCE ON GROUP IV PHOTONICS 2018 | ECTC 2018 | OFC 2020 | J. LIGHTWAVE TECHNOLOGY 2020 | IEEE J. SOLID- STATE CIRCUITS 2021 | OFC 2021 | OFC 2022 | OFC 2022 |

| Data capacity | 400Gbps | 400Gbps | 400Gbps | 1.6Tbps, 800Gbps | 100Gbps | 100Gbps | 800Gbps | 800Gbps |

| Data rate per channel | 50Gbps | 100Gbps | 100Gbps | 100Gbps | 100Gbps | 100Gbps | 100Gbps | 100Gbps |

| Transmission length | - | 500m | 500m | 500m | - | 20km | 2km | - |

| Modulation format | NRZ | PAM-4 | PAM-4 | PAM-4 | PAM-4 | PAM-4 | PAM-4 | PAM-4 |

| Implementation level | Chip | CPO module | Chip | CPO module | Chip | QSFP28 module | Chip | CPO module |

| Integration approach | 2D | 2.5D | 3D | 3D | 3D | 3D | 2D | 3D |

Intel 사는 실리콘 포토닉스 기반 50Gbps×8채널 CWDM-8(Coarse Wavelength Division Multiplexing 8 Channel) 광송신기를 발표하였는데, 실리콘 포토닉스 기반 8채널 광 다중화를 구현한 점이 주목할 만하다[60]. 2020년과 2021년 채널당 100Gbps 실리콘 포토닉스 기반 800Gbps/1.6Tbps CPO 광학 엔진을 발표하여 CPO 기반 데이터 센터 스위치 발전 방향을 제시하였다[5,62]. 2022년 실리콘 포토닉스 기반 100Gbps×4채널(CWDM-4) 2개 블록의 800Gbps 광송신기를 구현, 2km 전송 결과를 발표하였다. Ⅲ-Ⅴ/Si 이종접합 레이저 및 광변조기, 8채널 광 다중화기가 실리콘 포토닉스 기반 단일 집적으로 구현된 특징을 가지고 있다[12].

CISCO 사는 실리콘 포토닉스 기반 단일채널 100Gbps QSFP28 광트랜시버를 개발하고 20km 전송 결과를 발표하였다. 실리콘 포토닉스 광변조기, 광수신기, SerDes, Equalizer, 광변조기용 구동 드라이버, 광수신기용 전치 증폭기(Trans-Impedance Amplifier) 등 광 트랜시버의 모든 구성이 실리콘 포토닉스 기반 단일 집적화되었다는 점이 특징이다[14].

RANOVUS 사는 TE connectivity 사와 공동으로 100Gbps×8채널 단일 집적의 Odin™ 800Gbps CPO 2.0 Silicon Photonics Engine을 발표하였다[63].

2. 기술적 이슈

표 2는 광학 패키지(OSA: Optical Sub-Assembly) 구성과 광학 엔진 및 광트랜시버의 단계별 기술 로드맵이다.

표 2 광학 패키지 구성과 광학 엔진 및 광트랜시버의 단계별 기술 로드맵

1단계는 전-광, 광-전 소자의 구성을 2차원 평면에 패키지하는 수준이며, 2단계부터 3단계까지는 2.5차원 평면을 활용하면서 소형화, 다채널 구성의 정렬 및 패키지하는 수준이며, 4단계는 인터포져 기술의 도입으로 고밀도 인터페이스로 향상되며, 5단계는 전-광, 광-전 소자의 단일 집적화를 기반으로 더욱 고밀도 인터페이스로 향상될 것으로 전망한다. 여기서 중요한 사항은 실리콘 포토닉스 기술과의 융합을 위해서 4단계에서는 실리콘 포토닉스 소자-전자소자 간 하이브리드 구성, 5단계에서는 실리콘 포토닉스 소자-전자소자 간 3차원 단일 집적 구성으로 진화한다는 점이다.

‘광집적화 기술 한계 극복: 실리콘 포토닉스 기반 광트랜시버 기술’에서 고밀도 집적화를 위한 패키지 분야 도전 기술은 다음과 같다.

첫째, 3차원 실리콘 관통 비아(TSV: Thru Silicon Via)[64,65]

둘째, 3차원 실리콘 인터포져/플랫폼(3D Silicon Interposer/Platform)[65-68]

셋째, 칩 레벨 본딩(Chip Level Bonding), 웨이퍼 레벨 본딩(Wafer Level Bonding)[69]

넷째, 포토닉 와이어 본딩(Photonic Wire Bonding)[70]

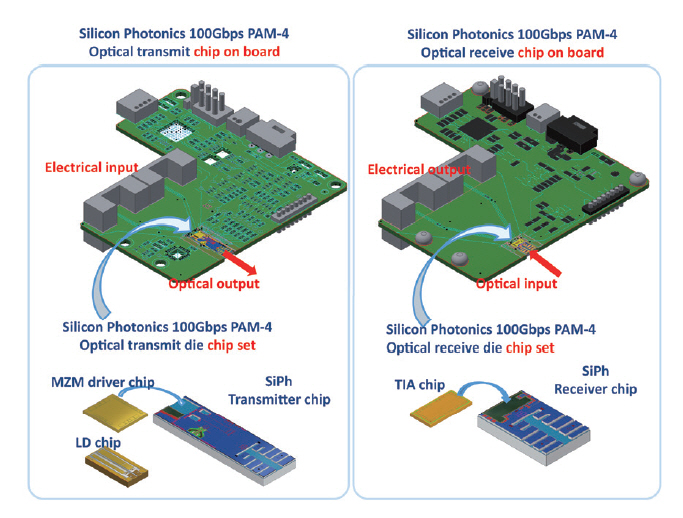

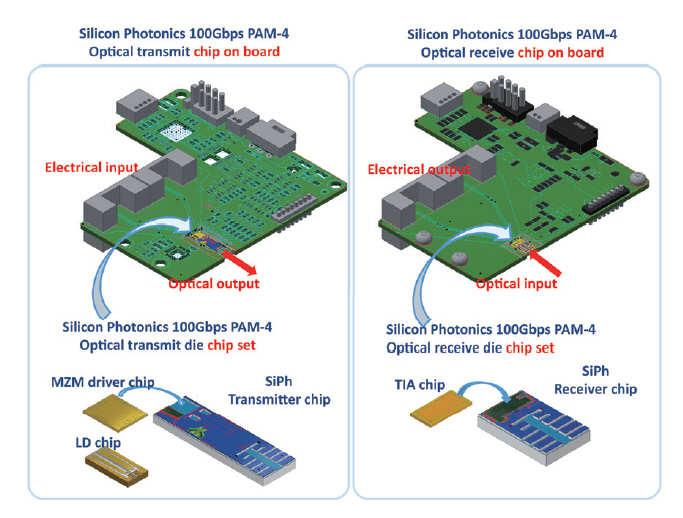

그림 3은 ETRI의 실리콘 포토닉스 100Gbps PAM-4 광송수신 칩온 보드 및 실리콘 포토닉스 광송수신 칩셋이다. 관통 비아 및 인터포져 기술을 적용한 광 시스템-인-패키지(OSIP: Optical System-In-Package) 형상 고도화를 위해서 3차원 실리콘 관통비아와 3차원 실리콘 인터포져/플랫폼에 관한 연구가 진행 중이다[65,68].

Ⅵ. 결론

실리콘 포토닉스 기술은 향후 테라비트 광전송을 위한 기반 기술로 활용될 것이며, 데이터 센터의 트래픽 처리/연결 용량 폭증, 스위치 대역폭 증가, 에너지, 공간, 비용 문제 등을 해결하기 위해 그 활용이 더욱 증가할 것으로 전망된다.

아울러, 고밀도 집적화 기반으로 소형화된 광학 패키지, 광학 엔진 및 광 트랜시버는 실리콘 포토닉스 기술과 융합되어 광 인터페이스 기술의 변혁을 이끌어 나가고 있다.

용어해설

Silicon Photonics 실리콘 포토닉스는 실리콘 집적회로와 CMOS 제조기술을 활용해 여러 개의 광소자를 하나의 칩으로 제작하는 기술로, 광부품의 대용량화, 소형화, 저전력화, 저가화를 가능하게 하는 기술이다. 실리콘 포토닉스는 빛으로 신호를 전달해 전기신호보다 훨씬 많은 데이터를 전달할 수 있으며, 자율주행 LiDAR, IoT/바이오 센서, 항공/우주 등 다양한 분야에 활용되고 있다.

약어 정리

ASIC

Application Specific Integrated Circuit

AWG

Arrayed Waveguide Grating

BCB

Benzocyclobutene

BGA

Ball Grid Array

CFP

100Gbps Form factor Pluggable

CMOS

Complementary Metal-Oxide Semiconductor

COB

Chip On Board

COBO

Consortium for On-Board Optics

CPO

Co-Packaged Optics

CWDM

Coarse Wavelength Division Multiplexing

DFB-LD

Distributed Feedback-Laser Diode

DR

Data center Range

DWDM

Dense Wavelength Division Multiplexing

EAM

Electro-Absorption Modulator

ELS

External Light Source

EPIC

Electronic-Photonics Integrated Circuit

FPCB

Flexible Printed Circuit Board

FR

Fiber Range

I/F

Interface

IoT

Internet of Things

IP

Internet Protocol

IQ

In-phase Quadrature

IQR

Inter-Quartile Range

LD

Laser Diode

LGA

Land Grid Array

LN

Lithium Niobate

LNOI

LN-On-Insulator

NPO

Near Package Optics

LiDAR

Light Detection And Ranging

MWIS

Multi-mode Waveguide Interconnect System

MZM

Mach-Zehnder Modulator

OFC

Optical Fiber Communication Conference and Exposition

OIF

Optical Internetworking Forum

OSA

Optical Sub-Assembly

OSIP

Optical System-In-Package

OSFP

Octal Small Form Factor Pluggable

OSFP-XD

Octal Small Form Factor Pluggable-eXtra Dense

PAM-4

Pulse Amplitude Modulation 4-level

PIC

Photonics Integrated Circuit

PIN

Positive-Intrinsic-Negative

QAM

Quadrature Amplitude Modulation

QCSE

Quantum Confined Stark Effect

QSFP-DD

Quad Small Form factor Pluggable-Double Density

RZ

Return-to-Zero

SerDes

Serializer/Deserializer

SFP

Small Form factor Pluggable

SiPh

Silicon Photonics

SOI

Silicon On Insulator

TE

Transverse Electric

TFLN

Thin-Film Lithium Niobate

TIA

Trans-Impedance Amplifier

TM

Transverse Magnetic

TSV

Thru Silicon Via

XFP

10Gbps Small Form factor Pluggable

F. Chang, "Optical interconnect technologies for datacenter networks," in Datacenter Connectivity Technologies: Principles and Practice, River Publishers, Gistrup, Denmark, 2018, pp. 1-32.

P. Maniotis et al., "Toward lower-diameter large-scale HPC and data center networks with co-packaged optics," J. Opt. Commun. Netw., vol. 13, no. 1, 2021, pp. 67-77.

S. Fathololoumi et al., "1.6 Tbps silicon photonics integrated circuit and 800Gbps photonic engine for switch co-packaging demonstration," J. Light. Technol., vol. 39, no. 4, 2021, pp. 1155-1161.

L. Ma, "Multimode polymer waveguides for high speed on board optical interconnects application," in Proc. COBO MWIS Ad Hoc Meeting, (San Francisco, CA, USA), Oct. 2021.

A. Liu et al., "A high-speed silicon optical modulator based on a metal-oxide-semiconductor capacitor," Nature, vol. 427, 2004, pp. 615-618.

S.Y. Siew et al., "Review of silicon photonics technology and platform development," J. Light. Technol., vol. 39, no. 13, 2021, pp. 4374-4389.

E. Timurdogan et al., "APSUNY process design kit (PDKv3.0): O, C and l band silicon photonics component libraries on 300mm wafers," in Proc. Opt. Fiber Commun., (San Diego, CA, USA), Mar. 2019, article no. Tu2A.1.

E. Timurdogan et al., "400G silicon photonics integrated circuit transceiver chipsets for CPO, OBO, and pluggable modules," in Proc. Opt. Fiber Commun., (San Diego, CA, USA), Mar. 2020, article no. T3H.2.

H. Yu et al., "800 Gbps fully integrated silicon photonics transmitter for data center applications," in Proc. Opt. Fiber Commun., (San Diego, CA, USA), Mar. 2022, article no. M2D.7.

M. Sakib et al., "A 240 Gb/s PAM4 silicon micro-ring optical modulator," in Proc. Opt. Fiber Commun., (San Diego, CA, USA), Mar. 2022, article no. M2D.4.

M. Traverso et al., "Integrated silicon photonics transceiver module for 100Gbit/s 20km transmission," in Proc. Opt. Fiber Commun., (San Francisco, CA, USA), June 2021, article no. M3A.3.

R. Meade et al., "TeraPHY: A high-density electronic-photonic chiplet for optical I/O from a multi-chip module," in Proc. Opt. Fiber Commun., (San Diego, CA, USA), Mar. 2019, article no. M4D.7.

M. Wade et al., "An error-free 1 Tbps WDM optical I/O chiplet and multi-wavelength multi-port laser," in Proc. Opt. Fiber Commun., (San Francisco, CA, USA), June 2021, article no. F3C.6.

Y. Bian et al., "Hybrid Ⅲ-Ⅴ laser integration on a monolithic silicon photonic platform," in Proc. Opt. Fiber Commun., (San Francisco, CA, USA), June 2021, article no. M5A.2.

R. Jones, "Overview and future challenges on Ⅲ-Ⅴ integration technologies in silicon photonics platform," in Proc. Opt. Fiber Commun., (San Francisco, CA, USA), June 2021, article no. M5A.1.

S. Amiralizadeh et al., "System optimization of high-efficiency 400 Gb/s PAM4 silicon photonics transmitter for data center applications," in Proc. Opt. Fiber Commun., (San Francisco, CA, USA), June 2021, article no. M3A.4.

E. Berikaa et al., "Net 1 Tbps/λ transmission over 80 km of SSMF using a single segment SiP IQM with all-electronic equalization," in Proc. Opt. Fiber Commun., (San Diego, CA, USA), Mar. 2022, article no. Th4A.5.

S. Fathololoumi et al., "1.6Tbps silicon photonics integrated circuit for co-packaged optical-IO switch applications," in Proc. Opt. Fiber Commun., (San Diego, CA, USA), Mar. 2020, article no. T3H.1.

D.A.B. Miller et al., "Band-edge electro-absorption in quantum well structures: The quantum-confined stark effect," Phys. Rev. Lett., vol. 53, no. 22, 1984, pp. 2173-2176.

S.A. Srinivasan et al., "60Gb/s waveguide-coupled O-band GeSi quantum-confined stark effect electroabsorption modulator," in Proc. Opt. Fiber Commun., (San Diego, CA, USA), Mar. 2022, article no. Tu1D.3.

P. Ying et al., "Low-loss edge-coupling thin-film lithium niobate modulator with an efficient phase shifter," Opt. Lett., vol. 46, no. 6, 2021, pp. 1478-1481.

S. Sun et al., "120 Gbps hybrid silicon and Lithium Niobate modulators with on-chip termination resistor," in Proc. Opt. Fiber Commun., (San Diego, CA, USA), Mar. 2020, article no. M2B.7.

M. Xu et al., "CMOS-level-voltage substrate-removed thin-film Lithium Niobate modulator," in Proc. Opt. Fiber Commun., (San Diego, CA, USA), Mar. 2022, article no. Th1J.3.

M. Sakib et al., "A 112 Gb/s all-silicon micro-ring photodetector for datacom applications," in Proc. Opt. Fiber Commun., (San Diego, CA, USA), Mar. 2020, article no. Th4A.2.

A. Chowdhury et al., "High performance avalanche photodiode in an monolithic silicon photonics technology," in Proc. Opt. Fiber Commun., (San Diego, CA, USA), Mar. 2022, article no. W3D.1.

H. Chen et al., "100-Gbps RZ data reception in 67-GHz Si-contacted Germanium waveguide p-i-n photodetectors," J. Light. Technol., vol. 35, no. 4, 2017, pp. 722-726.

S. Lischke et al., "Ge photodiode with -3 dB OE bandwidth of 110 GHz for PIC and ePIC platforms," in Proc. IEEE Int. Electron Devices Meeting (IEDM), (San Francisco, CA, USA), Dec. 2020, pp. 7.3.1-7.3.4.

서동준 외, "프린지 전계 강화를 위한 광검출기 도핑 구조 설계," in Proc. Photon. Conf., (Pyeongchang, Republic of Korea), Dec. 2021, article no. W1B-II.04, 2021.

D. Liu et al., "Silicon photonic filters," Microw. Opt. Technol. Lett., vol. 63, 2020, pp. 2252-2268.

C.K. Madsen and J.H. Zhao, Optical Filter Design and Analysis: A Signal Processing Approach, Wiley, New York, NY, USA, 1999.

T. Akiyama et al., "First demonstration of crosstalk-free (< -38.5 dB) 32-ch DWDM demultiplexer on standard Si PIC platform," in Proc. Opt. Fiber Commun., (San Diego, CA, USA), Mar. 2022, article no. Th4C.2.

K. Entesari, "Automated tuning for silicon photonic filters," in Proc. Opt. Fiber Commun., (San Diego, CA, USA), Mar. 2022, article no. Th1D.6.

J.Y. Lee et al., "Fabrication-tolerant nitride lattice filter for CWDM," in Proc. Opt. Fiber Commun., (San Francisco, CA, USA), June 2021, article no. Tu5B.2.

S.K. Selvaraja et al., "Subnanometer linewidth uniformity in silicon nanophotonic waveguide devices using CMOS fabrication technology," IEEE J. Sel. Top. Quantum Electron., vol. 16, no. 1, 2010, pp. 316-324.

D.J. Blumenthal et al., "Silicon nitride in silicon photonics," Proc. IEEE, vol. 106, no. 12, 2018, pp. 2209-2231.

P. Kaur et al., "Hybrid and heterogeneous photonic integration," APL Photon., vol. 6, no. 6, 2021, pp. 1-24.

X. Wang et al., "Athermal silicon arrayed waveguide grating with polymer-filled slot structure," Opt. Commun., vol. 282, no. 14, 2009, pp. 2841-2844.

D. Dai et al., "Mode/polarization manipulation in silicon photonics," J. Phys.: Conf. Ser., vol. 844, 2017, article no. 012039.

N. Margalit et al., "Perspective on the future of silicon photonics and electronics," Appl. Phys. Lett., vol. 118, no. 22, 2021, article no. 220501.

H.W. Rhee et al., "Direct optical wire bonding through open-to-air polymerization for silicon photonic chips," Opt. Lett., vol. 47, no. 3, 2022, pp. 714-717.

J.B. Driscoll et al., "First 400G 8-channel CWDM silicon photonic integrated transmitter," in Proc. IEEE Int. Conf. Group IV Photon. (GFP), (Cancun, Mexico), Aug. 2018.

D.W. Kim et al., "3D system-on-packaging using through silicon via on SOI for high-speed optical interconnections with silicon photonics devices for application of 400 Gbps and beyond," in Proc. Electron. Compon. Technol. Conf. (ECTC), (San Diego, CA, USA), June 2018. pp. 834-840.

H . Li et al., "A 3-D-integrated silicon photonic microring-based 112-Gb/s PAM-4 transmitter with nonlinear equalization and thermal control," IEEE J. Solid-State Circuits, vol. 56, no. 1, 2021, pp. 19-29.

W.S. Zhao et al., "High-frequency analysis of Cucarbon nanotube composite through-silicon via," IEEE Trans. Nanotechnol., vol. 15, no. 3, 2016, pp. 506-511.

이정찬 외, "고밀도 3D 집적 패키지 광모듈을 위한 인터포져비아 연구," in Proc. Photon. Conf., (Pyeongchang, Republic of Korea), Dec. 2021, article no. WP-I-.003.

L. Brusberg et al., "Glass interposer for high-density photonic packaging," in Proc. Opt. Fiber Commun., (San Diego, CA, USA), Mar. 2022, article no. Tu3A.3.

J.C. Lee et al., "A compact optics embedded optical receiver engine mounted on silicon interposer for 400G CWDM4 10km data center application," in Proc. Asia Commun. Photon. Conf., (Beijing, China), Oct. 2020, article no. T3G.3.

K. Sakuma et al., "Bonding technologies for chip level and wafer level 3D integration," in Proc. Electron. Compon. Technol. Conf. (ECTC), (Orlando, FL, USA), May 2014, pp. 647-654.

표 1 실리콘 포토닉스 기반 광트랜시버 주요 기술 동향

| Ref. | [60] | [61] | [11] | [5] | [62] | [14] | [12] | [63] |

|---|---|---|---|---|---|---|---|---|

| Affiliation | Intel Corp. | IME | Analog Photonics | Intel Corp. | Intel Corp. | CISCO | Intel Corp. | RANOVUS |

| Publish | IEEE 15th INTERNATIONAL CONFERENCE ON GROUP IV PHOTONICS 2018 | ECTC 2018 | OFC 2020 | J. LIGHTWAVE TECHNOLOGY 2020 | IEEE J. SOLID- STATE CIRCUITS 2021 | OFC 2021 | OFC 2022 | OFC 2022 |

| Data capacity | 400Gbps | 400Gbps | 400Gbps | 1.6Tbps, 800Gbps | 100Gbps | 100Gbps | 800Gbps | 800Gbps |

| Data rate per channel | 50Gbps | 100Gbps | 100Gbps | 100Gbps | 100Gbps | 100Gbps | 100Gbps | 100Gbps |

| Transmission length | - | 500m | 500m | 500m | - | 20km | 2km | - |

| Modulation format | NRZ | PAM-4 | PAM-4 | PAM-4 | PAM-4 | PAM-4 | PAM-4 | PAM-4 |

| Implementation level | Chip | CPO module | Chip | CPO module | Chip | QSFP28 module | Chip | CPO module |

| Integration approach | 2D | 2.5D | 3D | 3D | 3D | 3D | 2D | 3D |

표 2 광학 패키지 구성과 광학 엔진 및 광트랜시버의 단계별 기술 로드맵

- Sign Up

- 전자통신동향분석 이메일 전자저널 구독을 원하시는 경우 정확한 이메일 주소를 입력하시기 바랍니다.