양자 기술 구현을 위한 칩 제작 인프라 기술 동향

Trends in Chip Fabrication Infrastructure for Implementation in Quantum Technology

- 저자

-

김진우양자광학연구실 jk22@etri.re.kr 문기원양자광학연구실 kwmoon@etri.re.kr 주정진양자광학연구실 jjju@etri.re.kr

- 권호

- 38권 1호 (통권 200)

- 논문구분

- 국가 전략 산업을 위한 소재·부품 기술

- 페이지

- 9-16

- 발행일자

- 2023.02.01

- DOI

- 10.22648/ETRI.2023.J.380102

본 저작물은 공공누리 제4유형: 출처표시 + 상업적이용금지 + 변경금지 조건에 따라 이용할 수 있습니다.

본 저작물은 공공누리 제4유형: 출처표시 + 상업적이용금지 + 변경금지 조건에 따라 이용할 수 있습니다.- 초록

- In the rapidly growing field of quantum computing, it is evident that a robust supply chain is needed for commercialization or large-scale production of quantum chips. As a result, the success of many R&D projects worldwide relies on the development of quantum chip foundries. In this paper, a variety of quantum chip foundries, particularly the ones creating photonic integrated circuit (PIC) quantum chips, are reviewed and summarized to demonstrate current technological trends. Global projects aiming to establish new foundries, as well as information regarding their respective funding, are also included to identify the evolutionary direction of quantum computing infrastructure. Furthermore, the potential application of lithium niobate as a novel material platform for quantum chips is also discussed.

Share

Ⅰ. 서론

양자 컴퓨팅은 빠르게 성장하는 분야이며, 양자 역학의 기반으로 고전 컴퓨터보다 특정 문제를 기하 급수적으로 빠르게 해결할 수 있다. 양자 칩은 양자컴퓨터의 프로세서이고, 큐비트(Qubit)를 이용한다. 큐비트는 고전 컴퓨터의 비트(Bit)와 달리 0, 1, 그리고 0과 1을 둘 다 동시에 나타날 수 있는 중첩 상태(Superposition)를 취할 수 있다. 따라서, 양자 칩은 이 중첩 상태를 이용해서 한 번에 여러 작업을 동시에 수행할 수 있는 장점이 있다. 또 하나의 장점은 양자 얽힘 상태(Entanglement)이다. 양자적으로 얽힌 상태는 2큐비트의 매우 강한 상관관계를 의미하며, 큐비트 하나에 작업을 하면 같이 얽힌 큐비트도 아무리 멀리 있어도 동시에 작업이 될 수 있다. 그러므로 얽힌 상태의 성질을 이용해서 양자 컴퓨팅의 프로세싱 속도를 매우 증가시킬 수도 있다. 양자 알고리즘과 함께 활용되는 경우에는 사이버 보안, 제약 연구, 경제학 모델링 등 다양한 산업에 적용될 수도 있다.

양자 컴퓨팅 분야의 발달과 함께 현재 전 세계적으로 양자 칩 개발에 많은 투자가 이루어지고 있다. 유럽의 경우, 유럽 위원회(European Commission)에서는 최근에 Quantum Flagship이라는 계획을 수립하고 10년간 10억 유로를 투자하려고 한다[1]. 특히 공급망 강화를 위해서 양자 칩 제조 공정에 투자를 집중한다는 내용도 있다. 양자칩의 경우, 반도체 기반으로 만든 경우가 많아, 반도체 제조 공장, 또는 “파운드리(Foundry)”에서 개발되는 칩이 많고, 따라서 반도체 공장에도 양자 기술 발달을 위해 많은 투자가 이루어지고 있다. 예를 들면, 최근 2022년 7월에 미국에서 “CHIPS and Science Act”라는 법안이 통과되었으며, 200억 달러를 투자해서 미국에 있는 제조 능력을 키우려고 노력하고 있고, 개발 예정 분야에 양자 칩 제조 및 파운드리 개발이 포함되어 있다[2,3].

본고에서는 현재 해외에서 개발되어 있거나 개발되고 있는 양자 칩 제조 파운드리 및 제조 서비스를 소개한다. 또한, 진행되고 있는 주요 프로젝트도 같이 소개함으로써 현재 양자 칩 개발 기술의 동향을 논의하고자 한다. 양자 칩은 소재의 물리적인 특성에 따라 많이 다를 수 있고, 다양한 형태로 양자 컴퓨팅 기술이 발달하고 있지만, 본고에서는 photonic integrated circuit(PIC), 또는 광집적회로 양자 칩과 초전도 양자 칩에 집중하여 논의하고자 한다.

Ⅱ. PIC 파운드리

Photonic integrated circuits(PIC), 또는 광집적회로는 큐비트를 광학적으로 인코딩하여 전송하거나, 한 칩에서 처리할 수 있는 능력을 갖추고 있다. 실험실용 벌크 광학 기기를 이용해서 광학 큐비트의 인코딩이 가능하다는 점이 발견된 이후, 광집적회로를 활용하는 연구가 양자 칩의 제조 가능성, 효율성 및 견고성을 매우 향상시킬 수 있는 분야가 되었다[4,5].

1. Ligentec

Ligentec은 2016년 스위스의 Federal Institute of Technology in Lausane에서 spin-off를 통해 설립되어, Kippenberg 교수의 silicon nitride(Si3N4) 기술 기반으로 광집적회로 integrated foundry 서비스를 제공하는 B2B 회사이다. 다양한 응용 분야를 지원하고 있고, 그중 한 분야가 양자 기술 개발이다. 파운드리 서비스 분야에서는 MPW로 7~20칩, 또는 커스텀 프로토타입으로 최소 50칩, 그리고 대량 생산을 위해 최소 10,000칩 제조를 제공하고 있다.

Ligentec은 Mach Zehnder Interferometer(MZI), phase shifters, 튜너블 링 공진기, 또는 모드 일치를 위한 spot size converter 등 다양한 디자인을 제공하고 있다. 표 1[6]에 Ligentec이 제공하는 Si3N4칩 성능을 표시하였다.

표 1 LIGENTEC이 제공하는 SiN 칩 성능

| 항목 | 성능 |

|---|---|

| Bending loss, 50μm radius | 최대 0.005dB |

| 전파 손실 | 최대 0.1dB/cm |

| Minimum feature size | 최소 200nm |

| Insertion loss | 최대 5dB/m |

| MZI(Rejection) | 최소 22dB |

| 공진기 Q factor | 2 × 106 |

| Fiber-chip coupling loss | 최대 1.5dB |

이 회사는 유럽 연합(EU)의 Horizon 2020 연구 및 혁신 프로그램을 통해 지원받고 있다. European Space Agency, National Centre of Competence in Research’s Quantum Science and Technology in Switzerland 등 다수의 기관을 통해 펀딩을 받고 있고, X-FAB, VLC PHOTONICS, VPI PHOTONICS, MENTOR, LUDEDA, SYNOPSYS, LUMERICAL 등 다수의 유럽 기반 파운드리 사업자와 파트너십을 맺고 있다.

2. Lionix

Lionix는 네덜란드에서 2001년에 설립되어, silicon nitride(Si3N4) 기반 광집적회로 및 micro electromechanical systems(MEMS)의 파운드리 서비스를 다양한 응용 분야(통신, 생명과학, metrology, 양자 기술 등)에서 제공하는 회사이다. 파운드리 서비스는 작은 규모인 MPW부터 대용량까지 능력이 있고, MPW는 1,550nm, 850nm, 그리고 가시광선 파장의 Si3N4 광집적회로를 제공하고 있다. 광집적회로 설계, 시뮬레이션, 어셈블리, 그리고 소프트웨어 개발 서비스도 제공하고 있다[7].

QuScale, REAP, SensorChip, 5G-PHOS, i-gene, PICWeld, SpaceBeam, TERAWAY 등 다수의 R&D 과제에도 참여하고 있다.

3. VLC Photonics

VLC Photonics는 2011년에 Telecommunications and Multimedia Applications Institute of Universitat Politecnica de Valencia에서 spin-off로 설립된 스페인 회사이다. VLC Photonics는 턴키 광집적회로 솔루션을 제공하는 fabless foundry이다. PIC 컨설팅, 설계, packaging, 측정, foundry process design kits (PDK) 등 서비스를 제공하며, 다른 20개 해외 파운드리와 같이 협력해서 다양한 플랫폼의(Indium Phosphide(InP), Gallium Arsenide(GaAs), Silicon based Platforms, Iithium Niobate(LiNbO3) 등 포함) 광집적회로를 +20/100/1000 칩 단위, 아니면 MPW로 생성한다. 광집적회로 플랫폼에 대한 진입 장벽을 낮추기 위한 교육 프로그램도 제공하고 있다[8].

VLC Photonics는 현재 EU의 Horizon 2020 프로그램을 통해 다수의 과제를 수행하고 있으며, 과거에 optical code-division multiple-access(OCDMA) (Lionix와 공동연구), frequency discrimination photoreceiver PICs(Fraunhofer HHI, europic과 공동연구), 그리고 통신용 radio frequency(RF) 기기 및 PIC 광섭계를 만든 실적이 있다.

4. nanoPHAB

nanoPHAB은 2015년에 네덜란드에서 설립된 회사이며, Eindhoven University of Technology의 COBRA Institute에서 spin-off로 설립된 회사이다. nanoPHAB는 다양한 플랫폼(Si 기반 플랫폼, Ⅲ-V 반도체, 금속, 고분자 등)의 파운드리 서비스를 제공하고, 특히 광학 응용 분야에 활용될 수 있는 소재를 다룬다. 800~1,650nm 파장용 Ⅲ-V nano-heterostructure의 epitaxial growth, thin film deposition, 5nm 이하의 해상도를 다루는 electron beam lithography, plasma etching 등 서비스도 제공한다[9].

5. Teem Photonics

Teem Photonics는 1998년에 프랑스에서 설립되었고, glass 기반 광집적회로 파운드리를 운영한다. 레이저, Waveguide array-to-fiber transposers, custom circuits, packaging, assembly 등 서비스 및 제품도 제공한다. 표 2[10]에 Teem Photonics가 제공하는 칩의 성능을 표시하였다.

6. PHIX

PHIX는 네덜란드에서 2018년에 설립된 PIC 파운드리 회사이다. 이 파운드리는 특히 packaging과 assembly 파운드리 서비스를 제공하고, 통신, LIDAR, 의료 기기, 그리고 양자 분야를 위한 PIC의 개발에 집중한다. 소규모인 prototype의 packaging부터 대규모인 volume packaging 서비스를 제공하고, PIC 주요 플랫폼(Si, Si3N4, InP 등)을 모두 지원한다. 추가적인 서비스로 contract manufacturing이라는 계약을 통해 PIC의 module로 outsourcing을 할 수 있고, dicing, polishing, assembly 등 다양한 서비스를 지원한다[11].

7. QUIX

QUIX는 2019년에 네덜란드에 설립된 fabless PIC 파운드리로, Lionix와 PHIX회사 등과 협력해서 양자 컴퓨팅 분야에 특히 활용될 수 있는 PIC solution을 제공한다. 이 회사는 silicon nitride 기반 소재를 이용하고, 양자 칩부터 통합된 양자 컴퓨터까지 판매하며, 양자 통신(양자 키 분배 등) 또는 양자 센싱에 적용될 수 있는 custom solution도 제공하는데, Lionix 회사가 개발한 TriPleX 플랫폼 기반으로 제공한다.

8. National Quantum Fabless Foundry (NQFF)

NQFF는 현재 싱가포르에서 성장하고 있는 fabless foundry이다. 50개 연구기관(Institute of Micro Electronics, Institute of Materials Research and Engineering, Centre for Quantum Technologies 등)과 공동연구를 하며 양자 컴퓨팅, 양자 통신, 그리고 양자 센싱 분야의 양자 기기를 개발하고 있다. 특히, 초전도 큐비트, PIC, 그리고 silicon donor spin qubit을 주로 연구하고 있으며, 싱가포르의 Agency for Science, Technology and Research(또는 A*STAR)와 Quantum Engineering Programme 에서 펀딩을 받고 있다[12].

Ⅲ. 다른 형태의 양자 칩 파운드리

1. SEEQC

SEEQC는 HYPRES라는 회사에서 spin-off로 만들어진 미국 회사이고, 초전도 칩 파운드리를 운영한다. 5,000종의 초전도 칩 설계 실적이 있으며, 상업, 학술, 또는 정부 시장을 위한 모든 초전도 칩을 생산하고 지원할 수 있다고 한다. 파운드리의 주요 서비스는 설계, 개발, 시뮬레이션, fabrication, 그리고 측정이다. MPW나 dedicated wafer run 둘 다 가능하다[13].

SEEQC는 Digital quantum management(DQM) System-on-a-chip™이라는 제품도 판매하는데, 이 제품은 양자 칩이며, error correction을 포함해서 큐비트의 모든 제어 기능을 가지고 있다.

2. Qnami

Qnami는 2016년에 University of Basel의 Patrick Malentinsky 교수의 연구에 따라 설립된 스위스 회사다. 이 회사는 다이아몬드의 nitrogen vacancy(NV) centers를 사용해서 양자 시스템을 구현하고, NV 다이아몬드를 양자 센싱 분야에 최초로 상업화했다. 양자 센싱 분야를 위해 파운드리도 운영하고 있다. Plasma-assisted chemical deposition이라는 과정을 통해 인공 다이아몬드를 만들고, 다양한 기술을 이용해서 표준 solution이나 custom solution을 소규모 실험이나 대규모 제조까지 양자 센서를 제공한다.

Qnami는 ProteusQ™라는 통합 양자 현미경 시스템도 제공한다. 이 현미경 시스템은 원자 규모(nm 스케일)의 자성체 분석을 위한 NV 다이아몬드 현미경이고, 구동하는 소프트웨어와 함께 제공되어 있다. 작업도 자동화되어 있어 운영자가 양자 전문 지식이 많지 않아도 운영이 가능하게 되어있다. 표 3[14]에 Qnami가 제공하는 칩의 성능을 표시하였다.

표 3 Qnami가 제공하는 성능

Ⅳ. Lithium Niobate

새로운 물질 기반으로 만든 PIC를 양자 칩으로 만들 가능성에 대한 연구가 많이 이루어지고 있다. 특히 lithium niobate(LiNbO3 또는 LN)이 양자 분야에서 많은 관심을 받고 있다.

LN은 electro-optic coefficient가 매우 높아서 몇십 년 전부터 electro-optic modulator로 사용됐지만, 최근에 Smart-Cut이라는 기술의 개발 덕분에 lithium niobate on insulator(LNOI)의 thin film 기술이 발전하고 산업화되면서 양자 칩 개발 가능성이 열렸다[15].

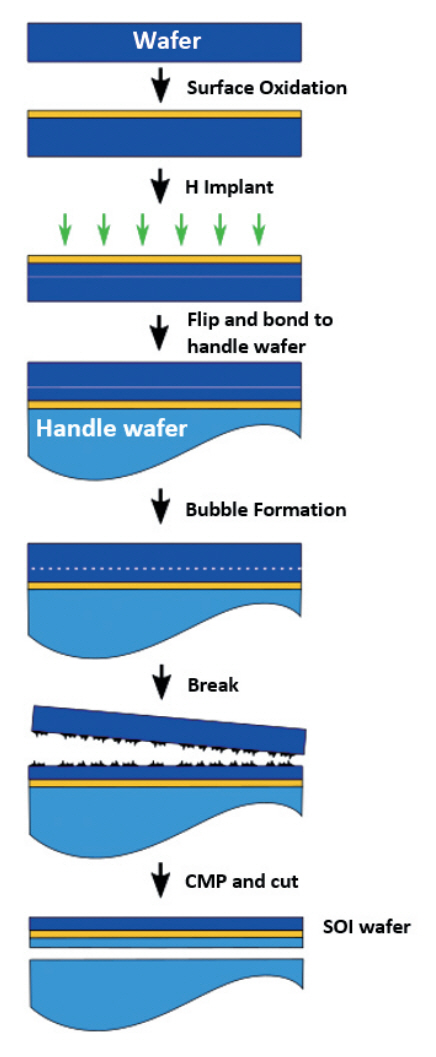

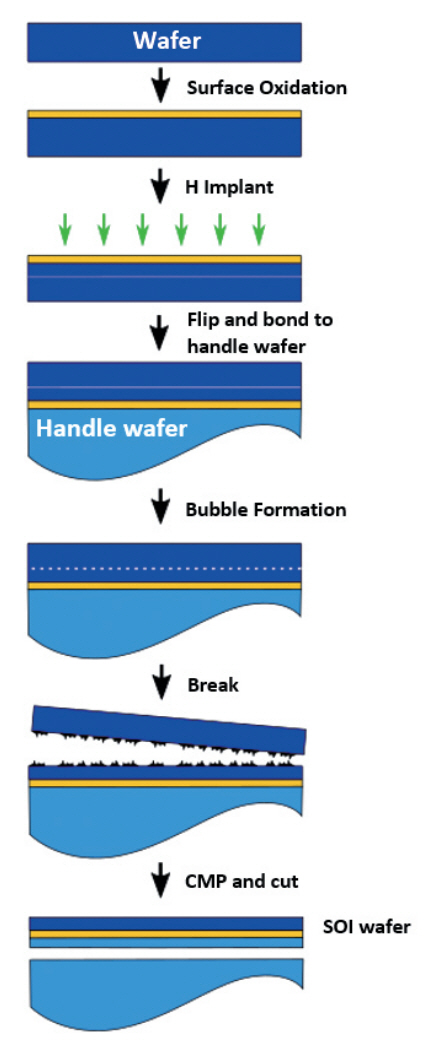

그림 1에 나타낸 바와 같이, Smart-Cut이라는 과정에서는 LN wafer에 ion implantation을 하고, implant 없는 면에서 SiO2 wafer와 같이 bonding한다. 마지막으로 열을 가해 bulk LN은 분리해서 다시 쓸 수가 있고, chemical mechanical polishing(CMP) 작업을 하면 SiO2에 남아 붙은 LN은 thin film 형태이다[16,17].

높은 electro-optic coefficient 덕분에 물질이 매우 non-linear하며, 광자가 LN 물질을 통해 spontaneous parametric down conversion(SPDC)이라는 과정을 통해 얽힌 상태가 될 수도 있고, 높은 상대 굴절률 덕분에 PIC를 만들 때 더 작게 만들 수가 있다는 장점이 있다[18]. 이렇게, 양자 칩 개발에 중요한 물질인 LNOI 제품을 판매하는 회사와 LNOI 기술을 소개한다.

1. Partow Technologies

Partow Technologies는 2012년에 University of Central Florida에서 spin-out으로 설립된 미국 회사이다. Partow Technologies에서 제공하는 주요 제품은 LNOI thin film이고, 특히 ion slicing(Smart-Cut) 방법을 사용해서 LNOI thin film을 만들어서 판매한다. 다른 wafer bonding 서비스도 제공하며, 반드시 LN만으로 wafer bonding 작업을 할 수 있는 것은 아니고, 다른 물질의 wafer도 서비스를 지원한다. MZ modulator, Micro-ring modulator, Acousto-optic filter, SHG integrated device, Acousto-optic Beam-steering device, Transducer, Lithium Niobate integrated photonics, MEMS resonator and RF filters, Pyroelectric detectors 등 소재도 LNOI를 활용해서 만드는 것을 현재 연구 중이다. 표 4에 Partow Technologies가 제공하는 LNOI의 성능을 표시하였다.

2. NanoLN

NanoLN은 2010년에 설립된 중국 회사이며, LN thin film wafer와 lithium tantalite thin film wafer(Surface Acoustic Wave 연구용)를 판매한다. Partow Technologies와 비슷하게 Smart-Cut 기술을 활용해서 thin film을 제조하고 판매한다. Ion implantation, wafer bonding, polishing, dicing 등 서비스도 제공하며, 원하면 다른 물체 wafer와도 Smart-Cut 기술을 이용해서 thin-film을 만드는 서비스도 지원한다[19]. 표 5에 Qnami가 제공하는 칩의 성능을 표시하였다.

3. Project ELENA

Project ELENA, 또는 “European electro-optic and nonlinear PIC platform based on lithium niobate”는 유럽에서 2022년 1월 1일에 시작한 프로젝트이며, 3년 동안 500만 유로가 투자된다. 이 과제는 특히 LN 플랫폼으로 PIC를 만드는 것을 연구하고 있고, 유럽에 공급망을 강화하면서 LN PIC 파운드리를 만드는 것이 목적이다. 이 과제도 다른 유럽 기반 PIC 파운드리와 같이 2020 Horizon programme에서 펀딩받고 있다. ELENA를 운영하는 협회의 주요 회사는 CSEM, VPI Photonics, Ⅲ-V Lab, Soitec, ETH Zurich, Vanguard automation, Thales, Rosenberger, L-up SAS, 그리고 CEA-LETI이다[20].

Ⅴ. 결론

양자 칩은 빨리 성장하는 분야이지만, 양자 칩을 대량으로 생성할 수 있게 만드는 파운드리에 대한 정보는 아직 많이 알려져 있지 않다. Fabrication과 fabless 파운드리 중 다양한 서비스를 제공하는 파운드리가 있으며, 소규모로 prototype을 만들며 측정하는 업체이거나, 대규모로 양자 칩을 개발하고 판매를 하거나 양자 칩의 산업화를 더 빨리 진행될 수 있게 큰 도움을 주고 있다.

Quantum Flagship이나 Project ELENA와 같이, 유럽에서 양자 칩 분야가 많은 투자를 받고 있다. 미국에서도 최근 CHIPS and Science Act로 인해 많은 자금이 투자되고 있어 관심이 쏠리고 있지만, 아직 개발된 파운드리 정보는 많이 공개되어 있지 않다. 그러나 기술이 발달 되며 다양한 형태의 파운드리가 나타날 것이며, 인프라의 발전을 통해 양자 칩의 산업화에 많은 도움이 될 것이다.

용어해설

Multi Project Wafer(MPW) 서비스는 한 고객이 다른 고객들과 wafer 하나를 같이 나눠서 사용할 수 있는 서비스이며, 규모가 작은 프로젝트나 프로토타입을 개발하는 데 진입 장벽을 줄일 수 있음[21]

Fabless Foundry Fabless 파운드리는 한 소재의 플랫폼으로 제한되지 않고, 설계 과정을 더 자유롭게 진행이 될 수 있게 만들고, 실제의 제조는 외부 회사를 통해 outsourcing해서 실행됨[22]

Packaging PIC에서 packaging이라는 것은 레이저, 측정기, modulator, beam-splitter 등 다양한 부품을 하나의 칩으로 통합하는 작업. Packaging 전에는 PIC 자체로 활용은 어려우며, 보호하는 enclosure에 넣어 외부 광섬유와 잘 연결할 수 있게 하는 작업

Process Design Kit PDK는 파운드리가 fabrication 과정에서 사용하는 파일을 의미함. PIC 설계자가 PDK를 사용해서 고객이 원하는 요소로 더 쉽게 만들 수 있게 도와주고 칩 개발의 진입 장벽을 낮춤[23]

약어 정리

S. Tanzilli et al., "On the genesis and evolution of Integrated Quantum Optics," Laser Photonics Rev., vol. 6, no. 1, 2012, pp. 115-143, Ostrowsky DB (2012-01-02).

G. Moody et al., "2022 Roadmap on integrated quantum photonics," J. Phys.: Photonics, vol. 4, no. 1, 2022, doi: 10.1088/2515-7647/ac1ef4.

G. Chen et al., "Advances in lithium niobate photonics: Development status and perspectives," Adv. Photonics, vol. 4, no. 3, 2022, article no. 034003.

M . Bruel, "Process for the production o f thin semiconductor material films," US 5374564, Dec. 20, 1994.

Cyferz, "Smart Cut Process," Wikipedia, Aug. 18, 2007, https://en.wikipedia.org/wiki/Smart_cut#/media/File:Smart_Cut_SOI_Wafer_Manufacturing_Schema.svg

M.-C. Wu and R.-B. Lin, "Multiple project wafers for medium-volume IC production," in Proc. IEEE Int. Symp. Circuits Syst. (ISCAS), (Kobe, Japan), May 2005, pp. 4725-4728.

P. Munoz et al., "Evolution of fabless generic photonic integration," in Proc. Int. Conf. Transparent Opt. Netw., (Cartagena, Spain), June 2013, pp. 1-3.

표 1 LIGENTEC이 제공하는 SiN 칩 성능

| 항목 | 성능 |

|---|---|

| Bending loss, 50μm radius | 최대 0.005dB |

| 전파 손실 | 최대 0.1dB/cm |

| Minimum feature size | 최소 200nm |

| Insertion loss | 최대 5dB/m |

| MZI(Rejection) | 최소 22dB |

| 공진기 Q factor | 2 × 106 |

| Fiber-chip coupling loss | 최대 1.5dB |

출처 Reproduced from [6].

표 2 Teem Photonics가 제공하는 칩 성능

| 접근방법 | 연구방법 |

|---|---|

| 전파 손실 | 최대 0.15dB/cm |

| Bending radius | 최대 1mm |

| SMF fiber coupling loss | 최대 0.2dB |

| Polarization dependent loss | 최대 0.1dB |

| 동작 밴드 | 400~2,000nm |

출처 Reproduced from [10].

표 3 Qnami가 제공하는 성능

출처 Reproduced from [14].

표 4 Partow Technology가 제공하는 LNOI의 spec

| 항목 | 성능 |

|---|---|

| 크기 | 100mm 또는 요청 시(75~100mm 지름) |

| 두께 | LN: 600nm(또는 요청 시 300~1,200nm) |

| SiO2: 1mm(또는 요청 시 0.5~1mm) | |

| Crystal orientation | X Cut |

| 두께 uniformity | 최대 3% |

| 표면 거칠기 | 최대 1nm |

| Si 비저항 | 최소 5,000ohm cm, 요청 시 0~20,000ohm cm |

출처 Reproduced from [18].

표 5 NanoLN이 제공하는 LNOI의 spec

| 항목 | 성능 |

|---|---|

| 크기 | 3~6inch 지름 |

| 두께 | 300~900nm |

| Crystal Orientation | X, Y, Z |

출처 Reproduced from [19].

- Sign Up

- 전자통신동향분석 이메일 전자저널 구독을 원하시는 경우 정확한 이메일 주소를 입력하시기 바랍니다.