배성범 (Bae S.B.)

Ⅰ. 서론

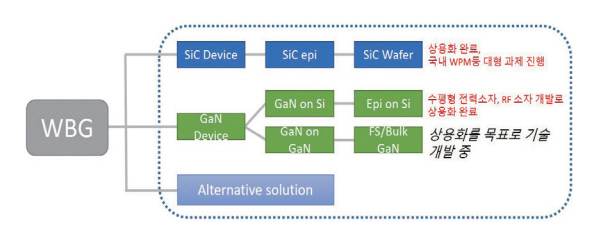

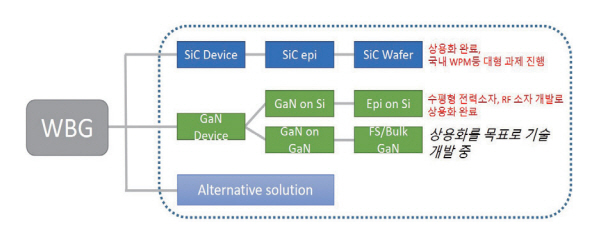

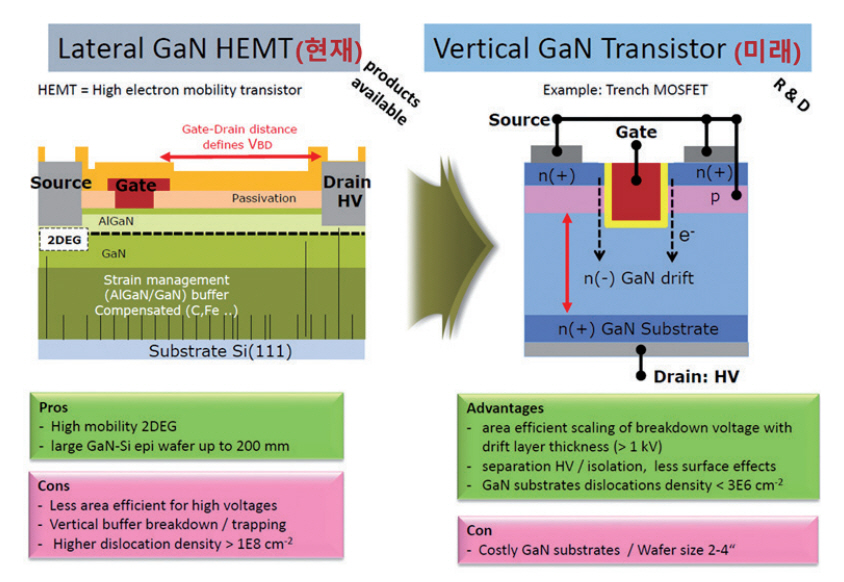

최근 글로벌 에너지 위기, 환경 및 기후변화 문제의 심각성을 인식하고 이를 해결하기 위해 2050년까지 탄소 순 배출량이 0이 되는 탄소중립 사회로의 전환을 선언하는 ‘2050 탄소중립 목표 기후동맹’이 전 세계의 화두가 되었다. 우리 정부에서도 2030년까지 국가 온실가스감축목표(NDC)를 2018년 대비 40%로 상향하는 기후 위기 대응을 위한 「탄소 중립·녹색 성장 기본법 시행령」 안을 2022년 3월부터 시행하여 2050 탄소중립 비전을 법제화한 14번째 국가가 되었다[1]. 탄소중립을 실현하기 위해서는 신재생 에너지의 발전량 확대와 같은 에너지 분야의 대응이 필요하며, 특히 최종 에너지원인 전기 에너지의 고효율화가 중요하다. 2021년 미국에서 소비된 에너지(2021 U.S. Energy Consumption Flow)를 보면 전기에너지로 변환되어 소비되는 비율이 약 37%(36.6 Quadrillion BTU)로 탄소중립을 위해 신재생 에너지의 활용 및 고효율의 전력변환 장치의 사용을 늘려가고 있다[2]. 운송 및 교통수단에 들어가는 에너지 대부분은 석유 형태로 되어 있지만, 내연 기관의 경우 약 20% 정도의 저효율로 대부분 열로 에너지 발생시키기 때문에 탄소중립을 위해서는 에너지 변환 효율이 높은 전기차(EV)의 전환이 필요하다. 글로벌 전기차 증가율은 약 30%로, 2030년까지 도로 차량의 약 7%를 전기차가 차지할 것으로 전망되고 있다[3]. 글로벌 전기차 업체들은 전기차 시장의 주도권을 잡기 위해 긴 주행거리 확보를 위한 경쟁이 격화되고 있다. 그림 1처럼 차체의 경량화, 고전압 배터리, 배터리 기술의 향상, 고효율 전력변환 장치, 경량의 고효율 AC모터 등과 같은 기술들이 적용되어 주행거리 확보를 위한 기술적 경쟁이 진행되고 있다[4]. 전력변환장치는 전기에너지를 시스템이 필요로 하는 형태로 변환, 제어, 처리 및 공급하는 것으로, 전자기기의 에너지 효율을 얼마나 높일 수 있는지가 전력반도체에 의해 좌우되기 때문에 고효율 전력반도체의 사용을 통해 전력변환 장치의 효율 향상이 가능하다. 현재 전기차용 전력 반도체는 Si 반도체가 주로 사용이 되지만, Si의 물성적 한계로 인해 고전압, 고전류 및 경량화 특성을 만족시키는 SiC, GaN과 같은 넓은 에너지 밴드 폭(WBG: Wide Band Gap) 반도체를 기반으로 하는 전력 소자의 사용이 점차 늘고 있다. 그림 2는 WBG 반도체의 분류 및 기술개발 동향을 나타낸다. WBG 반도체에서 GaN 전력반도체는 고속 스위칭, 저손실 및 고효율 반도체의 특징으로 차세대 전기차용 전력반도체로 많은 주목을 받고 있다. 표 1은 전력소자용 반도체 소재별 물성 특성을 나타낸다[5]. GaN 전력반도체는 HEMT 구조의 수평형 전력 소자가 먼저 상용화되어 최근 여러 응용분야에 활용되고 있다. 이종 기판에 성장된 GaN 에피 웨이퍼를 이용하기 때문에 수평형 소자 구조로 개발되었다. 전류 용량과 항복전압을 높이기 위해서는 칩 크기를 늘려야 하므로 항복전압 특성이 ~600V인 소자로 상용화되었으며, 중소형 스위칭 컨버터 등에 적합해서 ~100W급의 모바일 충전기에 많이 탑재되고 있다. 수직형 GaN 전력반도체는 Si과 SiC 전력반도체와 유사한 소자 구조적 특징을 가지고 있다. 수직형 GaN 전력 소자는 벌크(Bulk) GaN 단결정 기판 위에 GaN 에피 성장을 통해 제작하기 때문에 이종 기판을 이용한 수평형 GaN 전력 소자보다 결정 결함이 낮아서 높은 항복전압에 유리하며, 소자의 크기가 수평형 소자보다 상대적으로 작다는 장점이 있다. 최근 일본, 미국, 유럽 등 선진국을 중심으로 많은 연구가 진행되고 있다.

본 논문에서는 전기차 응용이 가능한 고전압 수직형 GaN 전력반도체에 대해 살펴보고자 한다. 이를 위하여 수직형 GaN 전력반도체의 기반이 되는 GaN 단결정 기판소재에 대해 간략하게 살펴보고, 다양한 GaN 수직형 소자 기술에 대한 국내외 기술 동향을 알아본다.

표 1 전력소자용 반도체 소재의 특성 비교

| Property | Si | 4H-SiC | GaN |

|---|---|---|---|

| Band GaP (eV) | 1.1 | 3.2 | 3.4 |

| Electric Field (MV/cm) | 0,3 | 3 | 3.3 |

| Saturation Drift Velocity (Mcm/s) | 10 | 20 | 25 |

| Thermal Conductivity (W/cmK) | 1.5 | 4.9 | 1.3 |

Ⅱ. 전기차 응용을 위한 수직형 GaN 전력반도체 기술

1. GaN 단결정 기판 기술

GaN 반도체는 광소자 및 전자소자용 소재로 주목받기 시작하면서 단결정 기판에 관한 연구가 활발하게 진행되었지만, GaN 반도체가 갖는 특이성인 2,000℃ 이상의 높은 융점과 6GPa 이상의 질소의 분해압[6] 때문에 실리콘 기판과 같은 Czochralski법 또는 Bridgman법으로는 제작이 어려운 점이 있다.

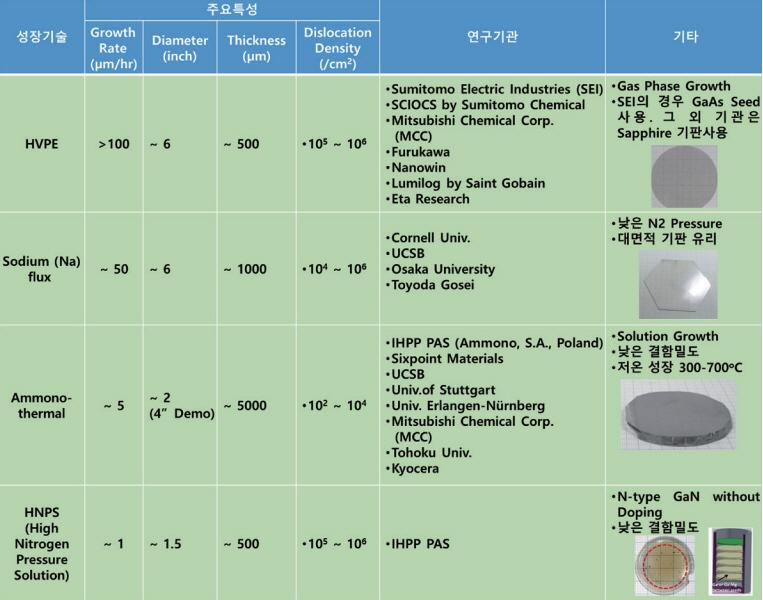

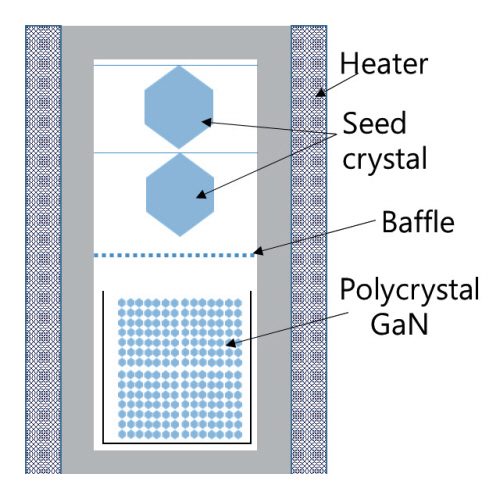

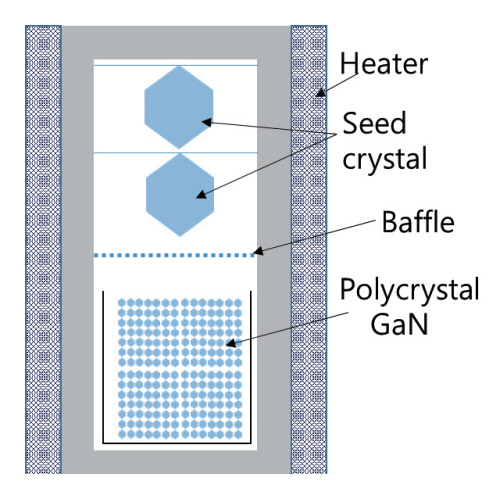

현재 GaN 단결정 기판을 제작하는 방법으로 벌크 형태의 기판을 제작하는 고온고압 용융법(Ammono-thermal), 승화법(Sublimation) 및 Na flux법 등이 있으며, GaN 후막(Thick Film) 형태의 기판을 제작하는 HVPE(Hydride Vapor Phase Epitaxy) 성장법이 대표적인 방법에 해당한다[7]. 표 2에서는 GaN 단결정 성장 방법에 대한 특징을 비교하였다[8-11]. 대표적인 저결함 GaN 단결정 기판 제작법인 Ammono-thermal 법은 낮은 결함 밀도, 간단한 장치 구조 및 성장온도의 장점이 있으나, 성장 속도가 느린 단점으로 상용화에 어려움이 있다. 1995년 Dwilinski가 Ammono-thermal 법을 이용한 GaN 단결정 성장을 시작하였으며[8], 이후 Ehrentraut에 의하여 성장 속도가 향상된 장비 구조가 제안되어[9] 현재 Ammono社에서 2인치 기판 상용화가 되었고, 4인치 기판 데모를 진행 중이다[10]. 국내에는 한국화학연구원에서 GaN 단결정 기판 개발을 위한 Ammono-thermal 장치와 성장 기술에 대한 기초 연구를 진행하였다[11]. 그림 3은 Ammono-thermal 성장법의 장치를 나타낸다.

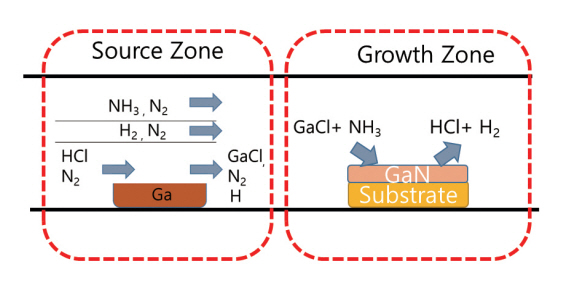

현재 GaN 단결정 기판 상용화에 가장 앞선 기술은 HVPE 성장법은 1970년대에 개발된 방법으로 초기에는 GaN 에피성장에 사용되었으나 현재 MOCVD 성장법으로 대체되었으며, 최근 GaN 단결정 기판 성장에 활용되면서 다시 활발하게 연구가 진행되고 있다. 그림 4와 같이 HVPE 성장법은 용융된 Ga 금속을 염산(HCl) 기체를 이용하여 이동하게 한 후 5족인 암모니아(NH3) 가스와 함께 가열된 GaN 기판 위로 이송하여 기상 반응에 의해 GaN 단결정을 성장하는 방법이다[12].

1999년 ATMI(美)가 HVPE법으로 사파이어 기판 위에 GaN 후막을 성장한 이후 레이저 분리법으로 GaN 단결정 기판을 발표하였다. 이후 일본 기업을 중심으로 상용화가 진행되었으며, 2003년 Sumitomo Electric(日)에서 GaAs 기판을 이용한 GaN 기판을 제작하였으며, Hitachi Cable(日)은 Ti-메탈 코팅을 적용한 VAS(Void Assisted Separation) 공정을 이용하여 자가 분리(Self Separation)에 의한 기판 제작에 성공하였다. Sumitomo Electric은 ELO(Epitaxial Lateral Overgrowth) 공정을 두 번 적용하는 자가 분리 공법을 개발하였다. 미국은 드미트리 박사(Dr. Dimitrie)가 1997년 설립한 TDI社를 중심으로 HVPE GaN 성장 기술을 주도해 오고 있으며, 현재 Kyma社에서 GaN 단결정 기판 및 template 제품들을 출시하고 있다. 국내에서는 1998년 삼성종합기술원에서 연구를 시작하여 2000년 기술개발을 완료하고 삼성코닝을 통한 사업화를 진행하였으며, 2005년 2인치급, 2011년 4인치급 GaN 기판개발을 완료하였으나 후속 사업화를 중단하였다. 이후 벤처기업(루미지엔텍, 루미스탈, 비투지 등)에서 현재까지 GaN 기판개발을 진행하고 있다[13].

2. 수직형 GaN 전력반도체 기술

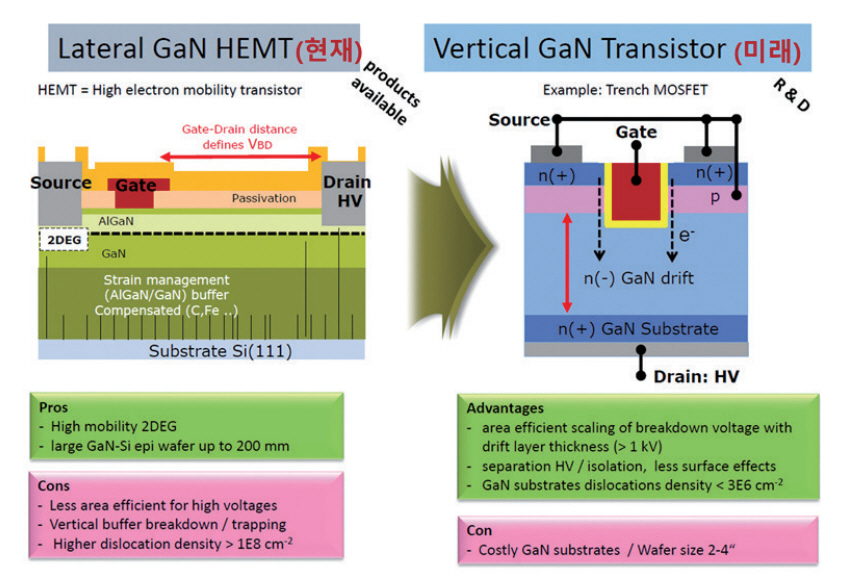

고내압, 대전류용의 전력반도체 개발을 위해서는 내압 구조가 상대적으로 만들기 쉽고, 또 소자의 면적당 전류 밀도가 큰 수직형 구조가 수평형 구조에 비해 그림 5와 같이 유리하다. 최근까지 수직형 GaN 전력반도체는 PiN 다이오드, CAVET(Current Aperture Vertical Electron Transistor), JEET, Trench FET, Vertical FinFET 등 다양한 소자가 발표되었으며, 소자별 특성을 간략하게 살펴보고자 한다.

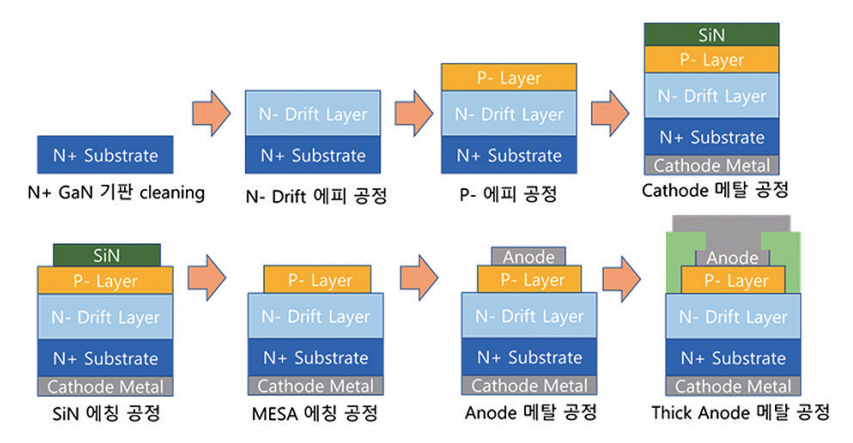

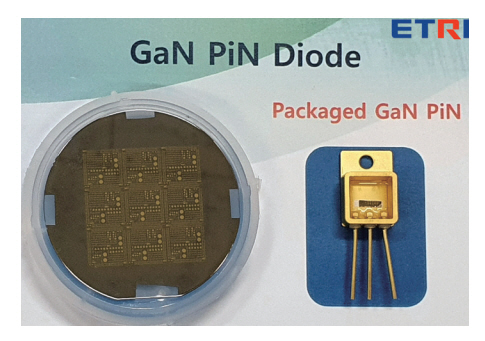

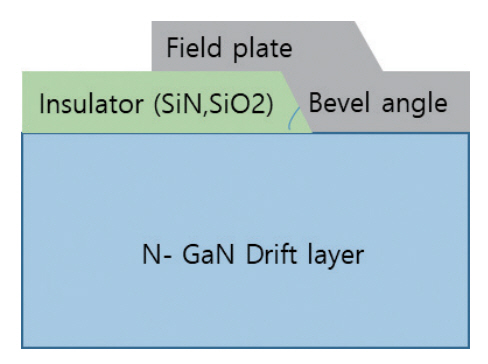

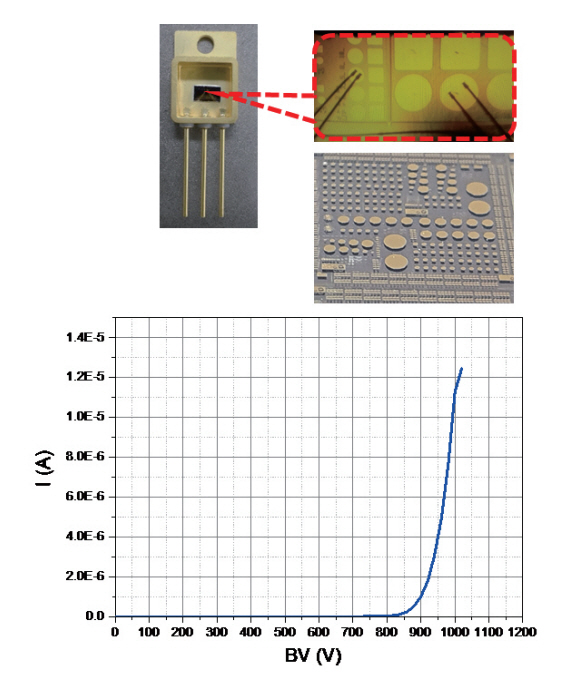

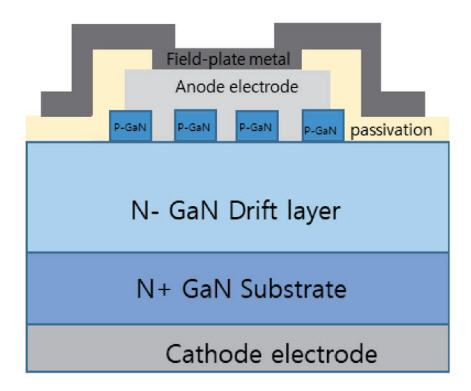

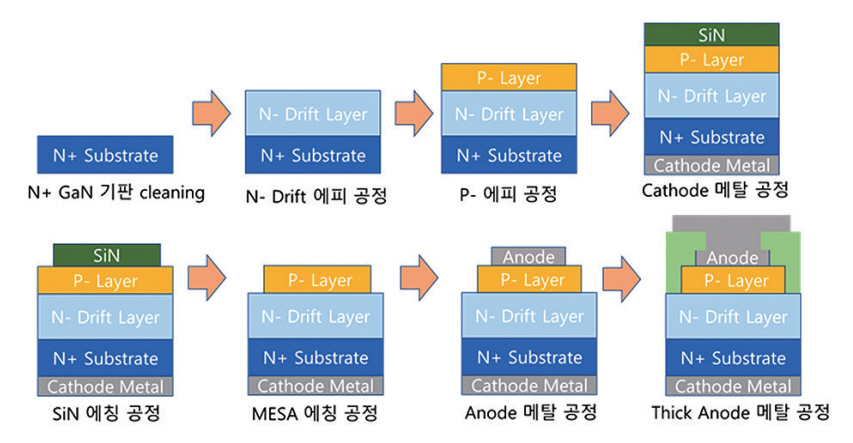

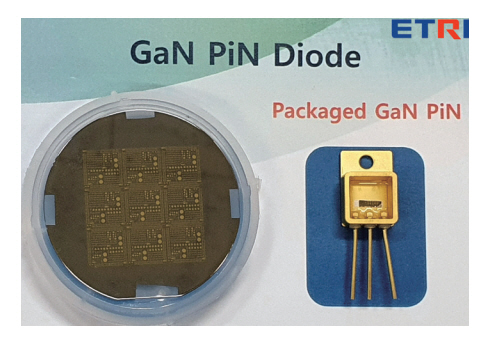

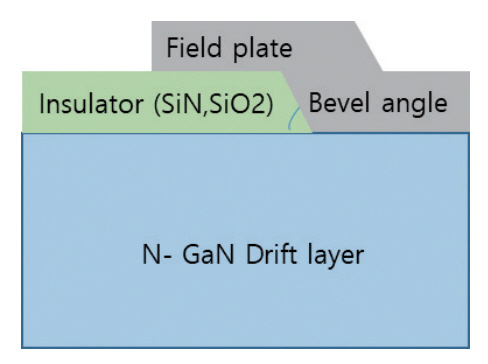

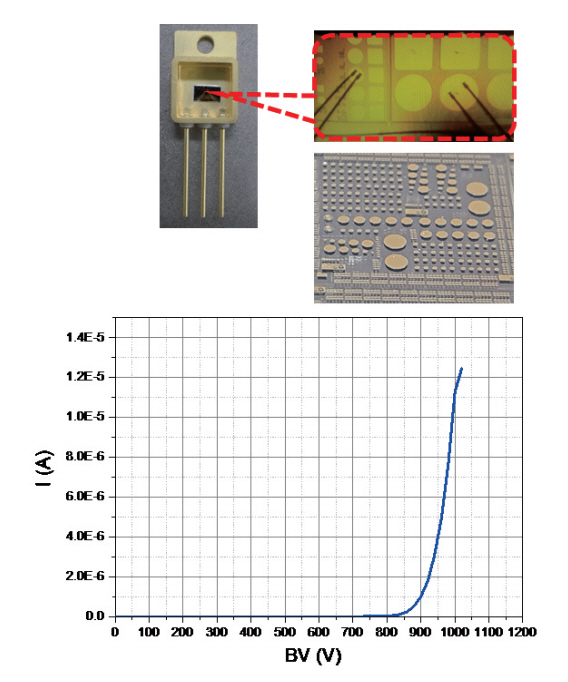

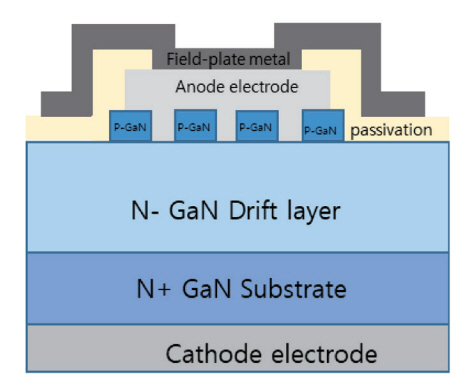

수직형 GaN PiN 다이오드의 경우 SBD(Schottky Barrier Diode)보다 턴-온 전압이 상대적으로 높지만(>3V), 낮은 누설전류와 다양한 항복전압(600V~5kV)의 성능을 가지고 있다[14-17]. 수직형 GaN PiN 다이오드에서 고내압을 견딜 수 있는 에피 소재의 도핑과 두께의 최적화 기술, 항복전압을 높일 수 있는 Edge-termination 기술 등이 중요한 개발 요소이다. 그림 6은 수직형 GaN PiN 다이오드의 소자 공정을 나타낸다. 미국의 Avogy社는 ~5 ×1015cm-3의 낮은 드리프트 농도와 30μm 이상의 긴 베이스를 이용하여 항복전압 3.7kV, 3mΩcm2 온-저항의 PiN 다이오드를 발표하였다[15]. 국내에서도 최근 한국전자통신연구원(ETRI)에서 그림 7과 같이 2인치 수직형 GaN PiN 다이오드 연구 결과를 발표하였다. GaN 단결정 기판에 ETRI에서 에피 공정을 수행하였으며, 그림 8에 나온 것과 같이 항복전압의 향상을 위해 메탈 끝단의 GaN Etching 경사각을 이용하는 Bevel angle etching 방법과 Field-plate 기술이 적용되었다. 그림 9는 ETRI의 2인치 수직형 GaN PiN 다이오드의 소자결과로 1kV급의 항복전압과 ~nA급의 누설전류를 나타낸다. PiN 다이오드는 높은 항복전압에도 불구하고 턴-온 전압이 SBD에 비해 상대적으로 높다는 단점을 가지고 있다. 미쓰비시사는 그림 10에서처럼 PiN 다이오드의 단점을 극복하기 위해 GaN 단결정 기판 위에 PiN 구조와 쇼트키 구조를 동시에 갖는 수직형 MPS(Merged PiN) 다이오드를 발표하였다[17]. MPS 다이오드의 특징인 SBD의 낮은 턴-온 전압과 PiN 다이오드의 높은 항복전압 특징을 가지는 구조로 ~1.5V의 턴-온 전압과 2kV 이상의 항복전압 특성을 보여주었다[17]. 수직형 GaN 다이오드의 주요 결과를 표 3에 정리하였다.

표 3 수직형 GaN 주요 다이오드 기술

| Device Type | BV (V) | Ron_sp (mΩcm2) | Ndirft (cm-3) | Group | Ref. |

|---|---|---|---|---|---|

| PiN diode | 260 | 1.28 | 1e17 | GE | [17] |

| PiN diode | 920 | 6.3 | 3e16 | Sumitomo | [18] |

| PiN diode | 1100 | 0.4 | 2e16 | Hosei Univ. | [19] |

| PiN diode | 3700 | 2.95 | 5e15 | Avogy | [15] |

| MPS diode | 2000 | - | 8e15 | Mitsubishi | [16] |

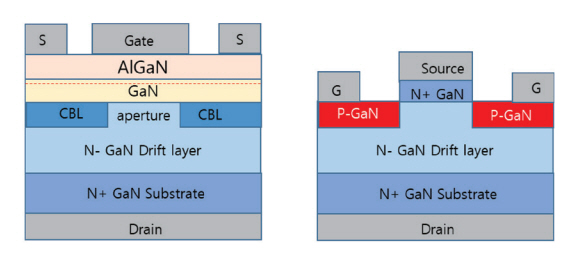

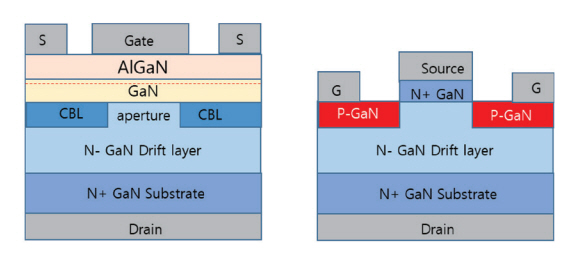

CAVET 전력반도체는 게이트와 소스 전극이 있는 AlGaN/GaN 영역의 상부층, CBL(Current Blocking Layer)을 포함하고 있는 N- 드리프트 영역, 그리고 드레인 전극이 있는 하부 N+ 영역으로 나뉜다. 그림 11은 CAVET 소자구조이다. HEMT 구조와 비슷하게 AlGaN/GaN 사이에 2DEG 채널 층이 형성되며, CBL 사이의 전류 조리개(Current Aperture)를 통해 전류가 흐르게 되며, 항복전압은 드리프트 영역에서 결정된다. 누설전류를 줄이기 위해 HEMT와 마찬가지로 표면 패시베이션 공정이 중요하며, 전류 조리개로만 전류의 흐름을 만들기 위해 CBL의 디자인 또한 중요한 요소이다. CBL은 SiN, SiO2 등의 유전체(Dielectric) 등을 사용하거나, 이온주입(Ion Implantation) 공정, P+GaN 에피 재성장 공정 등을 이용하여 정의하기도 한다[20,21]. 미국의 UCSB Misha 교수팀은 3μm 두께와 2 × 1016cm-3 도피농도의 드리프트 영역에 Mg 이온주입을 통해 CBL 영역을 정의하고, AlGaN/GaN 영역을 400℃의 낮은 온도에서 재성장한 CAVET 구조를 발표하였다[20]. 1 × 1015cm-2 dose의 Mg 이온이 GaN 쪽으로 이동하는 것을 막기 위해 저온의 MBE 공정을 시행하여 250V, 2.2mΩcm2 온-저항의 값을 보여주었다[20].

GaN CAVET 소자의 경우 높은 항복전압과 낮은 온-저항값에도 불구하고, normally-off 구동이 쉽지 않기 때문에 후속으로 Si나 SiC와 유사한 JFET 소자 연구가 발표되었다[22,23]. 소자의 구동은 그림 11과 같이 N+GaN 소스 전극에서 기판 아래의 드레인 전극으로 전류가 형성되고, p-GaN 위의 게이트에 의해 전류가 조절되는 구조이다. CAVET 소자의 경우 CBL에서 전류의 조리개 역할을 하지만 JFET은 게이트가 0V가 인가되었을 때 공핍(Depletion)이 되어 드레인으로부터 소스로 전류가 흐르지 않는 Normally-off 소자 구동이 가능하다. 미국의 Nexgenpower systems社에서 항복전압이 ~1,200V, 온-저항값이 4.9mΩ.cm2인 수직형 GaN JFET 결과를 발표하여 상용화를 준비 중이다[23].

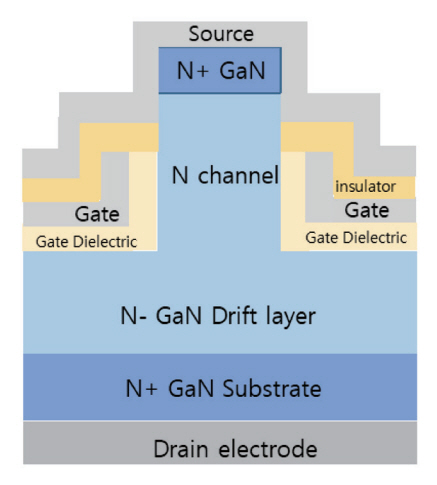

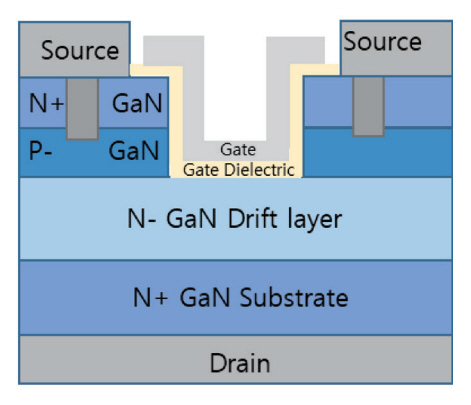

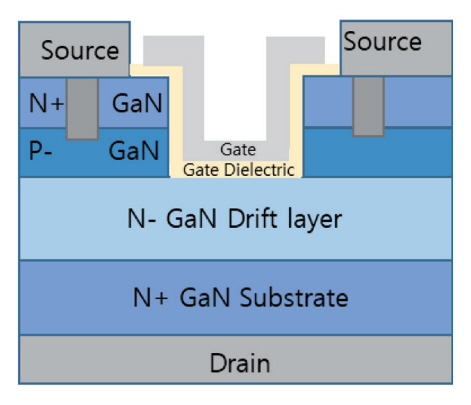

수직형 GaN Trench FET(Field-effect Transistor)는 Si, SiC 소자에서 주로 사용하는 MOSFET(Metal-oxide FET)의 소자에서 Gate Trench를 이용한 구조이다. 평탄형 소자(Planar Device)에 비해 Trench FET는 cell area가 작아서 더 많은 cell이 위치할 수 있기 때문에 온-저항값이 작은 장점이 있다. 그림 12와 같이 수직형 GaN Trench FET의 경우 N+단결정 기판 위에 N-드리프트 레이어, p-GaN, N+GaN 레이어로 구성이 된다. Trench를 p-GaN 아래까지 식각(Etching)하고 게이트 유전체와 게이트 전극을 p-GaN까지 식각된 측벽(Side Wall)에 형성한다. 게이트에 충분한 양의 전압이 인가되었을 때 게이트 유전체와 측벽의 p- GaN 사이에 전자의 반전(Inversion)이 생성되어, N+소스로부터 측벽의 반전된 p-GaN과 N-드리프트 레이어를 지나 N+드레인 쪽으로 전자가 이동하게 된다. 소자의 턴-온 전압의 경우 p-GaN 도핑의 영향을 받으며, 드리프트 레이어의 도핑과 두께가 항복전압에 영향을 미치게 된다. 에피성장 된 초기 상태보다 식각 후 표면이 거칠어서 측벽 표면의 식각 거칠기 제어와 식각 후 측벽을 얼마나 매끄럽게 복구할 수 있을지가 측벽과 게이트 인슐레이터 사이에 존재하는 트랩값의 차이를 만들어서 소자의 성능에 영향을 미친다[24,25]. 일본의 Toyoda Gosei社에서 15μm 두께와 8 × 1015cm-3 도핑 농도의 N-드리프트 영역, 4 × 1018cm-3 Mg 도핑의 p-GaN에 항복전압 향상을 위해 FP(Field-plate)를 적용한 1,600V, 12.1mΩcm2 온-저항의 값을 보여 준 Trench FET를 발표하였다[24].

수직형 GaN FinFET 소자는 GaN의 에피 재성장 혹은 p-GaN이 없이 FET 소자가 가능하다는 장점이 있다. 그림 13처럼 전류가 Fin 모양의 n-GaN 채널을 통해 조절되는 원리를 이용한다[26,27]. 얇은 Fin 모양의 n-GaN 채널에서 게이트 메탈과 GaN 사이의 일함수(Work Function) 차이로 게이트전극에 0V가 인가되면 전자의 반전이 되어 전류가 차단된다. 수직형 GaN FinFET의 경우 N+단결정 기판 위에 N-드리프트 레이어, N+소스 레이어, 그리고 N-드리프트 레이어의 Fin 모양의 N-채널로 구성이 된다. MIT Palacios 교수팀은 9.5μm 두께와 4 × 1015cm-3 도핑 농도의 드리프트 영역, 0.3μm 두께와 2 × 1019cm-3 도핑 농도의 N+소스 영역의 기판에 ~1μm 높이의 수직형 GaN FinFET 구조를 통해 1,200V, 2.1mΩcm2 온-저항의 값을 보여주었다[27]. 수직형 GaN FET의 주요 결과를 표 4에 정리하였다.

표 4 수직형 GaN FET 주요 소자 특성

| Device Type | BV (V) | Ron_sp (mΩcm2) | Ndirft (cm-3) | Group | Ref. |

|---|---|---|---|---|---|

| CAVET | 250 | 2.2 | 2e16 | UCSB | [20] |

| CAVET | 1,500 | 2.2 | 1e16 | Avogy | [21] |

| JFET | 1,000 | 4.8 | - | Avogy | [22] |

| JFET | 1,200 | 4.93 | - | Nexgen Systems | [23] |

| Trench FET | 1,600 | 12.1 | 8e15 | Toyoda | [24] |

| Trench FET | 1,200 | 1.8 | 9e15 | Toyoda | [25] |

| FinFET | 800 | 0.36 | 2e16 | MIT | [26] |

| FinFET | 1,200 | 1.2 | 4e15 | MIT | [27] |

Ⅲ. 결론

본고에서는 전기차 응용을 위한 수직형 GaN 전력반도체 기술에 대하여 살펴보았다. 차세대 수직형 GaN 전력반도체는 고속 스위칭, 전력 모듈 및 시스템의 소형화와 고효율화의 기존 수평형 GaN 전력반도체의 특징에 높은 항복전압의 특성이 추가되어 kV급 응용이 가능한 장점이 있다. 수직형 GaN 전력반도체 개발의 어려움이었던 대면적 GaN 단결정 기판, 소자 핵심 기술 등이 최근 많은 기술 발전을 이루면서 본격적인 수직형 GaN 전력반도체 개발을 위한 많은 관심을 받게 되었다. GaN 단결정 기판의 경우 4인치 기판이 상용화되었으며, 6인치 GaN 단결정 기판까지 연구개발이 되었다. 또한, 기존 HVPE 방식의 GaN 단결정 기판보다 결함이 적은 Na flux 방식이 6인치까지 개발이 되었고, 결함 밀도가 가장 작은 Ammono-thermal 방식의 GaN 단결정 기판이 2인치까지 상용화되어 현재는 기판의 대형화 연구가 진행 중이다. 수직형 GaN 전력반도체 소자로는 다이오드, CAVET, JFET, Trench FET, FinFET 등 다양한 형태의 전력 소자가 연구 중이며, 0.6-5kV급의 연구 결과가 발표되었다. 수직형 GaN PiN 다이오드와 JFET 소자는 상용화가 되었으며, CAVET과 Trench FET는 일본 및 미국에서 곧 상용화될 것으로 보인다.

글로벌 선진국은 차세대 전력반도체의 성장 가능성을 인지하고 다양한 정책적 지원을 추진 중이며, 세계 초고효율 반도체와 시스템 시장에 대한 선제 대응을 위한 전략적 육성과 기술 경쟁력 확보를 위한 투자가 많이 이루어지고 있다. 전기차 시장이 본 격적으로 열리고 있는 시기에 시스템의 고효율화와 소형화에 유리한 수직형 GaN 전력반도체 기술은 상용화 초기 단계로 국내 전력반도체에 대한 해외 의존도를 줄일 수 있을 뿐만 아니라 해외 선진업체 기술 따라잡기와 추월을 할 수 있는 분야이다. 기업체의 수직형 GaN 전력반도체 기술 경쟁력 부재 상황에서 정부의 지속적인 지원과 함께 국내 GaN 전력반도체의 공급망을 구성하는 소재-소자-모듈/시스템의 체계적인 연구개발과 더불어 산학연 연구개발 플랫폼을 통한 기술개발이 시급하다.

용어해설

GaN 실리콘(Si)에 비해 10배 이상 높은 항복 전계와 90% 이상 소형화가 가능해서 고전압 전력반도체 소자로 적합

Power Device 전력 변환, 전력 변압, 전력 안정, 전력 분배 및 제어 등을 수행하는 데 사용되는 반도체

Bulk Substrate 반도체 소자를 만드는데 기반이 되는 판(基板)을 의미하며, 보통 단결정 형태의 기판을 반도체 웨이퍼를 의미

약어 정리

2DEG

Two-Dimensional Electron Gas

BTU

British Thermal Unit

CAVET

Current Aperture Vertical Electron Transistor

CBL

Current Blocking Layer

FET

Field-effect Transistor

GaN

Gallium Nitride

HEMT

High Electron Mobility Transistor

IEA

International Energy Agency

MOSFET

Metal Oxide Semiconductor FET

MPS

Merged PiN-Schottky Diode

SBD

Schottky Barrier Diode

SiC

Silicon Carbide

WBG

Wide Band Gap

참고문헌

그림 1

그림 2

그림 3

그림 4

그림 5

그림 6

그림 7

그림 8

그림 9

그림 10

그림 11

그림 12

그림 13