# Complementary FET로 열어가는 반도체 미래 기술

## Complementary FET—The Future of the Semiconductor Transistor

김상훈 (S.H. Kim, krotc33@etri.re.kr)

이성현 (S.H. Lee, dalsimlee@etri.re.kr)

이왕주 (W.J. Lee, wjlee@etri.re.kr)

박정우 (J.W. Park, pjw21@etri.re.kr)

서동우 (D.W. Suh, dwuh@etri.re.kr)

차세대반도체소자연구실 책임연구원

차세대반도체소자연구실 선임연구원

차세대반도체소자연구실 책임연구원

차세대반도체소자연구실 책임연구원/실장

소재부품연구본부 책임연구원/본부장

### ABSTRACT

With semiconductor scaling approaching the physical limits, devices including CMOS (complementary metal-oxide-semiconductor) components have managed to overcome yet are currently struggling with several technical issues like short-channel effects. Evolving from the process node of 22 nm with FinFET (fin field effect transistor), state-of-the-art semiconductor technology has reached the 3 nm node with the GAA-FET (gate-all-around FET), which appropriately addresses the main issues of power, performance, and cost. Technical problems remain regarding the foundry of GAA-FET, and next-generation devices called post-GAA transistors have not yet been devised, except for the CFET (complementary FET). We introduce a CFET that spatially stacks p- and n-channel FETs on the same footprint and describe its structure and fabrication. Technical details like stacking of nanosheets, special spacers, hetero-epitaxy, and selective recess are more thoroughly reviewed than in similar articles on CFET fabrication.

**KEYWORDS** CMOS, complementary FET, FinFET, GAA-FET, semiconductor, transistor

### I . 트랜지스터 스케일링

인류에게 새로운 세상을 열어준 컴퓨터, TV, 모바일 등 수많은 전자제품에서부터 빅데이터, 고성능 컴퓨팅(HPC) 그리고 미래에 자율주행이나 인공지능을 가능케 할 반도체 칩은 트랜지스터의 집합으로 이루어져 있다. 이처럼 전류의 흐름을 통제하

는 작은 스위치로 간단히 정의될 수 있는 트랜지스터는, 1960년 Bell Lab의 강대원 박사가 최초로 개발한 MOSFET(Metal Oxide Semiconductor Field Effect Transistor)의 등장으로 전력 소모와 크기를 획기적으로 줄이면서 이전 세대의 트랜지스터와는 완전히 다른 혁신을 가져왔다. 인텔의 공동 창립자인 Gordon Moore는 1965년에 발표한 그의 유명한 논

\* DOI: <https://doi.org/10.22648/ETRI.2023.J.380606>

\* 본 연구는 한국전자통신연구원 내부연구과제(기초연구)의 일환으로 수행되었음[23ZB1310 듀플렉스 반도체 아키텍처 원천기술 개발].

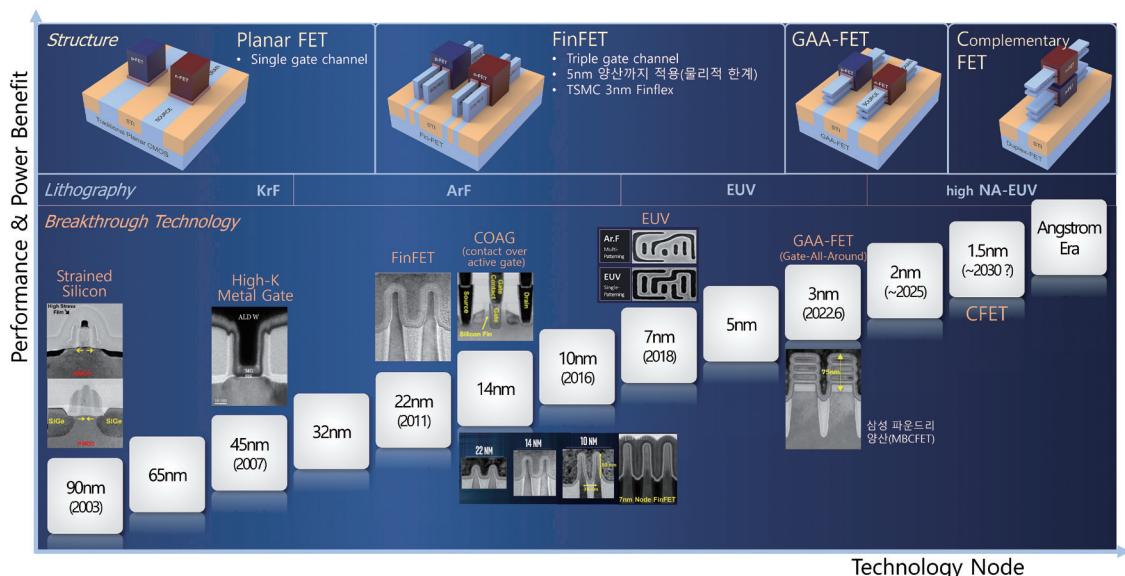

문 “Cramming More Components Onto Integrated Circuits”[1]에서 반도체에 집적하는 트랜지스터의 밀도는 매년 두 배로 증가한다는 무어의 법칙을 제안하였으며(이후에 18개월 그리고 2년으로 조정됨), 이는 지난 반세기 이상 반도체 산업을 이끄는 중요한 기술 로드맵이 되었다. 그러나 무어의 법칙은 본질적으로 경제 법칙에 가까워서 스케일링 축소에 따른 제조 비용의 증가보다 이익이 클 경우에만 유지될 수 있다. 따라서 트랜지스터는 스케일링을 통한 새로운 기술 노드의 성능지표인 PPAC(high performance, low power, small area, low cost) 방향으로 기술 발전이 이어져 왔다(그림 1).

채널과 게이트가 평면 형태로 제작되는 기존 Planar FET 스케일링의 주요 원동력은 리소그래피 기술 발전과 함께 재료 혁신을 들 수 있으나 트랜지스터 크기가 점차 작아질수록 드레인과 소스의 거리, 즉 채널의 길이가 짧아져 발생하는 SCE(Short Channel Effect)를 원천적으로 해결할 수 없는 한계에 도달하

게 되었다. 이를 해결하기 위해 22nm 노드 이후에는 FinFET이라는 새로운 트랜지스터 아키텍처를 도입하게 되었고, 상어 지느러미(Fin) 형상의 채널을 게이트가 삼면에서 둘러싸게 함으로써 on/off 스위칭 특성을 개선하여 SCE의 기술적 난제를 해결하였다. 하지만 FinFET 구조 또한 3나노급 이하에서는 채널이 원자 크기 수준으로 감소하면서 발생하는 물리적 한계에 직면하게 되어 MOSFET 자체의 성능은 물론 로직 회로 집적도와 전력효율을 더 이상 개선할 수 없는 심각한 상황에 이르게 되었다.

이에 FinFET의 물리적 한계를 극복하기 위해 채널의 모든 면을 게이트가 둘러싸는 구조인 gate-all-around FET(GAA-FET)가 새로운 트랜지스터 아키텍처로 도입되었고, 삼성전자는 2022년 6월에 세계 최초로 GAA 트랜지스터 기술을 적용한 3나노 파운드리 양산을 발표하게 되었다[2]. 삼성전자 파운드리의 3나노 GAA 공정이 최초로 적용된 칩은 중국 MicroBT사의 ASIC 칩으로 Tech Insights에

그림 1 반도체 스케일링에 따른 트랜지스터 아키텍처 혁신

2023년 7월 소개되었다[3].

전체 글로벌 반도체 시장에서 메모리 반도체 시장의 크기는 30% 전후이며, 시스템 반도체는 약 60%를 차지하고 있다. 과거 시스템 반도체 분야는 Strained channel, HKMG(High-K Metal Gate), FinFET, COAG(Contact Over Active Gate) 등(그림 1 참고) 신기술을 통해 공정 노드를 선도한 인텔에 의해 주도되었으나, 비즈니스 환경의 변화 등으로 2018년 파운드리 사업을 철수하게 되었다. 현재 전 세계 파운드리 시장은 대만의 TSMC가 2023년 1분기에 59%의 시장 점유율로 압도적인 1위를 유지하고 있으며, 삼성전자가 13%로 뒤를 잇고 있는 상황에서 2021년에 인텔이 파운드리 산업으로의 재진입을 선언하고 2024년 1.8나노 트랜지스터 양산을 목표로 하고 있다.

시스템 반도체 산업이 매년 7% 정도의 성장을 보일 것이라 예상되나, 시장을 선도하고 있는 TSMC와 삼성전자에서는 GAA-FET 이후에 적용할 트랜지스터에 대한 독자적인 전략을 발표하고 있지 못하는 상황이다. 그러나 2022년 IEEE IRDS(International Roadmap for Devices and Systems) 분석에 따르면 2나노 공정까지는 GAA-FET가 시장을 선도하고 2028년경 1.5나노 공정부터는 nMOS와 pMOS가 수직으로 적층되어 면적을 줄이고, 공통 게이트를 사용하여 제어되는 새로운 3차원 아키텍처 소자가 공정 스케일링의 한계를 극복할 새로운 기술 흐름의 주인공이 될 것으로 예상하고 있다[4].

## II. Complementary FET(CFET)

### 1. CFET의 출현

전술한 바와 같이 반도체 산업은 FinFET에서 GAA-FET 시대로의 전환점에 들어서고 있다. 또한, GAA 이후 스케일링의 한계를 넘어 고성능을 유

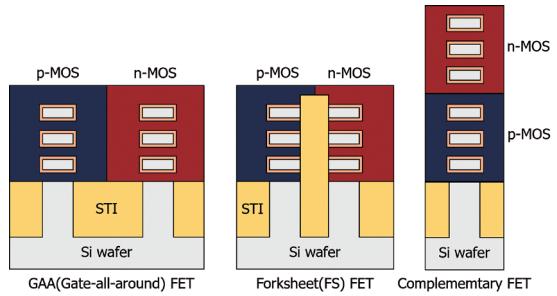

그림 2 미래 트랜지스터 후보군의 개념도

(GAA-FET, Forksheet FET and CFET)

지하면서 더 작은 Footprint 요구를 충족시키기 위해 현재 다양한 연구가 진행되고 있으며, 이 가운데에는 IBM과 삼성전자가 공동으로 연구 개발하고 있는 VTFET(Vertical Transport FET)[5,6]과 IMEC에서 제안한 Forksheet FET[7,8], L-shaped FET[9] 및 CFET(Complementary FET)[10-12] 등이 있다. 이러한 접근 방식의 공통된 주제는 수평 아키텍처에서 수직 아키텍처로의 이동이라 할 수 있다(그림 2). 이 중에서 스케일링을 확장할 가장 유력한 기술은 2018년 IMEC에서 최초로 개념을 도입한 CFET이다. 이 기술은 GAA 구조의 nMOS와 pMOS가 수직으로 적층된 형태로 제작되며, 기존 GAA-FET 대비 표준 셀과 SRAM 모두에서 50%의 면적 개선을 보였으며 TCAD 시뮬레이션을 통해 성능 또한 향상되는 것으로 보고되고 있다[13-18].

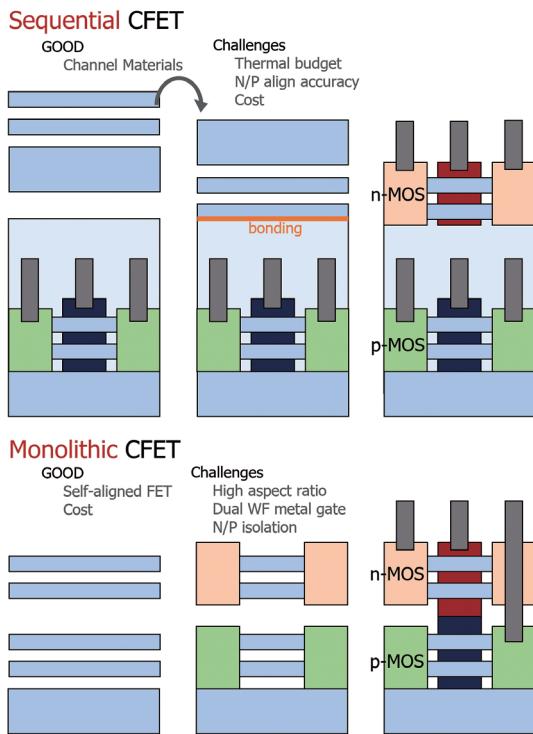

### 2. Monolithic/Sequential CFET

CFET과 동일한 개념으로 삼성전자는 3DS-FET(3-D Stacked FET), 인텔은 Ribbon FET 그리고 본 기관인 ETRI는 Duplex FET라는 명칭으로 연구가 진행되고 있으며, CFET 구현을 위한 nMOS와 pMOS 수직 적층에는 Sequential CFET[19-23]과 Monolithic CFET[24-27]의 두 가지 통합 방식이 연

그림 3 Sequential CFET과 Monolithic CFET 비교

구되고 있다(그림 3).

Sequential CFET 공정은 하부 트랜지스터 공정, 웨이퍼 본딩 및 추가적인 상부 트랜지스터 공정으로 구성되며, 상부 트랜지스터에 SiGe, Ge 혹은 III-V와 같은 이종 채널 재료를 접속하는 데 더욱 유연한 기술이다. 그러나 추가 웨이퍼 본딩 공정 및 별도의 상단 트랜지스터 공정으로 인해 제조 비용이 매우 증가할 수 있다. 또한, 하단 트랜지스터의 성능 저하 없이 고성능의 상단 트랜지스터를 제작하기 위해서는 엄격한 thermal-budget을 충족해야 하며, 고도로 미세해진 셀에서 상하부 소자의 정렬 정확도를 달성하기도 매우 어렵다.

이에 반해 Monolithic CFET 공정은 높은 종횡비 (High Aspect Ratio)의 핀 패터닝과 Dummy 폴리 게이트 패터닝을 공유하기 때문에 상하부 트랜지스

터는 자가 정렬(Self-aligned)이 이루어지게 된다. 또한, 소스/드레인 및 금속 게이트의 형성 등 온도에 민감한 주요 공정은 기존 GAA-FET와 유사하게 진행되므로 Thermal-budget 제한 없이 더 저렴한 솔루션을 제공할 수 있다. 하지만 복잡해지는 구조에 따른 전극 배선 문제를 해결해야 하며 게이트를 공유하는 nMOS와 pMOS의 동작 전압 확보를 위한 dual workfunction metal gate(DWFG) 적용이 가능한 신소재 연구와 nMOS와 pMOS 소자 분리라는 난제를 해결해야 한다. 결론적으로 두 가지 방식 모두 GAA-FET에 비해 매우 복잡해지는 구조로 인해 공정 제어 요구조건이 매우 까다롭고 제조 비용 또한 크게 치솟을 것으로 예상된다.

### 3. CFET process flow

CFET의 제작은 FinFET 공정을 기반으로 한 GAA-FET 소자의 nMOS와 pMOS의 적층형 구조로 이루어진다. 모든 채널은 사면이 모두 게이트로 둘러싸인 형태로 제작되므로 CFET에서는 나노 구조물을 3차원으로 복잡하게 형성해야 하는 어려움이 있다. 이를 위해 식각과 증착 공정의 정밀도가 요구됨은 물론 채널 주위로 게이트 절연막 및 메탈 게이트가 일정한 두께로 형성되어야 한다. 또한, 서로 다른 물성을 갖는 나노 두께 소재들의 결합으로 CFET 소자가 이루어지기 때문에 응력에 의한 계면 불안정성 및 에너지 밴드에도 변형을 줄 수 있다. 따라서 거의 모든 소재 공정에 대해 두께와 조성 그리고 농도에 대한 최적화가 필요하며, 이에 따라 CFET 제작에 많은 시행착오를 겪으리라 예상할 수 있다. 본고에서는 Sequential CFET과 Monolithic CFET의 두 가지 통합 방식 중에 FinFET에서부터 오랜 기간 관련 기술이 축적되어 있어 미래 트랜지스터로의 가능성이 좀 더 높은

- Ground Plane doping

- Si/SiGe nanosheet epitaxy growth

- Fin patterning

- Shallow Trench Isolation

- Dummy gate / Dummy gate patterning

- Outer spacer formation

- Si/SiGe cavity etch

- Inner spacer formation

- pMOS S/D selective epitaxy growth

- pMOS / nMOS isolation(SOC)

- Top S/D removal

- nMOS S/D selective epitaxy growth

- Channel release

- HKMG

- Fill metal / Contact

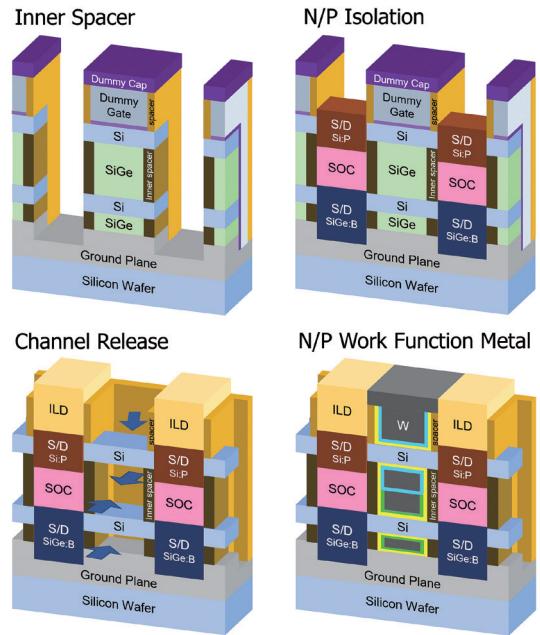

그림 4 Monolithic CFET의 제작 공정 흐름

Monolithic CFET의 제작 공정에 대해 알아보자 한다. 기존에 보고된 논문 등을 통해 예상할 수 있는 Monolithic CFET 제작 흐름은 그림 4와 같다. 주요 공정 모듈인 Si/SiGe nanosheet, Fin, STI(Shallow Trench Isolation), RMG(Replaced Metal Gate) 및 Inner/Outer spacer는 하부 pMOS와 상부 nMOS 모두에서 동일한 공정으로 진행된다. 하지만 상하부 소자를 전기적으로 완벽하게 분리하기 위한 SOC 공정, Multi-Bridge 형태의 채널을 형성하기 위해 SiGe 층만 선택적으로 식각하는 채널 릴리즈 공정 그리고 게이트를 공유하는 nMOS와 pMOS의 동작 전압 확보를 위한 DWFG 제작 공정 등 CFET 만의 주요 핵심 공정이 존재하며 다음 장에서 이에 대해 알아보자 한다.

#### 4. Si/SiGe 혼합 나노시트 기술

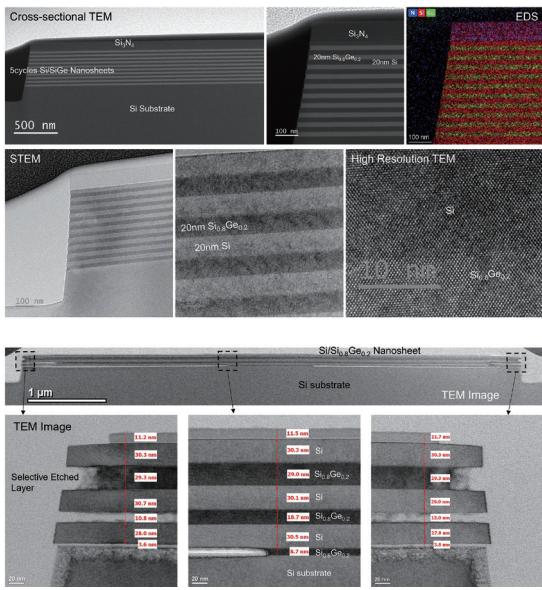

Si/SiGe 나노시트 에피 성장은 Si과 SiGe을 번갈

아 가며 적층시키되 이를 사이의 격자 정합성(Lattice Coherency)을 유지하면서 성장해야 한다. CFET 제작을 위한 에피 공정에서 가장 중요한 특성은 박막의 결정성과 균일한 표면을 들 수 있는데, Ge의 조성에 따라 SiGe과 Si층의 계면 응력이 발생하게 되어 결정성은 물론 식각 공정에서의 불안정성과에너지 밴드에도 영향을 미친다. 따라서 전위 밀도(Dislocation Density) 제어를 포함한 최적의 에피 성장 기술 개발이 반드시 이루어져야 한다.

CFET의 경우에 채널 두께는 얇고 채널 간의 간격도 작을수록 유리하므로 초기 Si/SiGe 나노시트 공정에서의 두께 정밀도가 매우 중요하다. 예를 들어, CFET의 채널 길이가 10nm인 경우 실리콘 채널 두께를 1nm만 낮춰도 subthreshold swing(SS) 값을 20mV/dec나 줄일 수 있을 것으로 시뮬레이션 결과가 보여준다. 하지만 CFET 제작 초기에 Si/SiGe 나노시트를 형성하고 그 상부에 Dummy 게이트, 열 산화막, SiGe 선택적 식각 등의 추가 공정이 진행되기 때문에 다층 박막 두께의 불확실성은 채널 간의 SS 편차를 일으킬 수도 있다. 따라서 고 진공하에서 채널의 결정성을 확보하고 조성 및 두께를 정밀하게 제어할 수 있는 UHVCVD 혹은 MBE 성장 방식이 많이 제안되고 있으며, 그림 5와 같이 ETRI에서는 비교적 저전공에서 가능한 기술로 관련 연구를 진행하고 있다[28-31].

또 다른 주요 핵심 공정인 SiGe 선택적 식각 공정은 Si/SiGe 나노시트의 Inner spacer를 확보하기 위한 SiGe 캐비티 식각과 채널을 노출하기 위한 채널 릴리즈 공정에 활용되기 때문에 CFET 전체 공정에서 가장 중요하고 정밀한 공정 설계가 요구된다. 이는 SiGe 캐비티 식각 깊이에 의해 소자의 채널 길이가 결정되며, 식각 공정이 채널의 균일성 및 표면 상태에 직접적인 영향을 주어 문턱전압( $V_t$ ), SS, 전하 이동도 등 소자 성능에 큰 영향을 주기 때문이

그림 5 ETRI의 Si/SiGe Nanosheet 에피 성장 및 SiGe 선택적 식각 기술

다. SiGe 선택적 식각 공정에는 습식법과 건식법 모두 연구되고 있으며, 식각된 캐비티의 형태가 라운딩되는 현상과 채널의 두께 손상을 방지하면서도 Si과 Spacer 등에 높은 선택비를 갖는 공정 조건이 제시되고 있다[32-35]. 여러 연구 결과를 종합해 보면 CFET의 최종 성능이 Si/SiGe 에피 성장 및 SiGe 선택적 식각 공정의 정밀도와 최적화 조건에 민감하다는 것을 확인할 수 있으며 이로 인한 공정 수율 관리가 매우 까다로울 것임을 예상할 수 있다.

## 5. Outer/Inner spacer formation

CFET의 게이트는 FinFET이나 GAA-FET 공정과 유사하게 Replace Metal Gate(RMG) 공정으로 제작된다[24-27,36]. 이때 사용되는 더미 게이트의 물질은 주로 폴리 실리콘인 사용되며, 이는 제조 과정에서 자기 정렬(Self-aligned) 공정이 가능하고 열처리 공정 등 고온 노출이 가능하기 때문이다. Outer

그림 6 CFET 제작을 위한 주요 핵심 공정

spacer는 더미 게이트 폴리의 모든 면을 Side-wall 공정을 이용하여 절연체로 둘러싸는 것을 의미하며, 더미 게이트 패터닝 및 Inner spacer 공정 시 더미 게이트를 보호하고 선택적 소스/드레인 성장을 가능하게 한다.

FinFET 공정과 차별되는 또 다른 CFET 만의 공정 모듈로는 그림 6에 개략적으로 도식한 Inner spacer 등이 있다. Inner spacer는 3차원의 적층 구조에서 게이트와 소스/드레인 간의 분리를 통해 기생 커�패시턴스를 감소시키고 채널 릴리즈 공정에서 소스/드레인을 보호하는 역할을 하는 공정이다. Inner spacer의 폭은 앞서 기술한 바와 같이 SiGe 일부를 선택적으로 식각하는 캐비티 식각에 의해 결정되는데, Inner spacer에 의해 채널의 길이(Lch)가 결정되므로 매우 정밀하고 균일한 제어가 요구된다. 캐비티 식각된 영역을 SiO<sub>2</sub>, SiCO, SiCN 등의 물질로 ALD(Atomic Layer Deposition) 방식으로 증착한 후

ALE(Atomic Layer Etching) 식각을 통해 캐비티 내에 만 Inner spacer가 남도록 공정하거나 Si와 SiGe 간의 열 산화 속도 차이를 이용한 Inner spacer를 형성하는 공정법도 연구가 진행 중이다.

## 6. nMOS/pMOS isolation

CFET 제작에 가장 어려움이 예상되는 공정 중 하나가 수직으로 적층된 nMOS와 pMOS의 전기적 분리 공정으로 지금까지 이 문제에 대한 명확한 해결 방법은 제시되지 않았으나 많은 논문과 특허에서 관련 기술을 다루고 있다. 예를 들어, 2020년에 IMEC에서 발표한 논문[20]을 보면 SOC(Spin on Carbon) 코팅을 활용하여 nMOS와 pMOS의 전기적 분리 공정을 제안하였으나(그림 6 참고) 실제 CFET 공정에 적용한 것은 아니고 가능성을 보여주는 수준에 머무르고 있다.

## 7. High-k Metal Gate(HKMG)

CFET의 게이트는 일반적으로 ALD 방식으로 채널 사이에 존재하는 미세공간(20nm 내외)에 다층으로 구성된 HKMG 박막을 균일하게 증착하여 형성한다. pMOS의 경우, TiN/HfO<sub>2</sub> 조합이 주로 사용되고 최근에는 TiN 대신 MoN을 적용하여 pMOS의 구동 전압을 낮추고 열적 안정성을 향상시키는 연구 결과가 보고되었다[37]. nMOS의 경우에는 4.45eV 이하의 낮은 Workfunction 구현을 위해 TiAlC/HfO<sub>2</sub>, TaAlC/HfO<sub>2</sub>, TaCN/HfO<sub>2</sub> 등의 다양한 합금 형태로 이루어진 HKMG 조합에 관한 연구가 진행되고 있다[38]. 이러한 HKMG 조합들은 GAA-FET 구조에 적용되어 높은 이동도와 낮은 누설 전류를 구현할 수 있는 것으로 보고되었지만 [39], 지금까지 확실한 HKMG 조합은 없는 상황으

로 추가적인 연구개발이 필요하다.

전술한 바와 같이 CFET 제작은 RMG 공정을 통해 HKMG를 형성하는데, nMOS와 pMOS 각각의 동작 전압 확보를 위해 서로 다른 HKMG를 형성하기 위해서는 주변 Inner spacer 및 채널과의 식각 선택비를 고려하여 적합한 절연 물질을 선택하는 것이 CFET의 동작 안정성을 보장하는 데 매우 중요하다. 최근 IMEC에서 CFET의 HKMG 공정을 개선하기 위해 선택적 식각에 SOC를 활용하고, Middle Dielectric Isolation(MDI) 공정을 개발한 연구 결과를 발표하였다[40]. 이와 더불어, HKMG의 두께 조절 및 Si/SiGe nanosheet 간의 간격 조절과 같은 기술적인 요소들을 통해 동작 전압을 미세 조정하는 연구도 여러 연구 그룹에서 활발하게 진행되고 있다[41-43].

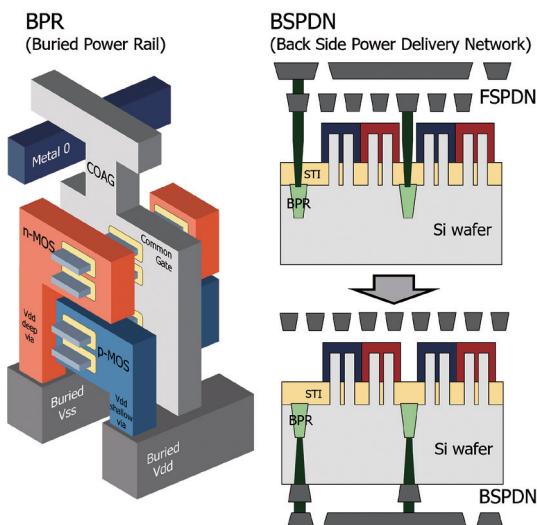

## III. Back Side Power Delivery Network(BSPDN) 기술

트랜지스터를 수직으로 적층하는 CFET 아키텍처에 필연적으로 수반되는 난제에는 금속 배선 공정을 들 수 있다. 반도체 스케일링의 한계를 극복하기 위한 여러 노력에도 불구하고 웨이퍼 전면을 통해서만 전력 공급이나 신호를 전달하는 기존의 전통적인 FSPDN(Front Side Power Delivery Network) 방식은 더 이상 전력효율 면에서 기술적 진보가 어려운 상황이다. 이에 그림 7에서와 같이 IMEC에서 2019년 처음 개념을 제시한 BSPDN(Back Side Power Delivery Network) 기술은 웨이퍼 전면에 로직 등 주요 기능을 하는 금속 배선을 배치하고 기존에 사용하지 않던 웨이퍼 후면에 전력 공급이나 신호 라우팅 등의 기능을 배치하는 기술이다[44-47]. 2021년 IEDM에 발표된 논문[48]에 따르면 BSPDN 적용 시 FSPDN 대비 44% 성능 개선 및 30%의 전력효율 향

그림 7 IMEC에서 제시한 BSPND 개념도

상을 보이며 로직의 경우 속도는 2.5배, 효율성은 60% 개선되는 것으로 보고되었다. 또한, 표준 셀 수준에서도 DTCO(Design Technology Co Optimization)를 통해 상호 연결을 위한 보다 효과적인 배치로 로직 표준 셀의 크기를 더욱 줄이는 데 도움이 되며 [49-51], 3-D System-on-Chip 구현을 가능하게 해줄 혁신적인 기술이 될 것으로 예상한다.

## IV. 결론

2000년대 스마트폰의 시대를 지나 2020년대 인공지능의 시대가 본격적으로 열리면서 트랜지스터의 스케일링을 통한 성능 향상 및 소비전력의 감소로 CMOS 기반의 AP나 GPU 등 반도체 칩에 대한 시장 수요가 급격하게 증가하였다. 시장의 혁신 요구에 대응하기 위해 FinFET, GAA-FET 그리고 CFET 같은 새로운 트랜지스터 아키텍처가 출현하였고, 다양한 산화물/금속 소재 및 에칭 공정의 발달 등 소재와 공정의 개발로 문제를 해결하면서 진

보해 가고 있다. 그러나 멀리 보면 CFET도 반도체 트랜지스터 진화의 종착지가 아니라 1.5nm 근처의 기술 노드를 담당할 중간 기착지인 것으로 보인다.

2030년 이후의 서브 나노 공정 레벨에서는 지금 과는 전혀 다른 혁신이 필요할 것으로 보이며, 소재 면에서는 2D 반도체나 Single-atom 기반의 반도체를 예상할 수도 있으나 아직은 기초 연구 단계에 머무르고 있다. 오히려 CFET 반도체를 기반으로 자성 신호(Spintronics)나 광신호(Photonics)를 조합하여 정보 처리 성능을 향상하는 방향으로 기술 진보가 이루어질 수도 있으며, 3D NAND Flash에서와 같이 3차원 고층 로직 구조로의 공정 혁신이 앞으로의 방향을 이끄는 키가 될 수도 있다. 예측 불가능한 미래 반도체 산업의 방향은 결국 최적의 소재 개발 및 새로운 혁신적인 소자 아키텍처와 이를 구현하기 위한 공정 기술 개발, 그리고 제조 비용을 절감하는 쪽으로 결정될 가능성이 크다. 이를 위해 반도체 소재 기초 연구에 대한 지속적인 지원, 반도체 기술 축적과 활용, 그리고 세계적인 반도체 기업들을 보유한 국내의 우수한 반도체 환경을 십분 활용할 수 있는 유기적인 협력 체계를 공고히 하는 것이 절대적으로 필요한 시점이다.

### 용어해설

**Transistor** 세 개 이상의 전극을 갖고 전자 신호나 전력을 스위칭 또는 증폭하는 반도체 소자

**MOSFET** 금속-산화물-반도체 전계효과 트랜지스터의 약자로 가장 일반적인 트랜지스터이며, nMOSFET과 pMOSFET, 이 둘을 한 쌍으로 하는 CMOS(Complementary MOS)로 구분함

### 약어 정리

|         |                                   |

|---------|-----------------------------------|

| BSPDN   | Back Side Power Delivery Network  |

| CFET    | Complementary FET                 |

| DTCO    | Design-Technology Co-Optimization |

| GAA-FET | Gate-all-around FET               |

|        |                                                   |

|--------|---------------------------------------------------|

| MOSFET | Metal Oxide Semiconductor Field Effect Transistor |

| PPAC   | Performance, Power, Area, Cost                    |

## 참고문헌

- [1] G.E. Moore, "Cramming more components onto integrated circuits," *Electronics*, vol. 38, no. 8, 1965.

- [2] <https://semiconductor.samsung.com/>

- [3] <https://www.techinsights.com/>

- [4] <https://irds.ieee.org/editions/2022>

- [5] H. Jagannathan et al., "Vertical-transport nanosheet technology for CMOS scaling beyond lateral-transport devices," in Proc. IEDM, (San Francisco, CA, USA), Dec. 2021, pp. 26.1.1–26.1.4.

- [6] G. Tsutsui et al., "Hardware based performance assessment of vertical-transport nanosheet technology," in Proc. IEDM, (San Francisco, CA, USA), Dec. 2022, pp. 819–822.

- [7] P. Weckx et al., "Novel forksheet device architecture as ultimate logic scaling device towards 2nm," in Proc. IEDM, (San Francisco, CA, USA), Dec. 2019, p. 8993635.

- [8] H. Mertens et al., "Forksheet FETs with bottom dielectric isolation, self-aligned gate cut, and isolation between adjacent source-drain structures," in Proc. IEDM, (San Francisco, CA, USA), Dec. 2022, pp. 555–558.

- [9] C.-Y. Yang et al., "First demonstration of heterogeneous L-shaped field effect transistor(LFET) for angstrom technology nodes," in Proc. IEDM, (San Francisco, CA, USA), Dec. 2022, pp. 475–478.

- [10] J. Ryckaert et al., "The complementary FET(CFET) for CMOS scaling beyond N3," in Proc. IEEE Symp. VLSI Tech., (Honolulu, HI, USA), June 2018, pp. 141–142.

- [11] B. Vincent et al., "A benchmark study of complementary-field effect transistor(CFET) process integration options done by virtual fabrication," *IEEE J. Electron Devices Soc.*, vol. 8, 2020, pp. 668–673.

- [12] L. Jiang et al., "Complementary FET for advanced technology nodes: Where does it stand?," in Proc. SISPAD, (Dallas, TX, USA), Sept. 2021, pp. 11–14.

- [13] L. Jiang et al., "Complementary FET device and circuit level evaluation using fin-based and sheet-based configurations targeting 3nm node and beyond," in Proc. SISPAD, (Kobe, Japan), Sept. 2020, pp. 323–326.

- [14] S.-G. Jung et al., "Performance analysis on complementary FET (CFET) relative to standard CMOS with nanosheet FET," *IEEE J. Electron Devices Soc.*, vol. 10, 2022, pp. 78–82.

- [15] S. Lee et al., "Design of JL-CFET(junctionless complementary field effect transistor)-based inverter for low power applications," *Semicond. Sci. Technol.*, vol. 37, no. 3, 2022, pp. 1–8.

- [16] B. Sun et al., "Analytical model of CFET parasitic capacitance for advanced technology nodes," *IEEE Trans. Electron. Devices*, vol. 69, no. 3, 2022, pp. 936–941.

- [17] P. Schuddinck et al., "PPAC of sheet-based CFET configurations for 4 track design with 16nm metal pitch," in Proc. VLSI Technol. Circuits, (Honolulu, HI, USA), June 2022, pp. 365–366.

- [18] J. Li et al., "Performance comparison of vertically stacked nanosheet CFET and standard CMOS without and with parasitic channels," *Microelectron. Eng.*, vol. 279, 2023, pp. 1–6.

- [19] L. Brunet et al., "First demonstration of a CMOS over CMOS 3D VLSI CoolCubeTM integration on 300mm wafers," in Proc. IEEE Symp. VLSI Tech., (Honolulu, HI, USA), June 2016, p. 7573428.

- [20] A. Vandooren et al., "3-D sequential stacked planar devices featuring low-temperature replacement metal gate junctionless top devices with improved reliability," *IEEE Trans. Electron. Devices*, vol. 65, no. 11, 2018, pp. 5165–5171.

- [21] W. Rachmady et al., "300mm heterogeneous 3D integration of record performance layer transfer germanium PMOS with silicon NMOS for low power high performance logic applications," in Proc. IEDM, (San Francisco, CA, USA), Dec. 2019.

- [22] S.K. Kwang et al., "Heterogeneous 3D Sequential CFET with Ge(110) Nanosheet p-FET on Si(100) bulk n-FET by Direct Wafer Bonding," in Proc. IEDM, (San Francisco, CA, USA), Dec. 2022, pp. 471–474.

- [23] A. Vandooren et al., "Demonstration of 3D sequential FD-SOI on CMOS FinFET stacking featuring low temperature Si layer transfer and top tier device fabrication with tier interconnections," in Proc. VLSI Tech. Circuits, (Honolulu, HI, USA), June 2022, pp. 330–331.

- [24] C.-Y. Huang et al., "3-D Self-aligned Stacked NMOS-on-PMOS Nanoribbon Transistors for Continued Moore's Law Scaling," in Proc. IEDM, (San Francisco, CA, USA), Dec. 2020, pp. 20.6.1–20.6.4.

- [25] S. Subramanian et al., "First monolithic integration of 3d complementary fet (cfet) on 300mm wafers," in Proc. IEEE Symp. VLSI Tech., (Honolulu, HI, USA), June 2020, article no. 9265073.

- [26] Chien-Te Tu et al., "First demonstration of monolithic

- 3D self-aligned GeSi channel and common gate complementary FETs by CVD epitaxy using multiple P/N junction isolation,” in Proc. IEDM, (San Francisco, CA, USA), Dec. 2022, pp. 20.3.1–20.3.4.

- [27] H. Mertens et al., “Nanosheet-based complementary field-effect transistors(CFETs) at 48nm gate pitch, and middle dielectric isolation to enable CFET inner spacer formation and multi-vt patterning,” in Proc. VLSI Tech. Circuits, (Kyoto, Japan), June 2023, pp. T1–3.

- [28] S.-J. Choi et al., “Dislocation sink annihilating threading dislocations in strain-relaxed Si<sub>1-x</sub>Ge<sub>x</sub> layer,” Nanotechnology, vol. 31, no. 12, 2020, p. 12LT01.

- [29] Kookjin Lee et al., “Defect spectroscopy of sidewall interfaces in gate-all-around silicon nanosheet FET,” Nanotechnology, vol. 32, no. 16, 2021, p. 165202.

- [30] Yi-Chun Liu et al., “Highly stacked GeSi nanosheets and nanowires by low-temperature epitaxy and wet etching,” in Proc. IEDM, (San Francisco, CA, USA), Dec. 2021, pp. 6599–6604.

- [31] C.-L. Chu et al., “Ge/Si multilayer epitaxy and removal of dislocations from Ge-nanosheet-channel MOSFETs,” Scientific Reports, vol. 12, 2022.

- [32] J. Bogdanowicz et al., “Spectroscopy: A new route towards critical-dimension metrology of the cavity etch of nanosheet transistors,” in Proc. SPIE Adv. Lithography, (Online Only), Feb. 2021, p. 116111Q.

- [33] Y. Zhao, et al., “Formation mechanism of a rounded SiGe-Etch-Front in an isotropic dry SiGe etch pocess for Gate-All-Around(GAA)-FETs,” in Proc. EDTM, (Chengdu, China), Apr. 2021.

- [34] G. Santoro et al., “Recess metrology challenges for 3D device architectures in advanced technology nodes,” in Proc. SPIE Adv. Lithography + Patterning, (San Jose, CA, USA), 2022, article no. 120530L.

- [35] E. Liu et al., “Study of selective dry etching Effects of 15-Cycle Si<sub>0.7</sub>Ge<sub>0.3</sub>/Si multilayer structure in Gate-All-Around transistor process,” Nanomaterials, vol. 13, no. 14, 2023.

- [36] S. Mukesh and J. Zhang, “A Review of the Gate-All-Around nanosheet FET process opportunities,” Electronics, vol. 11, no. 21, 2022, p. 3589.

- [37] H. Arimura et al., “Molybdenum nitride as a scalable and thermally stable pWFM for CFET,” in Proc. VLSI Tech. Circuits, (Kyoto, Japan), June 2023, pp. 1–2.

- [38] C. Zhao and J. Xiang, “Atomic layer deposition (ALD) of metal gates for CMOS,” Appl. Sci., vol. 9, no. 11, 2019, article no. 2388.

- [39] H. Mertens et al., “Vertically stacked gate-all-around Si nanowire CMOS transistors with dual work function metal gates,” in Proc. IEDM, (San Francisco, CA, USA), Dec. 2017, pp. 19.7.1–19.7.4.

- [40] H. Mertens et al., “Nanosheet-based Complementary Field-Effect Transistors(CFETs) at 48nm Gate Pitch, and middle dielectric isolation to enable CFET inner spacer formation and Multi-Vt patterning,” in Proc. VLSI Tech. Circuits, (Kyoto, Japan), June 2023, pp. 1–2.

- [41] J. Zhang et al., “High-k metal gate fundamental learning and multi-Vt options for stacked nanosheet gate-all-around transistor,” in Proc. IEDM, (San Francisco, CA, USA), Dec. 2017, pp. 22.1.1–22.1.4.

- [42] R. Bao et al., “Multiple-Vt Solutions in Nanosheet Technology for High Performance and Low Power Applications,” in Proc. IEDM, (San Francisco, CA, USA), Dec. 2019, pp. 11.2.1–11.2.4.

- [43] P.H. Vardhan, S. Ganguly, and U. Ganguly, “Threshold voltage variability in nanosheet GAA transistors,” IEEE Trans. Electron. Devices, vol. 66, no. 10, 2019, pp. 4433–4438.

- [44] W. Hafez et al., “Intel PowerVia technology: Backside power delivery for high density and high-performance computing,” in Proc. VLSI Tech. Circuits, (Kyoto, Japan), June 2023, pp. T6–1.

- [45] S. Kim et al., “Structural reliability and performance analysis of backside PDN,” in Proc. VLSI Tech. Circuits, (Kyoto, Japan), June 2023, pp. TFS2–5.

- [46] S. Yang et al., “PPA and scaling potential of backside power options in N2 and A14 nanosheet technology,” in Proc. VLSI Tech. Circuits, (Kyoto, Japan), June 2023, pp. T4–2.

- [47] A. Veloso et al., “Enabling logic with backside connectivity via n-TSVs and its potential as a scaling booster,” in Proc. Symp. VLSI Tech., (Kyoto, Japan), June 2021, pp. TFS2–6.

- [48] R. Chen et al., “Design and optimization of SRAM macro and logic using backside interconnects at 2nm node,” in Proc. IEDM, (San Francisco, CA, USA), Dec. 2021, pp. 498–501.

- [49] H.-H. Liu et al., “DTCO of sequential and monolithic CFET SRAM,” Proc. of SPIE, vol. 2023, pp. 124950Z–1.

- [50] H.-H. Liu et al., “CFET SRAM DTCO, interconnect guideline, and benchmark for CMOS scaling,” IEEE Trans. Electron. Devices, vol. 70, no. 3, 2023, pp. 883–890.

- [51] E. Park and T. Song, “Complementary FET(CFET) standard cell design for low parasitics and its impact on VLSI prediction at 3-nm process,” IEEE Trans. Very Large Scale Integr. VLSI Syst., vol. 31, no. 2, 2023, pp. 177–187.