차세대 반도체를 위한 글로벌 장비 개발 동향

Global Trends in Equipment Development for Next-Generation Semiconductors

- 저자

-

박재성차세대반도체소자연구실 jp24@etri.re.kr 박정우차세대반도체소자연구실 pjw21@etri.re.kr 서동우소재부품연구본부 dwsuh@etri.re.kr

- 권호

- 39권 6호 (통권 211)

- 논문구분

- 차세대 소재부품 기술 동향

- 페이지

- 1-7

- 발행일자

- 2024.12.01

- DOI

- 10.22648/ETRI.2024.J.390601

본 저작물은 공공누리 제4유형: 출처표시 + 상업적이용금지 + 변경금지 조건에 따라 이용할 수 있습니다.

본 저작물은 공공누리 제4유형: 출처표시 + 상업적이용금지 + 변경금지 조건에 따라 이용할 수 있습니다.- 초록

- South Korea҆s semiconductor industry, driven by Samsung and SK Hynix, dominates memory sectors such as DRAM (Dynamic Random Access Memory) and Flash memory. These leading companies are struggling to develop next-generation memory devices because of physical scaling limitations. Additionally, they heavily rely on equipment from the U.S., Japan, and the Netherlands for chip production. In this report, we investigate the roadmap for next-generation memory and logic semiconductor chips. Furthermore, we discuss research trends in the development of key technologies such as extreme ultraviolet lithography (EUV), low-resistivity metals, cryogenic high aspect ratio (HAR) etching, and indium gallium zinc oxide (IGZO) transistors.

Share

Ⅰ. 서론

한국의 전체 수출에서 반도체 섹터가 약 15% 이상을 차지할 정도로 한국은 반도체 산업에 대한 의존도가 높다. 대표적인 반도체 제조업체인 삼성전자와 SK하이닉스는 전 세계의 메모리 시장을 주도하고 있지만, 칩 제조에 사용하는 공정 장비 기술은 미국, 일본 및 네덜란드의 다양한 반도체 장비 업체에 의존하고 있다. 대표적으로 ASML사의 EUV(Extreme Ultraviolet Lithography) 노광 장비를 빠르게 확보하고 기술을 개발하는 것이 메모리 및 비메모리 제품 개발 속도에 지대한 영향을 주고 있다.

이러한 반도체 장비 및 기술 개발은 메모리 및 비메모리 반도체 제품 개발에 필요한 기술 수요에 의해 결정된다. 따라서, 차세대 반도체 소자의 개발 방향을 예측하고 준비해야만 장비 및 공정 기술을 선점할 수 있다.

최근 보고되는 메모리 및 로직 반도체 소자의 개발 방향에 대해 분석하고, 이에 필요한 장비 및 공정 기술에 대해 논의할 예정이다.

1. DRAM 개발 동향

1966년 Robert Dennard가 DRAM(Dynamic Random Access Memory)의 개념을 처음으로 제안한 이후, 컴퓨터의 메인 메모리로 이용되던 MRAM(Magnetic Random Access Memory)을 대체하였다[1]. 1T-1C 구조의 DRAM은 MRAM에 비하여 저장 밀도가 높고, 소모 전력이 매우 작고, 제작 공정이 비교적 단순하다는 장점이 있다. 또한, Lithography 공정의 혁신적인 개발로 소자의 크기를 스케일링(Scaling)하면서 이익을 극대화할 수 있었다.

Lithography 기술의 개발과 동시에, Recessed Channel Array Transistor, Saddle-Fin, Buried Word Line 기술을 개발하면서 다양한 트랜지스터 구조를 이용하여 20nm 크기의 트랜지스터를 가지는 DRAM 개발을 지속할 수 있었다[2,3].

그러나 소자의 크기가 현재 1x nm 수준으로 줄어들면서 6F2 Saddle Fin 구조는 소자의 성능 개선과 공정 한계에 도달하고 있다. 최근 6F2 DRAM에서도 Self Aligned Quadruple Patterning 및 High Aspect Ratio Etch 기술로 한계를 극복하려 하고 있지만, 다른 Row Hammer 효과, 누설 전류, RC Delay 등의 성능 저하를 가져오고 있다[4].

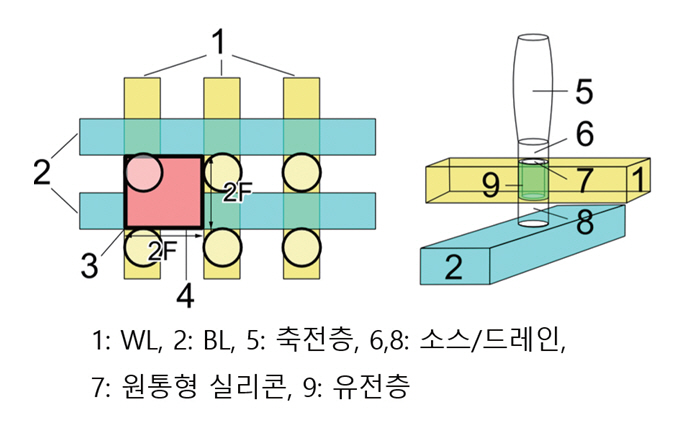

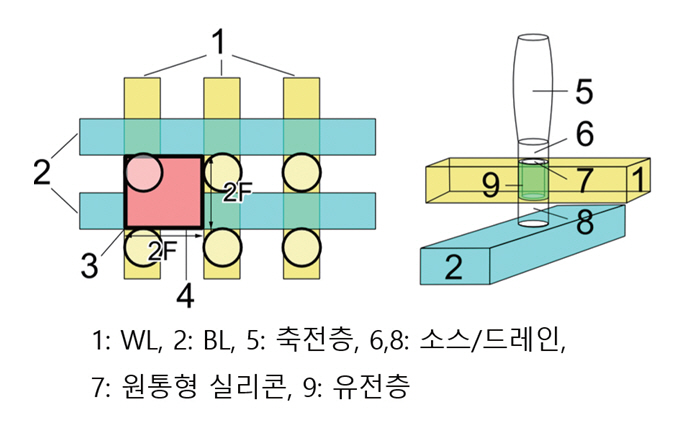

이러한 문제를 해결하기 위해 4F2 구조의 DRAM이 제안되어 개발되고 있다(그림 1)[6]. 4F2 DRAM은 6F2 DRAM에 비하여 33%의 Cell 면적을 줄일 수 있고, buried BL(Bit Line) 덕분에 더 낮은 Bit Line Capacitance를 가질 수 있다[5].

그림 1

4F2 DRAM의 모식도

출처 Tosaka, CC BY 3.0, https://creativecommons.org/licenses/ by/3.0, via Wikimedia Commons

또한, 4F2 DRAM은 구조적으로 SNC(Storage Node Contact)와 BLC(Bit Line Contact)를 구분하기 쉽기 때문에 이미 개발된 Lithography 공정으로도 충분히 개발 가능하다는 장점이 있다. 추가로 소자들이 서로 Active 영역을 공유하고 있지 않아 DRAM 신뢰성의 심각한 문제 중 하나인 Row Hammer 효과를 억제할 수 있고, 원통형 트랜지스터를 이용하기 때문에 누설 전류 및 게이트 조절 능력이 뛰어나다.

4F2 DRAM에서 BL을 형성하는 방법은 두 가지가 있다. 첫 번째로 실리콘을 에치(Etch)해서 파낸 곳에 금속 배선을 채운 뒤, 다시 금속 배선을 Etch Back하는 방법이다. 다만, 이 방법은 실리콘 사이에 금속 잔여물이 남기 쉬워서, BL-WL(Bit Line-Word Line) 단락 불량에 취약하다는 단점이 있다. 두 번째는 As 이온 주입과 열처리를 통하여 도핑된 실리콘 BL을 형성하는 방법이다. 이는 첫 번째 방법보다 공정이 쉽고, BL-WL 단락 불량을 방지하기 쉽지만, 저항이 높아져서 성능을 저하하는 문제가 있다.

BL을 형성한 후에는, 원통 형태의 실리콘 채널을 감싸는 게이트 유전막을 형성한다. 이때, SiO2 또는 High-K 산화물을 이용하게 된다. 이어서 다결정 실리콘 또는 금속을 증착하여 WL을 형성한다. 이때, 최근 이용하는 BCAT(Buried Cell Array Transistors)와 다르게 채널 원통을 모두 감싸기 때문에, 게이트의 조절 능력을 높일 수 있다. 또한, 채널의 길이를 증가시킬 수 있어서, SCE(Short-Channel Effect) 또한 개선할 수 있다.

4F2 DRAM 이외에도 3D DRAM의 연구 개발도 진행되고 있다[4]. 이는 4F2 DRAM보다 후세대의 DRAM으로 현재 활발한 연구가 이루어지고 있는 소자이다. 이는 3D NAND와 마찬가지로 메모리를 수직으로 쌓는 것이므로, 이론적으로는 무한히 소자 밀도를 증가시킬 수 있다.

이 소자는 BL이 수직 방향으로 적층되어 있고, WL은 각 BL과 수평으로 연결된 트랜지스터의 채널을 감싸고 있다. 그리고 축전층은 수평으로 길게 형성되어 있다. 축전 용량은 축전층의 면적에 비례하기 때문에, 필요한 축전 용량을 확보하기 위하여 면적을 매우 많이 차지하게 된다. 따라서, 손해 보는 면적을 상쇄할 정도로 매우 높게 메모리 소자를 적층해야 한다는 문제가 있다.

동시에 채널의 이동도가 기존의 단결정 실리콘 이동도 수준이 되어야 하므로, Si/SiGe 에피층을 쌓은 뒤에 SiGe를 선택적으로 에치하여 Si 채널을 만들어주어야 한다.

2. Flash 메모리 개발 동향

NAND Flash 메모리는 DRAM과 달리 비휘발성 메모리로, 전원이 꺼져도 데이터를 저장하기 때문에 기존의 HDD를 대체할 수 있다. 2013년 삼성전자에서 처음으로 3D NAND를 개발한 이후, 지난 10년간 메모리 층수를 약 200단 수준으로 증가시켜 왔다. 3D NAND에서 적층하는 메모리 단수를 증가시키는 것이 메모리 밀도를 높이는 가장 좋은 방법이다. 이를 위해서는 Oxide/Nitride 층을 많이 쌓고, 한 번에 에치한 뒤에 WL 전극을 채우는 기술 개발이 필수적이다. 따라서 높은 층의 유전층을 에치하는 HAR(High Aspect Ratio) 에칭 공정의 기술 개발이 필수적이다[7].

메모리 층수가 많아짐에 따라 수평 방향으로의 WL Pad의 길이도 길어지고, 이는 메모리가 차지하는 면적이 넓어지게 됨을 의미한다. 또한, WL 금속층에 의하여 웨이퍼가 받는 응력이 급격히 증가하여 웨이퍼가 말안장 모양처럼 휘어지는 Warpage 불량이 매우 심각한 문제 중 하나이다.

미래에 3D NAND 메모리의 성능 및 메모리 밀도를 더 높이기 위하여 적층하는 것 이외에도 많은 연구가 진행되고 있다. 첫째로는 수평 방향으로 스케일링을 할 수 있는 Multi-Hole 기술이다. 이는 WL Cut 사이의 채널 홀의 개수를 늘리는 것으로, WL을 채우는 공간을 에치하고, 그 공간을 WL 금속으로 채우는 공정 개발이 매우 중요하다. 두 번째로는 수직 방향으로 WL이 채워지는 두께를 스케일링해서 현재의 공정 능력으로 더 많은 층수를 쌓는 방법이다. 다만, 이 경우에는 각 소자의 간섭과 누설 전류가 커지면서 소자의 신뢰성 특성이 열화된다. 이때, 신뢰성 열화의 원인은 트랩 층을 따라서 전자가 이동하는 것으로, 트랩 층을 끊어주는 Trap-Cut 기술이 하나의 해결 방법이 될 수 있다[8].

메모리의 저장 셀을 CTF(Charge Trap Flash)가 아니라 다른 기술로 대체하는 연구도 활발히 진행되고 있다. 그 중 대표적인 방법이 바로 강유전 기술을 이용하는 것이다. 이는 SiO2와 강유전층을 이용하여 Oxide/Nitride/Oxide 층을 대체하여, 강유전층의 분극 방향에 따라 메모리 특성을 저장하는 기술이다. 구동 전압이 CTF 기술에 대비해서 낮아질 수 있게 되어 저전력 메모리를 구현할 수 있다[9].

메모리 소자의 구조 및 기술 개발 이외에도, 패키징 기술이 매우 중요한 역할을 할 수 있다. Peri와 Cell을 각각 만든 뒤에 웨이퍼를 본딩하는 개념인 Bonding VNAND가 있다. 이는 기존에 Cell을 Peri 위에 이어서 제작하는 COP(Cell Over Peri)와 다르게, Cell 제작 공정에서 발생하는 열처리가 Peri에 전달되는 문제를 해결할 수 있다. 실제로 Yangtze Memory에서 XtackingTM 제품 개발을 발표한 바 있다[10].

3. 로직 반도체 개발 동향

잘 알려진 Moore’s Law에 의해 스케일링되어 온 로직 반도체가 현재 TSMC 및 삼성전자의 3nm 수준 제품이 개발되기까지 몇 가지 중요한 기술의 혁신이 있었다.

Intel에서 처음으로 SiO2보다 유전상수가 큰 High-K Metal Gate(HKMG)를 이용하여 45nm 제품을 개발하였다. 이 기술을 이용하여 누설 전류를 수십에서 수백 배 개선하는 동시에, Poly-Si 게이트를 메탈 전극으로 대체하면서 게이트 전극의 공핍층을 제거하여 성능을 획기적으로 향상시킬 수 있었다[11]. 이어서, Intel은 약 5년 뒤에 평면 구조의 MOSFET이 아닌 3면에서 전류를 조절할 수 있는 실리콘 Fin 구조를 이용하여 22nm FinFET 제품을 개발하였다. 이 기술은 2D 구조였던 소자를 3D 구조로 바꾸게 되면서, 물리적 스케일링의 한계를 넘을 수 있는 기반을 마련하였다[12].

최근, 삼성전자가 3면에서 전류를 조절하는 Fin이 아닌 4면에서 전류를 조절할 수 있는 Nanosheet을 이용하여 GAAFET(Gate-All-Around FET) 제품 개발을 발표하였고, TSMC와 Intel 또한 GAAFET을 이용하여 Sub-3nm 수준의 로직 반도체 개발을 위해 노력하고 있다[13]. GAAFET는 4면에서 전류를 조절하므로 이론적으로 누설 전류를 최소화할 수 있고, 적층하는 Si 채널의 개수를 늘리면서 성능 향상도 얻을 수 있다는 장점이 있다. 또한, 채널의 폭을 미세하게 조절하여 회로 설계를 용이하게 할 수 있다[14].

CFET(Complementary FET)은 기존에 수평으로 배열된 NMOS와 PMOS를 수직으로 적층하는 소자로, 면적을 혁신적으로 감소시킬 수 있는 기술이다. 다만, Si 채널의 개수 증가, 게이트 메탈 패터닝, Source/Drain 에피, 컨택 전극 등 수많은 과제 해결이 필요하다.

Ⅱ. 차세대 반도체를 위한 공정 및 장비 개발 동향

1. 소자 스케일링 및 Extreme UV

소자 스케일링은 반도체 집적 칩을 제조하고 이익을 극대화하는 것에 가장 기본적인 방법으로, i-line, KrF, ArF, i-ArF, 그리고 EUV까지 혁신적인 노광 장비 및 패터닝 방법의 개발이 있었다. 1990년대 캐논과 니콘이 주도하던 노광 장비는 ASML에서 EUV 장비 개발 및 지속적인 연구 개발 투자를 바탕으로 시장을 장악했고, 반도체 제조업체는 선행 소자 개발을 위해서 가능한 한 많은 EUV 장비를 빠르게 확보하려고 경쟁하고 있다[15].

노광 장비에서 가장 중요한 Ernst Abbe 식을 보면, CD(Critical Dimension)는 광원의 파장에 비례하고, NA(Numerical Aperture)에 반비례한다.

EUV는 Sn 방울에 CO2 펄스 레이저를 조사하여 방출되는 13.5nm의 플라즈마 광원을 이용한다. 방출된 EUV는 장비에 존재하는 콜렉터와 거울에 의해 모인 뒤 웨이퍼에 조사된다. 13.5nm 광원은 어떤 기체도 흡수하기 때문에 장비 전체가 진공을 유지해야 한다는 특징이 있다. 또한, 광효율을 높이기 위하여 Mo/Si 다층 거울을 이용하여 광원의 손실을 최소화한다.

지금까지의 EUV 장비는 0.33의 NA를 이용하고 있지만, 최근 ASML에서 0.55의 High-NA 광원계를 이용하는 새로운 장비를 출시하고 반도체 제조업체에 납품하고 있다. High-NA가 형성할 수 있는 가장 작은 크기인 8nm Half Pitch의 패턴을 형성하려면, 매우 정밀한 거울을 만드는 것이 필수이다[15].

EUV 및 Lithography 장비 전체를 개발하는 것은 수십 년의 연구 개발의 결과이기 때문에, 지금 우리나라 업체에서 개발하는 것은 불가능하다. 다만, EUV 공정에 필요한 펠리클 또는 감광제 같은 부품 및 소재 연구 등에 집중하여 연구를 수행할 필요가 있다. 최근에는 SiNx를 기반으로 하여 Ru, 그래핀, 또는 카본나노튜브 등을 펠리클에 적용하여 EUV 광원의 투과도를 높이는 연구가 보고된 바 있다. 또한, 금속산화물을 포함하는 감광제를 이용하여 EUV의 공정 산포(3σ < 3nm)를 개선한 바 있다[16].

2. 저저항 신규 물질

집적 칩의 스케일링이 물리적 한계에 도달하면서 트랜지스터 자체의 성능보다 금속 배선의 성능이 전체 칩 동작에 더 큰 영향을 미치고 있다. 금속의 비저항은 배선의 폭, 두께, 그리고 결정의 크기가 작아지면서 계면에서의 산란으로 인해 비저항이 증가하는 경향을 보여준다. 현재 이용되는 Cu 또는 W 금속 배선은 전자 산란의 평균 자유 거리(Mean Free Path)가 크기 때문에 스케일링에 의한 저항 열화 문제가 심각하다. 이러한 이유로, Cu와 W를 대체하기 위한 차세대 배선 물질의 공정/장비 개발에 대한 연구가 활발히 진행 중이다[17].

신물질의 후보로는 Mo, Ru, Rh, 그리고 Ir이 집중적으로 연구되고 있고, 상대적으로 가격이 저렴한 Mo를 이용하여 W를 대체하려는 연구에 초점이 맞춰져 있다[18-20]. 특히, Mo ALD 증착 공정 및 장비의 개발로 금속 Via와 배선을 거의 단결정에 가깝게 형성하면서 전자의 산란을 최소화하여 성능 개선을 가져올 수 있다. 다만, Mo 증착 공정/장비의 개발뿐만 아니라 신물질 도입에 따른 CMP 또는 Etch 등 연계된 공정에 대한 연구 개발이 병행되어야 한다는 문제가 있다.

3. 극저온 수직 에칭

최근 10년간 3D NAND 메모리의 적층 단수를 증가시키면서 메모리 집적도를 급격히 성장시킬 수 있었다. 현재 메모리의 단수는 200단을 넘어섰고, Oxide/Nitride 층을 뚫는 공정인 채널-홀 에칭 공정 난이도가 급격하게 증가하고 있다. 128단 에칭 공정의 종횡비는 약 100nm 직경으로 약 5~6µm 깊이를 관통하면서 약 50:1의 HAR을 가진다. 나아가서 10년 안에 1,000층의 3D NAND 메모리의 개발을 목표하고 있으므로 제품의 개발 난이도는 더욱 어려워질 것이 자명하다. 특히, 종횡비가 커질수록 에칭 속도가 급격히 감소하면서 웨이퍼의 공정 시간과 비용이 기하급수적으로 증가하게 된다.

최근 Lam Research에서 극저온 에칭 공정을 이용한 CryoTM 3.0 공정 장비와 기술을 선보이며 시장을 주도하고 있고, Tokyo Electron Ltd.에서도 지속적으로 공정 장비를 개발하고 있다[21]. 이 기술은 저온에서 표면의 에칭 속도가 빨라지는 특징을 이용하였다. 먼저, 기존의 건식 에칭 공정은 표면과 화학적으로 결합한 라디칼이나 이온이 표면 원자의 결합을 약하게 만들고, 열에너지 이온을 충돌시켜 떼어내는 방식으로 에칭한다. 그러나 에칭 공정 시, 실제 기체에는 중성 종이 라디칼이나 이온보다 10~100배 이상 많이 존재하게 된다. 기존의 에칭 온도와 다르게, 저온에서는 중성 종이 표면에 물리적으로 흡착하기 쉽고 이들이 에칭 속도를 높이는 역할을 한다[22].

이렇게 물리적으로 흡착한 중성 종은 화학적으로 결합한 라디칼이나 이온과 다르게 표면 확산과 Knudsen 전달을 통해 고 종횡비 구조의 바닥까지 도달하여, 바닥 영역까지 에칭을 가능하게 한다. 추가로, 기존의 HF 기반의 에칭 가스에 Cl, Br 기반의 다른 할로겐 가스를 조합하여 표면에 형성되는 암모늄 플루오로 실리케이트 염의 두께를 조절하여 에칭 속도를 증가시킬 수 있었다.

4. IGZO 산화물 증착 공정

IGZO(In-Ga-Zn-O)는 높은 전자이동도와 낮은 누설 전류를 가지는 투명 트랜지스터 채널 물질로, 이미 디스플레이의 패널에 상용화될 정도로 성숙한 물질이다[23]. 차세대 DRAM 중 하나인 3D DRAM의 트랜지스터로 실리콘을 이용하려면, Si/SiGe 수십~수백 층을 증착해야 하므로 비용과 시간 측면에서 매우 불리하다. 따라서, 이러한 적층형 차세대 반도체에서 Si nMOSFET을 대체할 수 있는 IGZO 물질 및 트랜지스터 기술에 대한 연구가 매우 활발히 이루어지고 있다[4].

현재 상용화된 디스플레이 IGZO 트랜지스터는 주로 스퍼터링 방식으로 증착하는 반면, 복잡한 3D 구조를 가지는 4F2 또는 3D DRAM은 원자층 증착 방법을 이용해야 한다. 또한, IGZO 트랜지스터의 성능 개선을 위해서 컨택 금속의 개발도 필수적이다. 실리콘 트랜지스터는 다양한 금속 실리사이드를 이용하여 쇼트키 장벽을 낮추었던 반면, IGZO는 주로 산소 공핍 또는 수소 등의 결함을 미세하게 조절하는 것이 필요하다. 따라서, IGZO 증착뿐만 아니라 열처리 등 주변 공정 및 신물질에 대한 꾸준한 연구 개발이 필요하다.

Ⅲ. 결론

지금까지 차세대 메모리 및 비메모리 반도체의 개발 방향과 그에 필요한 공정 및 장비 개발 동향에 대하여 논의하였다. 한국의 삼성전자와 SK하이닉스는 메모리 시장을 주도해 왔지만, 앞으로도 계속해서 경쟁력을 유지하려면 수많은 공정, 장비 그리고 소재에 관해 연구하며 문제를 해결해야 한다. 하나의 회사에서 모든 문제를 해결하는 것은 절대로 불가능하다. 따라서, IMEC 또는 IBM 연구소처럼 글로벌 장비/소재 업체와 매우 긴밀하게 협력하며 차세대 반도체 집적 칩 개발에 가능한 한 많은 자원을 투자해야 할 것이다. 동시에, 국내의 다양한 반도체 장비 업체는 일부 특정 기술에 대한 경쟁력을 가질 수 있도록 연구 개발 방향의 집중이 필요할 것으로 보인다.

용어해설

메모리 컴퓨터에서 연산이 아니라 데이터를 저장하는 반도체. 휘발성, 비휘발성 그리고 쓰기, 읽기 속도에 따라 메모리의 등급이 나뉨

비메모리 컴퓨터, 휴대폰, 그리고 태블릿에서 연산을 담당하는 반도체. 로직 반도체라고 하며, CPU, AP, GPU 등이 있음

스케일링 반도체 소자의 크기를 줄이면서 성능과 수익을 극대화하는 것을 의미

약어 정리

BCAT

Buried Cell Array Transistors

BL

Bit Line

BLC

Bit Line Contact

CD

Critical Dimension

CFET

Complementary FET

COP

Cell Over Peri

CTF

Charge Trap Flash

DRAM

Dynamic Random Access Memory

EUV

Extreme Ultraviolet Lithography

GAAFET

Gate-All-Around FET

HAR

High Aspect Ratio

HKMG

High-K Metal Gate

IGZO

In-Ga-Zn-O

MRAM

Magnetic Random Access Memory

NA

Numerical Aperture

SCE

Short-Channel Effect

SNC

Storage Node Contact

A. Spessot and H. Oh, "1T-1C Dynamic Random Access Memory Status, Challenges, and Prospects," IEEE Trans. Electron Devices., vol. 67, no. 4, 2020, pp. 1382-1393.

J.Y. Kim et al., "The breakthrough in data retention time of DRAM using Recess-Channel-Array Transistor(RCAT) for 88 nm feature size and beyond," in Symp. VLSI Technol. Digest Technical Papers, Kyoto, Japan, 2003.

T. Scholesser et al., "6F² buried wordline DRAM cell for 40nm and beyond," in IEEE Int. Electron Devices Meeting, San Francisco, CA, USA, 2008.

D. Ha et al., "Exploring Innovative IGZO-channel based DRAM Cell Architectures and Key Technologies for Sub-10nm Node," in IEEE Int. Memory Workshop, Seoul, Rep. of Korea, 2024.

H. Chung et al., "Novel 4F² DRAM cell with Vertical Pillar Transistor(VPT)," in Proc. Eur. Solid-State Device Res. Conf., Helsinki, Finland, 2011. doi: 10.1109/ESSDERC.2011.6044197

S.I. Shim, J. Jang, and J. Song, "Trends and Future Challenges of 3D NAND Flash Memory," in IEEE Int. Memory Workshop, Helsinki, Finland, 2023.

K. Kim, "The Smallest Engine Transforming Humanity: The Past, Present, and Future," in IEEE Int. Electron Devices Meeting, San Francisco, CA, USA, 2021.

H. Mulaosmanovic et al., "Ferroelectric field-effect transistors based on HfO2: a review," Nanotechnol., vol. 32, no. 50, 2021. doi: 10.1088/1361-6528/ac189f

Z. Huo, W. Cheng, and S. Yang, "Unleash Scaling Potential of 3D NAND with Innovative Xtacking® Architecture," IEEE Symp. VLSI Technol. Circuits, Honolulu, HI, USA, 2022.

K. Mistry et al., "A 45nm Logic Technology with High-k+Metal Gate Transistors, Strained Silicon, 9 Cu Interconnect Layers, 193nm Dry Patterning, and 100% Pb-free Packaging," in IEEE Int. Electron Devices Meeting, Washington, DC, USA, 2007.

C. Auth et al., "A 22nm high performance and low-power CMOS technology featuring fully-depleted trigate transistors, self-aligned contacts and high density MIM capacitors," in Symp. VLSI Technol., Honolulu, HI, USA, 2012.

G. Bae et al., "3nm GAA Technology featuring Multi-Bridge-Channel FET for Low Power and High Performance Applications," in IEEE Int. Electron Devices Meeting, San Francisco, CA, USA, 2018.

Samsung Semiconductor. https://semiconductor.samsung.com/emea/

P. Graeupner et al., "EUV optics: status, outlook and future," in Opt. EUV Nanolithography XXXV, vol. 12051, 2022.

N. Fu et al., "EUV Lithography: State-of-the-Art Review," J. Microelectron. Manuf., vol. 2, 2019. doi: 10.33079/jomm.19020202

D. Gall, "The Search for the most conductive metal for narrow interconnect lines," J. Appl. Phys., vol. 127, 2020. doi: 10.1063/1.5133671

Lam Research hompage. https://www.lamresearch.com/

T. Lill et al., "Dry etching in the presence of physisorption of neutrals at lower temperatures," J. Vac. Sci. Technol. A, vol. 41, 2023. doi: 10.1116/6.0002230

그림 1

4F2 DRAM의 모식도

출처 Tosaka, CC BY 3.0, https://creativecommons.org/licenses/ by/3.0, via Wikimedia Commons

- Sign Up

- 전자통신동향분석 이메일 전자저널 구독을 원하시는 경우 정확한 이메일 주소를 입력하시기 바랍니다.