강경남 (Kang K.N.)

장현규 (Jang H.G.)

박건식 (Park K.S.)

정동윤 (Jung D.Y.)

Ⅰ. 서론

지난 2002년 미국에서 스페이스X라는 스타트업이 설립되고, 민간기업 최초로 유인우주선 발사에 성공하면서 전 세계적으로 우주산업에 관심이 집중되고 있으며, 제5차 산업혁명의 핵심은 우주기술 산업화라는 말까지 생기고 있다. 국내에서도 국가 정책으로 120대 국정과제[1]와 미래전략 2045[2] 등에서 우주개발을 위한 독자적인 기술 역량을 확보하고, 반도체‧우주‧항공 등을 전략기술로 육성할 계획을 발표하였다. 또한, 올해 우주항공청의 공식 출범 및 대전-전남-경남의 우주산업 클러스터 삼각체제 구축 사업 추진 등 우주경제 강국으로의 도약을 준비 중이다.

방사선 환경에서도 내성이 강한 우주용 반도체는 우주시대를 대비하는 필수 기술 중 하나로 내방사선 특성이 우수한 미래 반도체 기술에 대한 관심이 집중되고 있다. 시장조사 전문기관인 Spherical Insights는 전 세계 우주용 반도체 시장이 2023년 26억 달러에서 2033년에는 33억 달러로 증가할 것으로 예측하고 있다[3].

과거, 후쿠시마 원전 사고에 투입된 로봇이 반도체 부품 손상으로 무용지물이 된 바 있으며[4], 우주항공시스템의 30% 이상이 반도체 부품의 방사선 손상에 기인한 것으로 보고되었고[5], 대기 방사선에 의한 반도체 오류가 자율주행 자동차에 치명적인 결함을 유발한다고 알려져 있다[6]. 이처럼 반도체 부품은 높은 방사선 환경에 노출되었을 때 더 높은 기준의 신뢰성과 안정성이 요구되며, 방사선 손상 효과가 전자부품의 성능에 미치는 영향이 점점 더 중요해지고 있음을 알 수 있다[7].

우주 방사선이 반도체에 발생시키는 대표적인 불량문제는 크게 3가지로 1) 장기적 누적효과인 총 이온화 선량(TID: Total Ionizing Doze), 2) 변위 손상(DD: Displacement Damage), 3) 순간적으로 발생하는 단일 사건 효과(SEE: Single Event Effect)로 분류할 수 있다[8].

TID는 우주 방사선에 장시간 노출됨으로써 반도체 내에 지속적으로 피폭된 결과, 계면 트랩에 의해 문턱전압이 바뀌는 현상 및 누설전류 증가 등의 성능 저하를 일으킨다. DD는 충분한 에너지를 갖은 중성자 혹은 하전 입자와 반도체 내의 원자와의 충돌에 의해 발생된 격자 결함으로 캐리어의 수명과 이동도 감소, 누설전류 증가, 열적 전하 생성을 증가시키는 등 반도체 소자의 특성을 저하시킨다[9]. SEE는 단일입자가 반도체를 통과할 때 발생하는 현상으로 그 과정에서 생성된 전자 정공쌍(EHP: Electron Hole Pair)으로 인해 순간적으로 전류가 발생하게 된다. 이는 반도체 내의 전압, 전류 또는 전하 분포를 변화시킬 수 있으며, 이에 따라 일시적인 오작동(Soft Errors) 또는 영구적 파괴(Hard Errors)를 유발한다.

고내방사선 반도체는 대부분 국가에서 전략자산으로 여기고 있으므로 기술 자립화를 위해 많은 연구 개발이 진행 중이다. 이는 반도체 재료의 관점에서부터 반도체 소자의 동작 특성, 다양한 설계/공정 기법이 해당된다. 본고에서는 우주환경에 강한 고내방사선 특성을 가진 반도체 개발을 위한 다양한 기술에 대해 소개한다.

Ⅱ. 내방사선 반도체 기술

1. Silicon CMOS

가. 공정 기반 내방사선 기술(RHBP)

RHBP(Radiation Hardened By Process)는 방사선 영향을 최소화하도록 구성된 공정 방법이며, 고내방사선 반도체 개발을 위해서 사용되는 가장 근본적인 방법으로 여겨진다. 본 절에서는 방사선 경화에 초점이 맞춰져 있는 SOI(Silicon On Insulator) 기술, 나노 스케일의 CMOS 소자 등 RHBP 기술에 관해 소개하고자 한다.

1) SOI(Silicon On Insulator) 기술

1926년 Lilienfield의 의해 제안된 절연 게이트 전계 효과 트랜지스터(IGFET)[10]에서 유래된 SOI 기술은 1970년 SiO2가 절연 물질로 사용되기 시작하면서 SOI 기판에 CMOS 기술이 적용되었고, 1990년대 SOI 웨이퍼의 품질이 크게 향상되면서 군사 및 우주 응용 분야의 제조 기술로 자리매김해 왔다[11]. SOI 소자는 기판과 활성영역을 분리하는 매몰 산화막(Buried Oxide)의 존재로 Bulk CMOS와 비교해서 pn 접합 영역과 커패시턴스가 작아 저전력 응용 분야에 많이 사용되며, 본질적으로 CMOS 래치업이 없으므로 SEE 성능이 강하다고 알려져 있다[26].

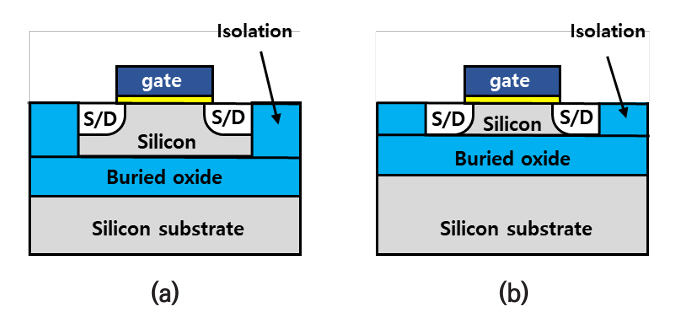

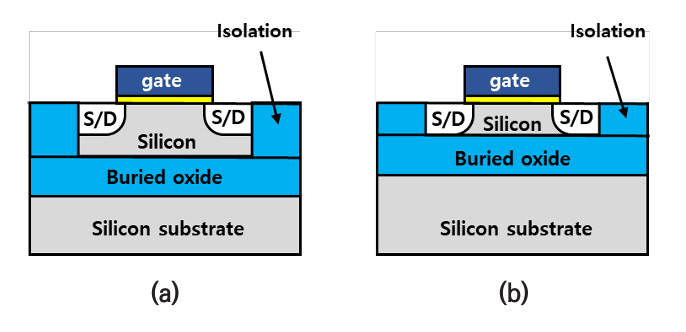

그림 1과 같이, SOI 소자구조는 PD(Partially Depleted)와 FD(Fully Depleted)-SOI CMOS 구조로 나뉠 수 있다. 두 구조의 주요 차이점은 매몰 산화막 위 실리콘층 두께이다. FD-SOI 구조에서 약 20~50nm의 두께를 가진 실리콘층은 게이트 전계에 의해 실리콘층 전체가 공핍층이 되고, PD-SOI 구조는 FD-SOI의 실리콘층보다 두꺼운 약 100~250nm의 두께를 가지며, 실리콘층의 일부만 공핍층이 된다[12]. 이러한 구조적인 성질로 PD-SOI 구조는 채널영역과 매몰 산화막 사이에 플로팅(Floating Body) 영역이 생기게 되고, 이는 방사선에 따른 입자 충돌로 생성된 캐리어가 바디(매몰 산화막 위 실리콘 층)에 쌓이면서 소스와 바디 사이의 전위가 낮아져 기생 바이폴라의 동작을 유도하게 된다. 기생 바이폴라의 동작은 Positive Feedback으로 전류를 증폭시킴에 따라 SEE의 종류인 SES(Single Event Snapback)의 형태로 영구적인 파괴가 유발될 수 있다[11]. 따라서, SEE에 대한 내성을 향상시키기 위해서는 기생 바이폴라 효과를 줄이기 위한 추가적인 기술이 반드시 필요하다.

기생 바이폴라 효과를 줄이는 방법으로 많이 사용되는 방법은 Body Tie 기술로 플로팅된 영역의 전위를 고정시켜 플로팅 영역을 제거하는 방법이다. 이로써 바디에 쌓이는 캐리어가 빠져나갈 수 있는 효율적인 경로를 제공함으로써 기생 바이폴라의 동작과 전류를 제한한다[12,13]. 플로팅 영역이 없는 FD-SOI 구조에서도 기생 바이폴라 효과가 생길 수 있으나, 기생 바이폴라의 전류 이득이 낮아 PD-SOI 구조보다도 더 우수한 SEE 내성을 가질 수 있다고 알려져 있다[14].

Bulk CMOS에 비해 SEE 성능이 우수한 SOI CMOS는 Bulk CMOS와는 달리 매몰 산화막이 추가되어 TID에는 더 민감한 특성을 보인다. PD-SOI의 경우 Bulk CMOS와 유사한 누설전류 발생 메커니즘을 갖고 있고, 이에 더해 매몰 산화막의 트랩 전하 영향을 포함하지만, Body Tie 기술로 매몰 산화막에 의한 TID 열화를 크게 개선할 수 있다.

FD-SOI는 누설전류뿐만 아니라 매몰 산화막에 축적된 양의 전하로 소자의 문턱전압 감소와 같은 특성 변화를 유도하기 때문에 TID 측면에서는 가장 취약하다고 볼 수 있다[11]. SOI 구조는 SEE 성능은 우수하나, TID에 민감한 특성을 보이므로 이를 극복하기 위해 다양한 기술이 연구되고 있다.

미국 해군연구소에서 매몰 산화막에 의한 양의 전하를 보상하기 위해 Si+을 이온주입함으로써 전자 트랩(Electron Traps)을 형성시키는 방법을 발표했다[15]. 또 다른 TID 향상 방법으로 고품질의 매몰 산화막을 갖는 Hardened SOI 웨이퍼를 사용하는 것이다. SOI 기판은 제조 과정 중에 산소 Out-diffusion으로 매몰 산화막 계면에 결함이 생성되어 TID 성능이 취약해지기 때문에 Out-diffusion으로 인해 손실되는 산소의 양을 산소이온주입으로 산화막의 결정 균일도를 개선해 계면에서의 트랩 밀도를 감소시켜 TID 성능을 높였다[16]. 또한, 산소이온주입 대신 질소이온주입으로도 내방사선 성능이 높아질 수 있다[17].

매몰 산화막뿐만 아니라 필드 산화막 내의 결함을 줄여 TID 성능을 높이는 방법도 있다. Si+ 이온주입 및 질화공정(Nitridation) 기술을 필드 산화막(STI)에 적용해 130nm PD-SOI CMOS 공정으로 제작된 512bit SRAM의 내방사선 특성이 검증되었다[18]. STI 형성 과정에서 산화막을 트렌치에 채우기 전에 Si+ 이온주입과 NO 열처리로 실리콘 표면처리를 진행하고, 트렌치를 산화막으로 채우고 평탄화 공정 후 Si+ 이온주입 공정을 추가했다. 이 기술이 적용된 SRAM은 500krad(Si)까지 내방사선 성능을 보였다. 이외에도 TID의 내성을 높이기 위한 Body Tie PD-SOI 구조인 BUSFET(Body Under Source FET)를 샌디아 국립연구소에서 제안했다[19]. BUSFET 구조는 Co-60 감사선으로 2Mrad (SiO2)까지 내방사선 성능이 검증되었다.

한편, SOI 기술을 이용해 내방사선에 특화된 Foundry 서비스가 제공되고 있다. Honeywell은 1980년부터 내방사선 성능이 우수한 집적회로를 개발하기 시작했고, 매몰 산화물 품질 개선, 도핑 프로파일 최적화, 특수한 Body Tie 기술을 150nm PD-SOI 공정에 적용해 메모리, 프로세서, ASIC(Application-Specific Integrated Circuit) 등의 제품에 적용해 우주 분야를 위한 QML(Qualified Manufacturers List) 자격을 얻었으며, 현재 150nm의 노드를 90nm 기술로 발전시키고 있다. 또 다른 Foundry 서비스를 제공하는 회사로 미국의 Skywater Technology가 있으며, 90nm FD-SOI 기술을 기반으로 내방사선 제품을 생산하고 있다.

표 1 대표적인 내방사선 특화 Foundry 비교

| Technology | Honeywell[20] | Skywater[21] |

|---|---|---|

| Substrates | PD-SOI | FD-SOI |

| Node | 150nm | 90nm |

| Wafer size | 8inch | 8inch |

| Metal | 6 | 7(5 Cu, 2 Al) |

| Isolation | STI | STI |

| Gate | Poly(w/, w/o Silicide) | CoSi2 Silicide Poly |

| Voltage | 1.8V/2.5V/3.3V | 1.2V/3.3V |

| Qualification | QML, ISO-9001, AS-9100 | ISO-9001, AS-9100 |

2) 나노 스케일 CMOS 기술

CMOS 소자의 미세화는 TID, SEE 등 방사선 내성을 높이는 방법 중 가장 좋은 방법으로 알려져 있다[22]. 실제로 SOI-CMOS 소자가 Scale Down되면서 게이트 산화막이 얇아지고, 동작 전압이 낮아지며, Pocket의 농도가 증가해 내방사선 설계/공정 기술 적용 없이도 TID에 대한 저항성이 높아졌다. 2014년 IEEE S3S 학회에서 발표된 논문[23]에 의하면 150nm에서 32nm로 Scale Down되었을 때 1Mrad(SiO2) 조건에서 NMOS의 누설전류가 약 300배 낮아졌다고 발표했다. 또한, 고농도의 바디 도핑을 사용하는 45nm와 32nm PD-SOI 상용 공정을 사용하는 것만으로 TID에 대한 고유 내성이 존재하므로 내방사선 제품 개발에 많이 사용되었다.

그러나, Scale Down에 의한 내방사선 효과는 28nm 이하의 기술에서는 적용되지 않는다고 보고 있다. 28nm 노드 이하에서 사용되는 FD-SOI는 TID에 의한 누설전류 레벨이 90nm PD-SOI 수준까지 증가한다[22]. 이는 앞서 언급된 매몰 산화막의 트랩전하에 의한 누설전류의 영향이 증가했기 때문이다. 또한, FinFET에서도 방사선 내성이 감소하는 현상이 나타나는데 SCE(Short Channel Effect)를 효과적으로 관리하기 위한 낮은 채널도핑 등에 의해 방사선으로 인한 트랩 전하들이 문턱전압 변화, 누설전류에 영향을 준다고 보고 있다[24]. 이외에도 SOI FinFET과 GAA 등의 차세대 반도체 구조도 내방사선 영향에 대해 활발히 연구 중이다[25].

나. 설계 기반 내방사선 기술(RHBD)

RHBD(Radiation Hardened By Design)는 방사선에 대한 내성을 높이기 위해 사용되는 설계 기법으로, 특별한 제조 공정을 사용하지 않고 기존의 반도체 공정으로 소자 설계 및 레이아웃 단계에서 고내방사선 성능을 구현하는 방법이다. 본 절에서는 소자 단위 Cell 디자인 기법과 가드링 기술을 소개하고자 한다.

1) 소자 단위 내방사선 설계기술

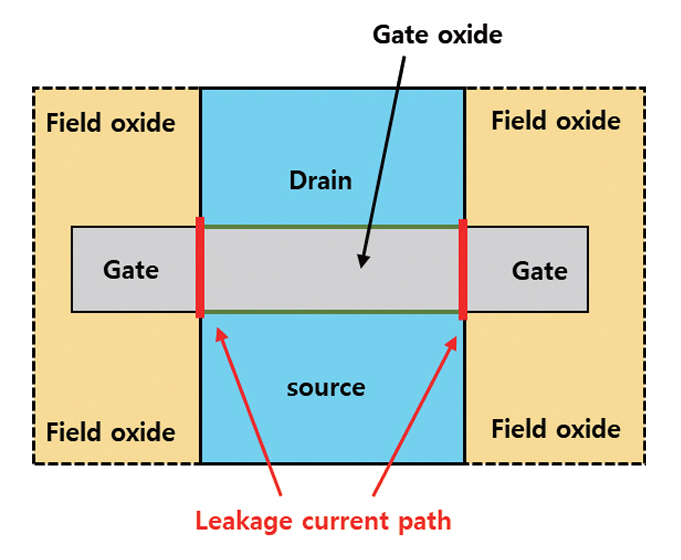

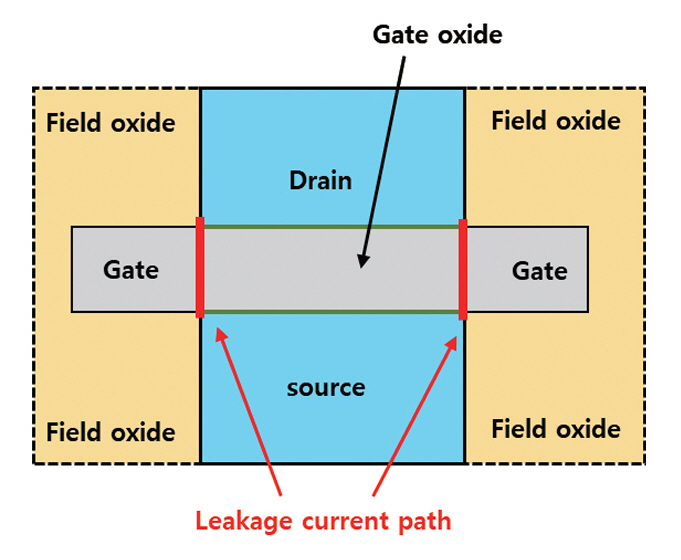

CMOS 소자의 Scale Down으로 게이트 산화막의 두께는 얇아지면서 TID에 대한 내성은 향상되고 있으나, 여전히 두꺼운 필드 산화막에서는 방사선에 의한 트랩 전하가 유도되고, 이로 인해 그림 2와 같이 필드 산화막과 게이트 산화막 경계에서 소스-드레인 누설전류가 발생하여 회로의 방사선 내성을 제한한다. 따라서, 누적 방사선에 의한 누설전류 차단을 위해 ELT(Edge Less Transistor) 구조 등과 같은 특수한 설계 기법을 사용한다[26].

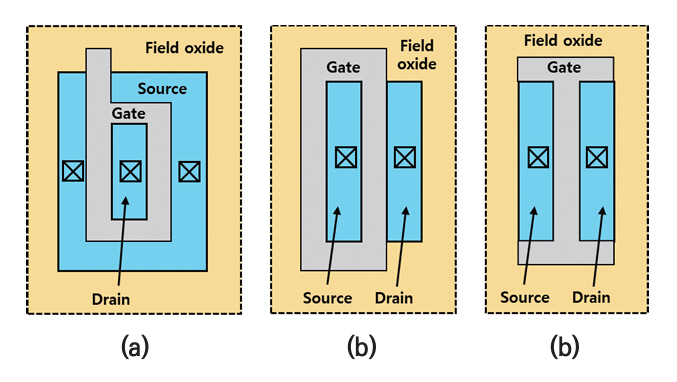

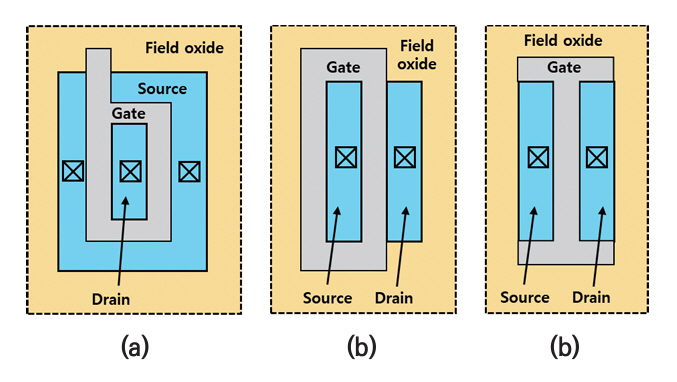

그림 3은 고내방사선 특성을 위한 세 가지 MOSFET Layout 설계구조를 보여준다. 고리형(Annular)과 밀폐형(Enclosed) 게이트 구조는 소스 또는 드레인 영역을 게이트로 감싸는 형태로써 필드 산화막과 게이트 산화막의 겹치는 부분이 없다. 이로써 필드 산화막의 측벽을 따라 발생하는 소스-드레인 간 누설전류를 크게 줄일 수 있어 30Mrad(Si)의 선량까지 견딜 수 있다고 보고되고 있다[28]. 고리형과 밀폐형 게이트 구조에서 게이트가 드레인을 둘러싸게 되면 기생 밀러 커패시턴스가 생겨 게이트 저항과 결합된 RC-delay로 인해 회로 성능을 저하시킬 수 있다[27,28]. 그러나, 구조적으로 드레인의 단면적이 줄어들어 SEE의 성능이 개선될 수 있다는 연구 결과[26]가 있으므로 회로의 목적에 맞게 설계할 필요가 있다. 또한, 고리형과 밀폐형 게이트 구조는 MOSFET의 폭과 채널 길이(W/L: Width/Lenght) 설계 비율이 2.26보다 낮아질 수 없어 아날로그 회로 설계에 제약이 될 수 있다[29].

반면에, 그림 3(c)의 I-gate 구조는 앞에서 설명한 고리형과 밀폐형 구조에 비해 내방사선 성능은 떨어지나, 일반적인 MOSFET 설계구조와 동일하게 W/L의 비율이 적용되기 때문에 회로설계 시 자유도가 높다는 장점이 있다[30].

이외에도 내방사선을 위한 설계기법으로 DGA (Dummy Gate-Assisted) 구조[31], Z Gate 구조[32] 등 다양한 게이트 구조가 연구 중이다.

PMOS는 NMOS에 비해 방사선에 의한 트랩 전하 영향으로 발생하는 누설전류에 덜 취약하므로 특수한 경우를 제외하고 일반적인 설계 기법을 따른다[26].

2) 가드링 설계기술

NMOS와 PMOS 소자 주변에 P+와 N+ 확산영역을 링 형태로 둘러싸는 가드링(Guard Ring)을 사용하면 인접 소자 간의 누설전류를 줄일 수 있고, 내방사선 성능 또한 향상시킬 수 있다. 그림 4(a)와 같이, 가드링이 없는 구조가 장시간 방사선에 노출되면 계면 트랩 전하에 의해 산화막 주변에 원하지 않는 채널이 유도되어 누설전류가 발생하나 그림 4(b)와 같은 형태로 가드링을 사용하면 기생적으로 발생되는 누설전류를 막을 수 있다[26].

또한, N-well은 VDD에 P-well은 VSS 연결하는 형태의 더블 가드링 설계 기법으로 SEE에 의해 발생되는 래치업 오류를 방지할 수 있다. 앞서 언급한 일반적인 가드링 기술 외에 트렌치 격리(STI)를 둘러싸는 고농도 도핑 기법[33], 삼중 웰 및 가드 컨택 기술[34], 소수캐리어 가드링(MICGR: MInority Carrier Guard Ring) 기술[35] 등 고내방사선을 위한 다양한 기술이 보고되고 있다.

가드링 사용은 소자 간의 간격이 늘어나기 때문에 복잡한 회로일수록 많은 면적이 소요되어 칩 면적이 증가하는 단점이 있으나, 내방사선 등 높은 신뢰성이 요구되는 우주용 반도체에는 반드시 고려되어야 할 기술이다.

다. 내방사선 집적회로 기술 동향

일반적인 Mixed-signal 집적회로는 저전력 및 빠른 속도를 위해 게이트 길이가 짧을수록 성능에 유리하며 최근 16nm 또는 그 이하까지도 사용하고 있다. 반면, 방사선 환경에서의 집적회로는 최신 공정기술보다는 소자의 안정적인 동작을 위해 130~180nm급의 비교적 구형 기술을 사용하여 방사선 저항성을 가진 회로 설계를 연구 개발하고 있다.

앞서 언급한 Honeywell사는 150nm PD-SOI 공정을 활용하여 500krad(Si) TID 내성을 가진 12bit ADC (Analog to Digital Converter)와 300krad(Si)의 12bit DAC를 비롯하여 다양한 Mixed-signal, Digital, Analog 제품 및 메모리 칩을 출시하고 있다. 영국의 BAE Systems는 45nm SOI 공정을 활용하여 1Mrad (Si)급 및 14nm FinFET 공정을 활용한 300krad(Si)급 TID 내성을 가진 다양한 ASIC 제품을 출시하고 있다[36]. 이 외에도 미국의 Analog Devices, Texas Instruments, Frontgrade Technologies, Microchip, 독일의 Infineon, 스위스의 ST Microelectronics, 영국의 Teledyne e2v, 일본의 Renesas 등이 우주항공용 고내방사선 반도체를 출시하고 있다.

미국의 NASA에서는 고내방사선 20채널 ASIC을 발표하였다[37]. 그림 3(b)와 같은 밀폐형 게이트 구조의 고내방사선 설계 기법을 사용하여 Towerjazz 180nm CMOS 공정으로 각 채널마다 16bit ADC를 포함하는 다중채널디지타이저(MCD: Multi Channel Digitizer)를 제작하였으며, 50Mrad(Si)의 TID와 123.6MeV·cm2/mg의 SEE 내성을 보여주었다.

중국의 전자과학기술대학교에서는 500nm BiCMOS 기술을 활용하여 4채널 12bit 디지털-아날로그 변환기(DAC)를 위한 방사선 내성 회로 설계를 소개하였다[38]. 아날로그 회로 블록은 3µm 이상의 High-voltage MOS를 사용함으로써 SEE의 허용 오차는 보장할 수 있었으나 반대로 TID 내성이 좋지 않아, 이를 극복하기 위해 p-sub을 격리하기 위한 Deep N-well이 있는 구조를 사용하였다.

디지털 회로는 방사선에 의한 Single-event Upset 현상을 막기 위해 동일한 회로를 중복하여 사용하는 TMR(Triple Modular Redundancy) 설계를 적용하였으며, 속도 저하 및 소모전력의 증가를 최소화하기 위해 중요한 Sub-block에만 TMR을 적용하였다.

중국 후난대학교에서는 130nm PD-SOI CMOS 공정을 활용하여 방사선에 강인한 위상 고정 루프(PLL: Phase Locked Loop) 기술을 소개하였다[39]. 방사선에 강인한 시스템 설계뿐만 아니라 단일 회로 블록에서도 방사선에 가장 취약한 회로로 널리 알려진 VCO(Voltage Controlled Oscillator), Charge Pump 및 Frequency Divider를 내성이 강하도록 설계하였다. 또한, SEE로 인한 위상 변위를 감지하기 위해 내성이 강한 Lock Detector를 설계하였다. 방사선 내성이 강한 PLL(RH-PLL)과 일반 Unhardened PLL(UH-PLL)을 각각 제작하여 특성을 비교해 본 결과, 소모 전력과 면적은 8.4%와 12.8%의 오버헤드가 있었으나, Phase Noise 특성이 100kHz offset에서 약 2.29dB 향상된 특성을 보였다. 또한, SEE 측정 결과 UH-PLL은 37.6MeV·cm2/mg 이하의 특성을 보인 반면, RH-PLL은 83.7MeV·cm2/mg의 우수한 특성을 보여주었다. 300krad(Si)의 TID 조사 이후의 지터 특성을 비교해 본 결과, UH-PLL과 RH-PLL은 각각 10.75%와 7.42%의 저하를 보여주어 심우주 탐사(Deep Space Exploration)에 대한 요구사항을 충족함을 알 수 있었다. 또한, 150nm FD-SOI, 180nm CMOS, 65nm CMOS 공정을 활용한 PLL과 비교할 때 내성이 가장 우수함을 보여주었다.

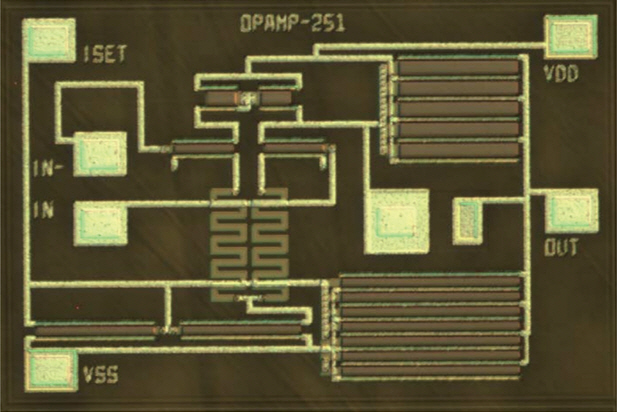

국내에서는 한국원자력연구원이 I-gate 구조를 이용한 고내방사선의 집적회로를 Full Custom IC 설계기법을 통해 SK하이닉스의 0.18µm 공정으로 D-latch, 2-stage OP amp. 및 Clock Generator를 제작하여 총 이온화 선량 2Mrad(Si)까지 시험한 결과를 발표한 바 있고[40], 한국전자통신연구원은 자체 보유하고 있는 6인치 실리콘 팹에서 PD-SOI 공정을 활용하여 집적회로를 제작한 바 있으나, 기술 선진국에 비해 우주용 고내방사선 반도체 제품이 전무하고 해당 연구도 극초기 수준에 해당된다.

2. WBG 반도체

WBG(Wide Band Gap) 기반 반도체는 고전압, 고전력, 고주파의 응용 분야에 많이 사용된다. 특히, 표 2에 보이는 바와 같이 우수한 물성적 성질로 자동차, 우주 탐사, 원자로 등과 같은 극한의 고온 및 방사선 환경에서 실리콘을 대체할 수 있는 반도체로 주목받고 있다. 본 절에서는 고내방사선 WBG 반도체 기술을 소개하고자 하며 이 중에서도 SiC, Diamond 기반의 반도체 기술에 대해 다루고자 한다.

표 2 반도체 재료에 따른 물성 비교

가. SiC 반도체(CMOS)

실리콘 카바이드(SiC)는 2001년 다이오드의 상업화[42], 2011년 MOSFET 출시[43] 이후로 고전압 Discrete 반도체 소자 분야에서는 실리콘을 대체하기 시작했다. 또한, SiC는 실리콘보다 우수한 물성적 성질에 따라 고온, 고내방사선에 적합한 재료로 알려져 센싱회로, 전력회로, 에너지 변환과 같은 응용 분야에서 수요가 늘어나고 있다[42].

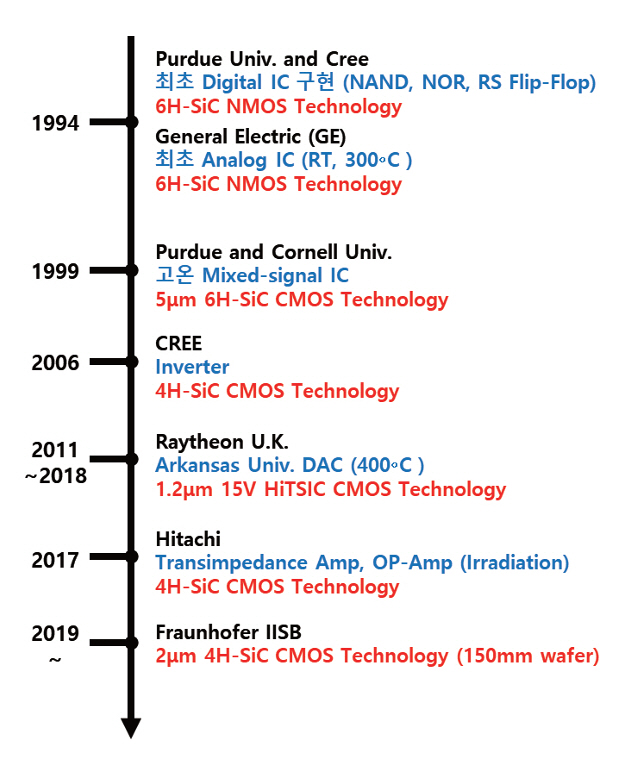

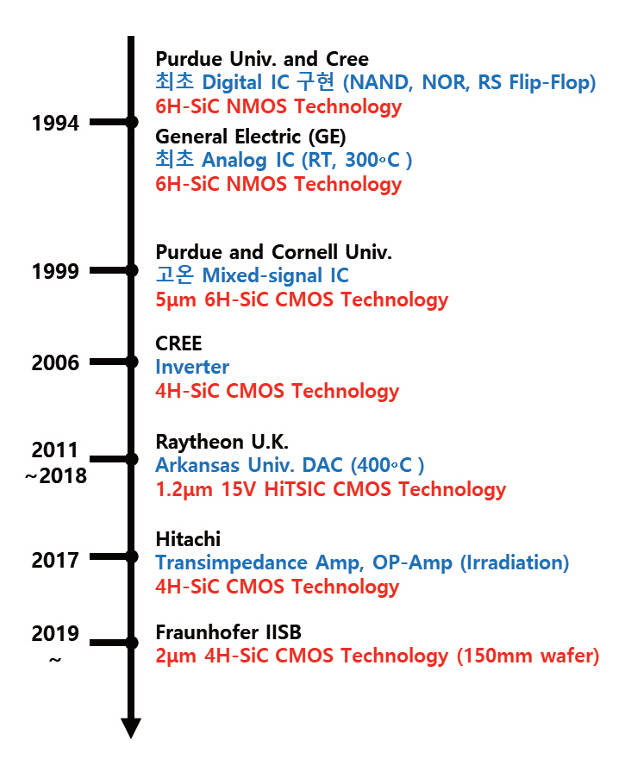

그러나 SiC 기반 반도체는 Discrete 분야에 비해 CMOS 기술의 발전은 느리게 진행되고 있다. Si CMOS 소자의 채널 길이가 10nm 이하까지 구현된 반면, SiC CMOS는 그림 5와 같이 채널 길이가 1.0µm 이상 범위에 있다. 대부분의 SiC CMOS는 고온동작에 집중적으로 연구되고 있으며, 일부 그룹에서 고내방사선 SiC CMOS 기술이 연구되고 있다[44].

그림 6은 일본 히타치가 자체 보유한 SiC CMOS 공정을 이용해 2017년 개발한 내방사선 op-amp 칩 사진을 보여준다. 회로 제작에 사용된 SiC CMOS 소자의 채널 길이는 각각 10µm(NMOS), 20µm (PMOS)이고 NO 분위기 열처리된 25nm 두께의 산화막 기술이 적용되었다. 제작된 회로는 3Mrad까지 성능변화 없이 안정적으로 동작했다. 이는 기존 Si BJT(Bipolar Junction Transistor) 기반의 op-amp와 비교했을 때 약 100배 이상의 내방사선 성능으로 보고 있다. 또한, 연구그룹은 감마선 조사 영향에 대한 저항력을 향상시키기 위한 기술로 산화막 내의 전자정공쌍의 밀도를 줄이기 위한 얇은 게이트 산화막 두께와 두꺼운 필드 산화막 위에 필드 플레이트 전극을 형성해 산화막 내에 생성된 전자-정공쌍이 재결합할 수 있도록 유도해서 트랩전하를 줄이는 방법을 제안했다. 제안된 소자가 회로에 적용되었을 때 최소 10Mrad의 감마선 저항성을 가질 수 있을 것으로 예상했다[45,46].

또한, 히타치는 2020년 100Mrad 이상의 감마선 조사 저항성을 갖는 TIA(TransImpedance Amplifier)를 개발했다고 발표했다[47]. 이전에 발표한 op-amp와 다르게 SiC CMOS 소자의 게이트 산화막을 CVD 방식으로 8nm 증착한 후 NO 분위기로 열처리했고, CMOS의 채널 길이는 5µm이다. 제작된 CMOS 소자에 TID 효과를 조사한 결과, 약 220Mrad의 방사선 저항성을 보여주며 TIA 회로에 적용했을 시 120Mrad까지 정상적으로 동작했으나, 이후 PMOS의 이동도 감소에 따른 Open-loop 이득이 저하되었다. 연구그룹은 SiC CMOS의 고내방사선을 위해서는 게이트 산화막 두께가 얇아야 문턱 전압 변화(ΔVth)를 최소화할 수 있고, Nitric-Oxide(NO) Passivation 기술을 적용해야 감마 방사선에 의한 이동도 저하를 효과적으로 완화시킬 수 있다고 강조했다.

미국 NASA Glenn Research Center는 금성 탐사의 목적으로 4H-SiC JFET 기반의 프로토타입 ICs(16bit RAM, Clock Generator)를 개발했다. 개발된 ICs는 1년 동안 500℃의 온도에서 안정적으로 작동했을 뿐만 아니라 금성 표면 대기조건(460℃, 9.3MPa)과 같은 환경에서 칩 상태로 2달 동안 동작했다고 발표했다[48]. 특히, Clock Generator는 7Mrad(Si) 이상의 TID 내성과 최대 86MeV·cm2/mg의 SEE 내성을 보였다고 소개했다[49].

나. Diamond 반도체

다이아몬드는 밴드갭이 5.47eV이며, 이는 SiC의 밴드갭보다 높은 수준이다. 또한, 10MV/cm의 높은 항복 전계, 22W/cm·K의 높은 열전도로 인해 감마선에 낮은 감도를 갖는다[41]. 이러한 특성은 다이아몬드가 내방사선 및 고온 동작 반도체 소자에 적합함을 보여준다[50]. 따라서, 극한 환경에 적용하기 위한 다이아몬드 반도체 소자들이 PiN diode[51], Schottky diode[52], MOSFET[53], BJT[54], MESFET[55] 등 다양한 구조로 연구 개발되고 있다. 그러나 연구 개발 중인 다이아몬드 반도체 소자들은 전기적 특성 검증에 국한되어 있다.

일본의 훗카이도 대학에서 RADDFET(Radiation hardened H-diamond MOSFET)을 제작하여 X-선 조사에 따른 소자 특성 변화를 확인했고, 이를 이용해 차동증폭기 회로를 구현했다[56]. RADDFET은 다이아몬드 기판 위에 Undoped 다이아몬드를 성장시키고 그 위에 p+ 층을 HFCVD(Hot Filament Chemical Vapor Deposition)로 소스와 드레인 영역을 형성한다. 이후 산소와 수소를 이용해 MPCVD(Microwave-assisted Plasma CVD)로 표면을 처리하고 Passivation으로 Al2O3 물질을 증착한다. 소스, 드레인, 게이트 전극으로는 Au/Ru(금/루테늄)이 사용되었다. 제작된 RADDFET에 X-선이 조사량이 300Mrad까지 안정적으로 특성이 유지되었다. 또한, Au/Ru 전극에 대한 방사선 영향을 확인한 결과, 비교군으로 활용된 Au/Ni(금/니켈) 전극은 30Mrad 조사 이후에 합금상태로 변했지만, Au/Ru 전극은 300Mrad 조사에도 상태 변화가 확인되지 않았다. 이러한 결과들로 볼 때, Au/Ru 전극이 적용된 RADDFET은 최소 300Mrad까지 방사선 저항성이 있을 수 있다고 발표했다[56]. 이에 더해 RADDFET을 이용해 차동증폭기 회로를 제작함으로써 다이아몬드 소자의 회로 구현 가능성을 보여주었다. 제작된 차동증폭기는 반전 및 비반전 증폭 회로 구동이 가능하였고, 비반전 출력에서는 최대 4.7배의 증폭 효과를 보였다[50].

앞서 설명하였듯 다양한 다이아몬드 기판 기반의 반도체 소자 또는 회로들이 개발되고는 있지만, 기판의 크기가 양산 수준에 미치지 못하고 있고 n형 도핑에는 아직 많은 연구 개발이 필요한 상황이며 다이아몬드 반도체만을 위한 패키징도 필요하다. 또한, 실제로 우주와 비슷한 환경에서의 동작 실험(방사선 환경, 고온 환경 등)은 아직 수많은 국내외 연구자가 해결해야 할 과제로 남아 있다.

Ⅲ. 결론

과학기술의 급속한 발전으로 반도체를 활용한 전장품은 원자력 발전소, 항공우주 장비 등의 응용 분야에 광범위하게 적용되고 있다. 최근 저궤도 위성 서비스 중심 뉴 스페이스 시대가 열리면서 고성능, 고집적, 저전력 기반 고내방사선 반도체 수요가 늘고 있다. 그러나, 고내방사선 반도체 집적회로는 전세계적으로 활용할 수 있는 공정 및 평가환경에 큰 제약이 있어 연구 개발에 많은 예산과 시간이 요구되는 어려움이 존재한다. 그럼에도 불구하고 미국, 유럽, 일본 등 선진국에서는 우주항공용 반도체 시장을 석권하기 하기 위해 정부와 산업계, 학계가 노력하고 있다. 현재 100% 수입에 의존할 수밖에 없는 한국 입장에서도 우주산업 강국이 되기 위해서는 PD-SOI 또는 SiC CMOS 등 다양한 기술을 활용한 고내방사선용 반도체 집적회로 분야에 많은 연구 개발이 절실하다. 이에 더해 지속적인 기술 개발만이 우주항공산업 기반을 견고히 구축할 수 있는 지름길이며 미래 먹거리 창출을 위한 산업으로 육성이 필요한 시점이다.

용어해설

우주 방사선 우주에서 생성되어 지구로 날아오는 고에너지 입자로 된 방사선 및 이들과 대기를 구성하는 원자들이 충돌하여 생성되어 지표에 도달하는 방사선을 통칭

반도체 집적회로 트랜지스터, 다이오드, 저항, 커패시터 등 다양한 전자부품으로 구성된 복잡한 회로를 하나의 반도체로 구현한 칩

약어 정리

ASIC

Application Specific Integrated Circuit

BUSFET

Body Under Source FET

DD

Displacement Damage

ELT

Edge Less Transistor

PDSOI

Partially Depleted Silicon On Insulator

QML

Qualified Manufacturers List

RADDFET

RADiation hardened H-terminated Diamond MOSFET

RHBD

Radiation Hardened By Design

RHBP

Radiation Hardened By Process

SEE

Single Event Effect

SiC

Silicon Carbide

SIMOX

Separation by IMplanted OXygen

STI

Shallow Trench Isolation

TID

Total Ionizing Dose

TMR

Triple Modular Redundancy

참고문헌

그림 1

그림 2

그림 3

그림 4

그림 5

그림 6