반도체 파운드리 주요 기업 현황 및 이슈별 대응 동향

Current Status and Issue-Specific Response Trends of Major Semiconductor Foundry Companies

- 저자

-

설성호통신정책연구실 ssh1517@etri.re.kr 송근혜기술전략연구센터 ghsong0227@etri.re.kr

- 권호

- 40권 2호 (통권 213)

- 논문구분

- 일반논문

- 페이지

- 67-79

- 발행일자

- 2025.04.01

- DOI

- 10.22648/ETRI.2025.J.400208

본 저작물은 공공누리 제4유형: 출처표시 + 상업적이용금지 + 변경금지 조건에 따라 이용할 수 있습니다.

본 저작물은 공공누리 제4유형: 출처표시 + 상업적이용금지 + 변경금지 조건에 따라 이용할 수 있습니다.- 초록

- Recently, the semiconductor industry has been facing significant environmental changes. This paper analyzes the current status of major global foundry companies and their strategic response trends. Specifically, the analysis focuses on each company’s wafer fabrication processes, facilities and technology, operational performance, and other relevant factors. Additionally, this study examines how companies respond to three major issues: subsidy policies and facility expansion, the strengthening dominance of the Taiwan Semiconductor Manufacturing Company and the risk of antitrust regulation, and the advent of the 2nm competition era. The findings of this paper can contribute to policy considerations for the development of the domestic non-memory semiconductor industry.

Share

Ⅰ. 서론

우리나라는 반도체 강국으로 평가받고 있지만, 메모리를 제외한 비메모리반도체 산업은 글로벌 비중이 3%대에 불과할 정도로 매우 취약한 상황이다. 비메모리반도체(특히 시스템반도체)는 다품종소량생산체제이고 기술집약적인 특성이 강하여 중소‧벤처기업이 참여하기에 적합할 뿐만 아니라 메모리반도체에 비해 경기변동에 비탄력적이라는 장점이 있다. 이에 국내 반도체 산업의 체질을 개선하고 진정한 반도체 강국으로 거듭나기 위하여 비메모리반도체 산업 육성은 시대적 당면과제가 되고 있다.

2022년 기준 국내 비메모리반도체 산업을 제조 단계별로 나누어 살펴보면, 파운드리 분야는 글로벌 비중이 16%대를 차지하여 가장 높은 수치를 기록하였고, 팹리스 분야는 1%대로 가장 낮은 수치를 보였다. 또한, 파운드리 분야는 글로벌 10대 기업에 포함된 국내업체가 2개를 차지하는 등 그 위상도 상당하여 자연스럽게 비메모리반도체 산업 생태계의 중심에 위치하였다.

그러나 최근 들어 반도체 제조를 담당하는 전문 기업인 국내 파운드리 업체들을 둘러싼 환경에 큰 변화가 발생하고 있다. 먼저 미‧중 패권 경쟁 심화와 지정학적 불확실성 증대로 각국은 반도체 제조시설을 자국 영토 내로 끌어들이기 위하여 제조 시설 투자에 대해 막대한 보조금을 제공하는 정책을 전개하고 있다. 생성형 AI 시대가 도래하면서 AI 반도체에 대한 수요가 급증하여 이를 독식한 글로벌 1위 파운드리 기업으로의 쏠림현상이 심화되고 있다. 또한, 초미세화 공정이 3나노 경쟁을 넘어 GAA(Gate All Around) 기반의 2나노 경쟁 시대로 넘어가는 시점이 도래하고 있다.

이러한 환경변화는 국내 파운드리 기업뿐만 아니라 국외 파운드리 기업에게도 많은 영향을 미치고 있다. 파운드리 기업들의 지리적 경쟁 영역은 자국 내 영토에 한정되지 않고 전 세계 시장이 대상이며, 서비스 제공 범위는 특정 분야로 국한하지 않는다. 따라서 환경변화로 인한 파운드리 기업들의 대응 동향과 경쟁 현황에 대한 상세한 이해를 위하여 분석 범위를 글로벌 전체 시장으로 넓혀 국내외 파운드리 기업들을 대상으로 살펴볼 필요가 있다.

본고는 국내 반도체 산업에 종사하고 있거나 반도체를 연구하는 이들에게 조금이나마 도움이 되고자 하는 의도에서 국내 1위 기업을 포함하여 국내외 주요 파운드리 기업들의 현황에 대하여 분석하고, 환경변화로 인한 대응 동향을 이슈별로 나누어 정리하였다.

본고는 다음과 같은 순서로 구성된다. 먼저 Ⅱ장에서 반도체 산업 가치사슬과 반도체 제조 공정 및 기술을 개괄적으로 소개한다. 이어서 Ⅲ장에서는 전 세계 파운드리 시장 현황을 간략히 살펴보고 1위부터 3위까지의 파운드리 기업을 대상으로 사업 범위, 팹 운영, 영업 실적 추이 등을 파악하기 위하여 각 기업의 연차보고서 및 관련 자료를 분석한다. Ⅳ장은 보조금 정책과 이에 대응한 생산시설의 확대, TSMC에 의한 지배력 강화와 반독점 규제 리스크, 2나노 경쟁의 도래와 준비라는 3가지 이슈와 관련된 파운드리 기업들의 움직임을 중심으로 약술한다. 그리고 이를 바탕으로 Ⅴ장에서 결론을 맺는다.

Ⅱ. 반도체 산업 가치사슬 및 제조 기술 개요

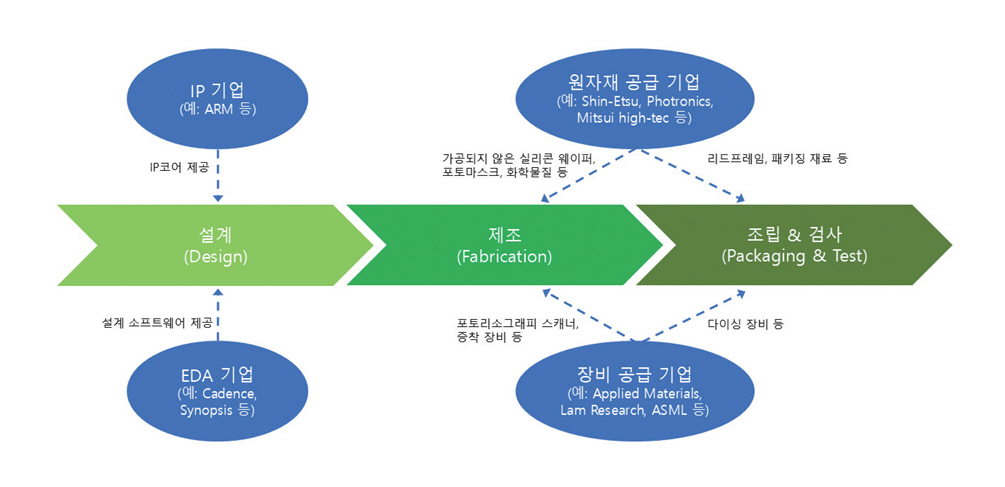

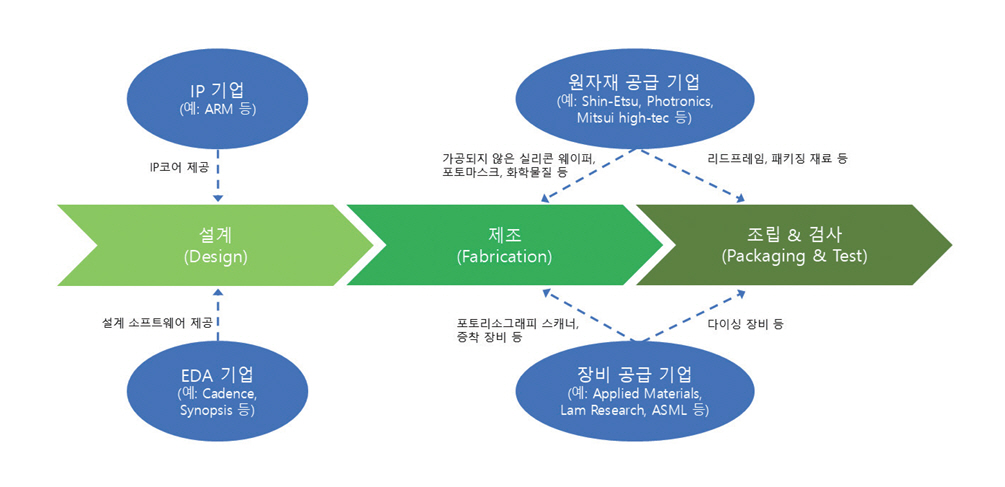

1. 반도체 산업 가치사슬

반도체 산업의 가치사슬을 간략한 형태로 도식화하면 그림 1과 같다. 반도체는 크게 설계, 제조, 조립 & 검사 단계를 거쳐 완성되는데, 설계와 제조가 분업화된 구조가 일반적이다(일부는 종합반도체기업(IDM: Integrated Device Manufacturer)에서 설계와 제조를 함께 수행).

본고의 분석 목적상, 그림 1에서 설계 단계와 조립&검사 단계에 대한 설명은 생략하고 제조 단계를 중심으로 서술하기로 한다.

업계에서는 외부 업체가 설계한 반도체를 위탁생산‧공급하는 팹을 보유한 제조 전문업체를 파운드리라고 호칭하고 있다. 파운드리가 반도체 칩을 제조하기 위해서는 팹리스 등 외부 업체로부터 칩 설계도를 받아야 할 뿐만 아니라 원자재 공급기업으로부터 소재 및 화학 물질 구매와 장비공급업체로부터 반도체 제조 장비 구매를 필요로 한다.

소재 및 화학 물질 분야는 가공되지 않은 실리콘 웨이퍼, 포토마스크, 포토레지스트, 습식 화학 물질, 공정용 가스 등으로 구성된다. 그중 실리콘 웨이퍼는 전체 소재 및 화학 물질 시장(’21년 400억USD)의 약 1/3을 차지할 정도로 중요한 시장이다[1]. 특히 직경 300mm(12인치)의 실리콘 웨이퍼는 최첨단 칩 생산을 위한 표준 투입물이 되고 있다.

반도체 생산에 필요한 정밀도, 규모, 속도, 순도 및 신뢰성을 두루 갖춘 장비는 비싸고 제작하기 어렵기 때문에 장비공급이 Applied Materials, Lam Research, Tokyo Electron, ASML 등 몇몇 기업으로 집중되어 있다. 본사를 기준으로 할 때, 미국 기업과 일본기업이 전 세계 반도체 제조 장비 시장의 70% 이상을 차지하고 있다[1].

반도체 제조 장비 시장은 웨이퍼 팹 장비 시장과 ATP(Assembly, Test and Packaging) 장비 시장으로 나뉘며 전자(’21년 908억USD)가 후자(’21년 152억USD)에 비해 규모가 훨씬 크다. 최근에 발간된 BCG & SIA(2024) 보고서에 따르면 웨이퍼 팹 장비 시장의 경우 소재 제거 및 세정(Material Removal & Cleaning), 증착(Deposition), 리소그래피(Lithography) 순서로 분야별 매출 규모가 큰 것으로 나타났다[2].

2. 반도체 제조 기술 개요

칩 제조 8대 공정과 사용되는 주요 기술에 대해 간략히 설명하면 다음과 같다.

첫 단계인 웨이퍼 제조에서는 다결정의 EG(Electronic Grade) 실리콘으로부터 매우 순수한 형태와 다양한 직경을 가진 단결정 실리콘 원통형 잉곳을 얻게 되며, 이어 잉곳을 다양한 두께의 웨이퍼로 절단하고 평탄화하는 작업을 거치게 된다. 이 단계에서 특히 중요한 사항은 초고순도의 실리콘 잉곳을 제조하는 것인데, FZ(Float Zone) 방법과 CZ(CZochralski) 방법이 대표적인 기술이다[3].

두 번째 단계인 산화는 빈 웨이퍼(Blank Wafer) 위에 산화막(SiO2)을 입히는 공정이다. 이 산화막은 반도체가 전기적 특성을 갖도록 하는데 필수적인 이온 주입(또는 도핑(Doping)) 공정 제어에 핵심적인 역할을 한다. 산화막 생성 방법은 실리콘 웨이퍼를 고온의 수증기와 반응시키는 습식, 고온의 산소와 반응시키는 건식, 산소 원자와 수소 분자가 섞인 반응성 높은 기체와 반응시키는 라디칼로 구분된다[4].

세 번째 단계인 포토공정(또는 포토리소그래피)은 웨이퍼에 반도체 회로를 패터닝하는 공정이다. 감광성 물질인 포토레지스트를 산화막이 형성된 웨이퍼 위에 바르고, 자외선이 마이크로칩 회로 패턴이 새겨진 포토마스크를 지나 포토레지스트에 투사되도록 한다. 자외선을 사용하여 칩의 회로 패턴을 웨이퍼에 그려 넣는 것을 노광이라고 부르는데 노광 장비는 크게 스태퍼와 스캐너로 구분된다. 이후 자외선에 노출된 포토레지스트를 제거하여 회로 패턴만 웨이퍼 표면에 남게 만든다.

네 번째 단계인 식각(Etching)은 회로 패턴이 아닌 산화막을 웨이퍼 표면에서 제거하는 과정이다. 식각은 습식, 건식, 플라즈마 등 다양한 방식을 사용하여 작업을 수행할 수 있다.

다섯 번째 단계에서 증착(Deposition)은 박막(Thin Film)을 만드는 과정이며 이온 주입은 반도체가 전기적인 특성을 갖도록 불순물을 투입하는 과정이다. 증착의 방법은 크게 물리적 기상 증착(PVD: Physical Vapor Deposition), 화학적 기상 증착(CVD: Chemical Vapor Deposition), 원자층 증착(ALD: Atomic Layer Deposition) 등이 있다. 어떤 방법을 사용할 것인가는 공정 노드, 칩 유형, 증착에 필요한 시간 등에 따라 달라진다. 이온 주입에서 특히 많이 사용되는 불순물은 붕소(B) 또는 인(P)으로 소량을 추가하여 P형 반도체 또는 N형 반도체를 만든다.

여섯 번째 단계인 금속 배선은 반도체 전공정(Front-End Process)의 마지막 단계로 칩의 회로 패턴을 따라 전기길이 이어지도록 하는 공정을 말한다. 이 공정에 많이 활용되는 금속은 알루미늄(Al), 티타늄(Ti), 텅스텐(W) 등이 있으며, 증착을 통해 얇은 금속막을 형성함으로써 전기가 잘 통할 수 있도록 만든다.

전공정은 파운드리 업체가 주로 담당하고, 웨이퍼 테스트, 패키징 및 최종 테스트로 이어지는 후공정(Back-End Process)은 OSAT(Outsourced Semiconductor Assembly and Test) 업체가 담당한다. 웨이퍼 테스트(또는 EDS(Electronic Die Sorting) 공정)는 전공정과 패키징 사이에서 이루어지는 검사로 불량칩이 불필요하게 패키징되는 것을 막기 위하여 웨이퍼를 대상으로 시행되며, 최종 테스트(또는 패키지 테스트)는 완성된 반도체 제품을 대상으로 최종 불량 유무를 판별하기 위하여 시행된다.

패키징은 반도체가 외부로부터 안전하게 보호되도록 포장하거나 조립하는 공정을 의미한다. 전통적인 패키징은 웨이퍼를 낱개의 칩으로 절단(즉, Dicing)하고 절단된 칩을 리드프레임 등에 접착하며 칩의 접점과 기판의 접점을 연결하는 와이어본딩 등의 단계를 거쳐 진행된다1)[5].

Ⅲ. 전 세계 파운드리 시장 및 주요기업 현황

1. 전 세계 파운드리 시장 현황

표 1은 글로벌 10대 파운드리 기업 현황을 정리한 것이다[6]. 글로벌 10대 파운드리 기업의 2023년도 매출 합계는 111,538백만USD로 글로벌 파운드리 전체 기업 매출 합계의 94.9%를 차지하고 있다.

표 1 글로벌 파운드리 10대 업체의 매출 및 시장점유율

주) 순위는 2024년 3분기 기준, 매출 단위는 백만USD, ( )는 시장점유율

출처 Reproduced with permission from https://datatrack.trendforce.com/Chart/content/95/global-foundries-revenue

글로벌 파운드리 10대 기업에는 대만 업체 4개, 중국 업체 3개, 그리고 한국/미국/이스라엘 업체가 각각 1개씩 포함된다2). 또한, 유형별로 구분하면 자체 설계제품 없이 위탁생산만을 수행하는 순수 플레이 파운드리(Pure Play Foundry 또는 Dedicated Foundry) 기업이 9개를 차지하고 있으며, 자체 설계제품에 대한 생산과 위탁생산을 병행하는 종합반도체기업(IDM)은 1개뿐이다3). 즉, 순수 플레이 파운드리 기업 형태가 글로벌 파운드리 시장에서 대세를 형성하고 있다.

한편, 대만은 글로벌 파운드리 시장점유율이 75.2%(’23년 기준)를 차지하여 국가적 위상이 매우 높다는 것을 알 수 있다[7]. 특히 1위 기업인 TSMC의 시장점유율이 최근 60%를 넘어서는 등 독점화 추세를 보이고 있다. 이에 반해 TSMC를 제외한 나머지 파운드리 기업들은 시장점유율이 감소세를 보이고 있다(단, 중국 SMIC는 예외).

2. 주요 파운드리 기업 현황

가. 대만 TSMC

글로벌 파운드리 1위 기업인 TSMC(창립: 1987년, 본사: 대만 신주과학공원)의 현황을 보다 효과적으로 설명하기 위하여 제공하는 파운드리 서비스, 팹 운영 현황, 매출 등 영업 분석, 3나노 공정 기술, 그리고 기타 사항(R&D 포함)으로 나누어 순서대로 서술하기로 한다.

TSMC가 제공하는 파운드리 서비스는 CMOS 로직, 혼합 신호(Mixed-Signal), RF, 임베디드 메모리, BiCMOS(Bipolar Complementary Metal Oxide Semiconductor) 혼합 신호 등의 제조 공정을 포함한 포괄적 범위의 웨이퍼 제조 공정이다. 또한, 설계, 마스크 제작, TSMC 3DFabric4) 첨단 패키징 및 실리콘 스태킹 기술, 테스팅 서비스도 제공한다. 주요 고객사는 AMD, AWS, 브로드컴, 인피니온, 인텔, 미디어텍, 엔비디아, NXP, 퀄컴, 소니 등이다[8].

2024년 2월 말 기준, TSMC와 자회사들은 총 18개의 팹을 운영하고 있다. 보다 구체적으로는 150mm(6인치) 웨이퍼 팹 1개, 200mm(8인치) 웨이퍼 팹 6개, 300mm(12인치) 웨이퍼 팹 6개, 그리고 5개의 첨단 백엔드 팹을 운영하고 있다. 이를 지리적으로 살펴보면 본사가 위치한 신주과학공원에 8개, 중부 대만 과학공원에 2개, 남부 대만 과학공원에 4개의 팹이 위치하고 있으며, 해외에는 미국(1개), 중국(2개), 일본(1개)에 팹이 있다. 2023년 기준, TSMC의 연간 커패시티는 12인치 동등 기준으로 환산하면 약 16백만 웨이퍼 수준이다.

TSMC의 2023년 연간 매출은 2,161,736백만 NTD(69,300백만USD)였고 매출총이익률(Gross Profit Margin)5)은 54.4%를 기록하였다. 2023년 기준으로, 웨이퍼 매출이 기업 매출의 대부분(87%)을 차지하고 있으며, 그 중, 7나노 이하의 선단 공정이 웨이퍼 매출의 58%를 차지하였다. 이는 2022년도의 53%(2021년도의 50%)에 비해 5%(8%)만큼 증가한 수치로서 웨이퍼 매출에서 선단 공정이 차지하는 비중이 지속적으로 증가하고 있음을 나타낸다.

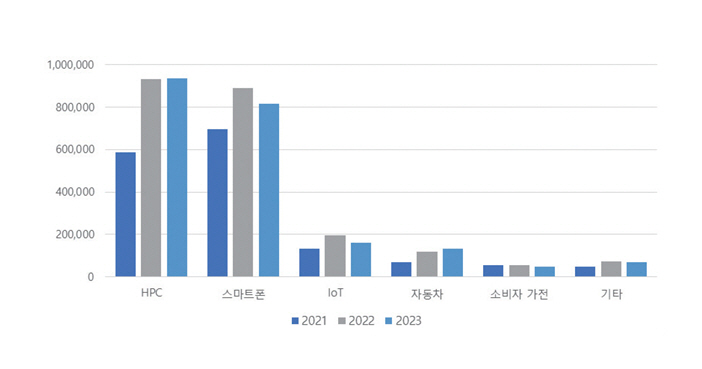

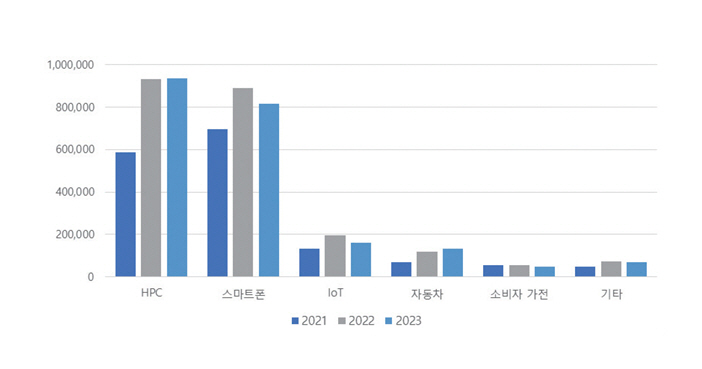

연도별 매출을 플랫폼별로 나누어 살펴보면 AI반도체가 포함된 HPC(High Performance Computing) 플랫폼 분야의 매출이 2022년부터 스마트폰 플랫폼 분야를 제치고 1위를 기록하고 있다(그림 2)[8]. HPC 플랫폼과 스마트폰 플랫폼은 선단 공정과 첨단 패키징 기술을 특히 많이 활용하는 분야이다(자동차 플랫폼과 IoT 플랫폼 분야도 선단 공정을 일부 이용).

현재 TSMC가 칩 양산에 사용하고 있는 가장 진보된 기술은 3나노 핀펫 공정이다(남부 대만 과학공원에 위치한 팹 18이 핵심적인 3나노 생산시설). TSMC는 3나노 핀펫 공정(N3)을 2022년부터 칩 양산에 활용하기 시작했으며 N3에 이어 더 나은 전력, 성능 및 밀도를 위해 향상된 3나노 공정인 N3E와 N3P를 출시했다. 또한, 다양한 고객 요구를 충족하기 위해 3나노 공정 기술을 지속적으로 확대하고 있는데 여기에는 HPC 애플리케이션에 맞춤화된 공정인 N3X와 최첨단 실리콘 기술에서 자동차 애플리케이션을 조기에 시작할 수 있는 N3AE도 포함된다[9].

TSMC는 2023년에 182,370백만NTD(5,956백만 USD)를 연구개발에 투자했는데 이는 매출의 8.5%에 해당한다. 연구개발은 주로 첨단 공정 기술 개발을 통해 선도 기업 지위를 유지하는데 많이 투자하고 있으며 성숙 기술 제공을 위한 분야에도 계속 투자하고 있다.

한편, TSMC는 성장 과정에서 Grand Alliance와 OIP(Open Innovation Platform)를 통해 각 분야의 전문기업들이 마치 하나의 기업처럼 협력할 수 있는 생태계를 구축하였다[10]. Grand Alliance란 반도체 혁신 가속화를 목적으로 한 수요기업(팹리스), EDA(Electronic Design Automation) 파트너, IP 파트너, 주요 장비 및 재료공급업체와의 협업체계를 의미한다. 2008년에 처음 발표된 OIP는 Grand Alliance의 핵심으로 팹리스와 파트너사(EDA/IP)의 창의적인 사고를 결합하여 설계 시간, 양산시간 및 출시 기간 단축에 중점을 둔 개방형 혁신 플랫폼을 의미한다. 홈페이지에 게시된 자료에 의하면, 현재 OIP에 참여하고 있는 EDA 파트너사는 16개이며 IP 파트너사는 39개이다.

나. 한국 삼성전자

삼성전자는 2005년부터 파운드리 사업을 시작하였으며, 2017년 5월에 이루어진 DS 부문 조직 개편을 통해 시스템LSI사업부에서 독립한 독자적인 파운드리 사업부를 신설하였다. 삼성전자 파운드리 사업부는 시스템반도체를 위탁생산하는 사업부로 첨단공정 기술을 통해 글로벌 팹리스 고객을 위한 칩 생산뿐만 아니라 라이브러리/PDK(Process Design Kit)/설계 방법/설계 서비스 등의 설계 인프라를 통해 솔루션까지 제공하는 토탈 파운드리를 지향한다.

삼성전자 파운드리 사업부는 국내 3곳(기흥, 화성, 평택)과 미국 오스틴에 팹을 보유하고 있다(미국 테일러 팹은 건설 중). 기흥 캠퍼스의 경우 6라인(8인치)과 S1라인(12인치)이, 화성 캠퍼스의 경우 S3라인(12인치)이, 평택 캠퍼스의 경우 S5라인(12인치)과 및 S6라인(12인치)이, 오스틴 팹의 경우 S2라인(12인치)이 위치하고 있다. 선단 공정은 평택 캠퍼스 S5라인 및 S6라인과, 화성 캠퍼스 S3라인의 일부에서 이루어진다[11].

삼성전자 파운드리 사업은 2022년 글로벌 시장점유율 12.6%를 기록하였으나, 최근에는 하락세를 거듭하고 있다. 글로벌 시장조사 업체 트렌드포스의 집계에 의하면, 2023년에는 11.3%대였고 ’24년 3분기에는 9.3%대까지 추락했다. 점유율 하락의 가장 큰 원인은 세계 최초로 GAA(Gate All Around) 구조를 도입한 3나노 공정에서의 낮은 수율 때문이라고 지적되고 있다. 이로 인한 막대한 영업손실을 낮추고자 평택 캠퍼스 파운드리 생산라인 중에서 일부 선단 공정 설비의 가동을 중단하였다[12]. TSMC 대비 레거시 공정이 부족한 점도 삼성 파운드리 사업의 문제점으로 거론되고 있다.

한편, 삼성전자는 2018년도에, TSMC의 OIP를 벤치마킹하여 SAFE(Samsung Advanced Foundry Ecosystem)라는 자체 파운드리 생태계를 출범시켰다. SAFE 생태계에 참여하는 파트너사의 개수는 충분하지만, 보유하고 있는 설계자산(IP)이 부족하다는 점이 약점으로 지적되고 있다[13].

다. 중국 SMIC

SMIC는 2000년에 창립된 순수 플레이 파운드리 기업으로 중국 정부의 대폭적인 지원에 힘입어 자국 시장을 중심으로 꾸준한 성장을 거듭한 결과, 미국 GlobalFoundries와 대만 UMC를 제치고 2024년 1분기부터 글로벌 순위 3위로 부상하였다(표 1 참고). 상하이에 본사를 두고 있으며 고객들에게 로직 IC, 전력/아날로그, 고전압 드라이버, 임베디드 비휘발성 메모리, 비휘발성 메모리, 혼합 신호/RF 및 CMOS 이미지 센서 등의 기술 플랫폼에 적용되는 8인치 및 12인치 웨이퍼 파운드리 서비스를 제공한다. 이외에도 설계 서비스, IP 지원, 포토마스크 제조 등에서 원스톱 지원 서비스를 제공하고 있다[14].

SMIC는 8인치 팹 3개(텐진, 상하이, 선전), 12인치 팹 4개(베이징(2), 상하이, 선전)를 운영하고 있다6)[15]. 이 팹들은 모두 28나노 이상의 레거시 공정용이며 용량 확대를 위해 새로 건설 중인 4개의 12인치 팹들(베이징, 상하이, 텐진, 선전)도 모두 레거시 공정용이다(2025년 이후 운용 개시 예정). 외견상 SMIC는 성숙 공정을 이용한 파운드리 서비스 제공에 주력하고 있다.

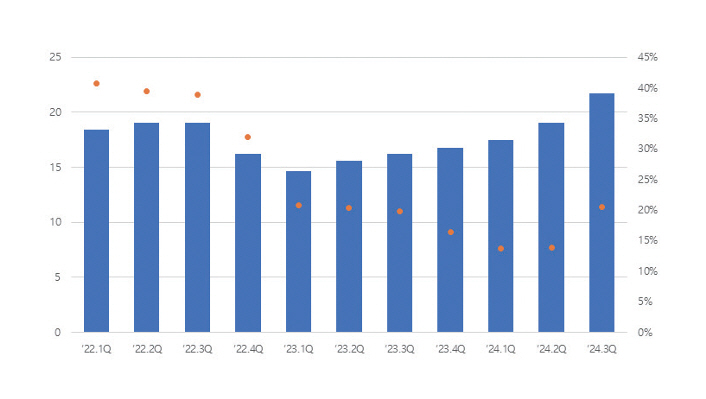

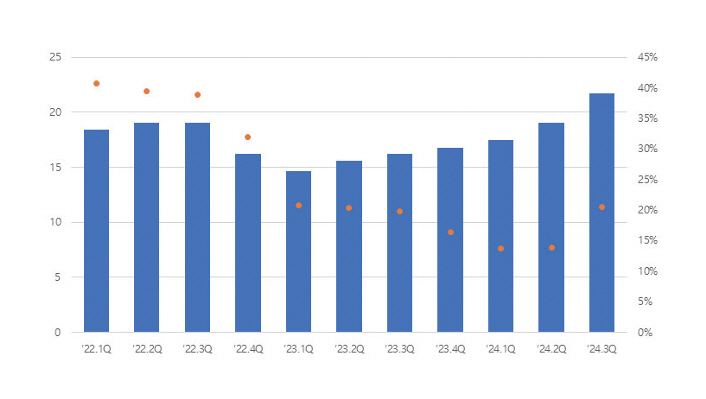

SMIC의 매출은 반도체 산업 불황기였던 2023년을 제외하고는 지속적으로 증가하는 추세를 보인다. 특히 2024년 3분기 매출은 그림 3에 나타난 바와 같이 21.7억USD를 기록하여 전년 동기 대비 34% 증가하였다(웨이퍼 매출은 38% 증가했으며 12인치가 웨이퍼 매출의 78.5%를 차지). 2024년 3분기 매출 총이익률은 20.5%를 기록하여 2023년 동기(19.8%)와 유사한 수준을 보였지만, 2022년 동기(38.9%)에는 크게 미치지 못하였다 못하였다[16]. 2023년 이후 매출총이익률의 저하는 무리하게 7나노 제품을 생산하면서 수익성이 악화된 것으로 추정된다[17].

2023년 연차보고서에 따르면, 매출의 80%는 중국 본토에서 이루어졌으며 이어 미주 지역에서 16%가 발생하였다. 매출의 대부분을 차지하는 웨이퍼 매출의 경우 응용분야별로 스마트폰(27%), 컴퓨터 및 태블릿(27%), 소비자 가전(25%), 커넥티비티 및 IoT(12%) 등으로 구성된다[14].

한편, SMIC의 대외 환경에서 가장 큰 리스크는 지정학적 갈등에 따른 미국의 제재이다. 2020년 12월에, 미국 정부는 국가 안보 및 외교 정책상의 이유로 화웨이, SMIC 등을 Entity List에 추가하여 수출 관리 규정(EAR: Export Administration Regulation) 적용을 받도록 했으며, 2022년 10월에는 EAR을 대폭 개정하여 14나노 이하 공정에서 사용되는 반도체 생산 장비의 중국 수출을 크게 제한(실질적으로 금지)하였다7). 이러한 제재에 맞서 SMIC는 주로 레거시 공정의 생산능력을 확대하고 자국 기업과의 협력 강화를 통한 내수 시장 확대에 주력해왔다.

Ⅳ. 글로벌 파운드리 기업의 주요 이슈별 대응 동향

1. 보조금 정책과 생산시설 확대

미국, 유럽, 일본, 중국, 대만 등 세계 각국에서 반도체 칩 제조를 위한 인센티브 정책이 추진되면서 이에 발맞추어 주요 파운드리 기업들은 생산시설을 확대하고 있다. 각국의 인센티브 정책은 표 2에 나타난 바와 같이 제조시설에 대한 직접 보조금 제공이 핵심이다. 특히 TSMC를 비롯한 대만 파운드리 기업들과 SMIC를 비롯한 중국 파운드리 기업들의 생산시설 확대 움직임이 활발하다.

표 2 주요국의 칩 제조를 위한 인센티브 정책 요약

TSMC는 대만 신주과학공원 내 바오산(팹 20), 미국 애리조나주 피닉스(팹 21), 대만 가오슝(팹 22), 일본 구마모토(팹 23), 그리고 독일 드레스덴(팹 24)에 새로운 팹을 건설하였거나 건설 중이다8). 12~28나노 공정을 제공하게 될 팹 23의 P1은 2024년 2월에 개소식을 열었고 2나노 공정을 제공하게 될 팹 20의 P1 및 P2는 2024년 4월에 툴인(Tool-in)을 시작한 것으로 알려져 있다9). 이외에 대만 3위의 파운드리 기업인 PSMC는 중국, 인도, 일본을 포함한 여러 국가에 반도체 팹을 설립하기 위해 현지 기업과의 합작사를 설립하였다[8,20].

트렌드포스(2023.11.14.)가 집계한 바에 의하면 중국 기업들 특히 SMIC, Nexchip, Huahong Group 등은 주로 성숙 공정에 초점을 맞춘 22개의 웨이퍼 팹을 건설하고 있다. 이 중, 6개의 12인치 웨이퍼 팹은 SMIC와 그 자회사들이 건설하고 있는 것으로서 증설 용량은 웨이퍼 44.5만 장/월에 해당한다[21].

삼성전자는 2022년부터 미국 텍사스주 테일러시에 신규 팹을 건설하고 있다. 2024년말까지 공장을 건설하여 4나노 공정 가동을 시작할 예정이었으나, 2나노 공정을 2026년까지 가동하는 것으로 계획이 수정되었다10).

한편, 보스턴컨설팅그룹(BCG)과 미국반도체협회(SIA)는 미국 정부의 보조금 정책과 기업들의 적극적인 노력에 힘입어 미국에서의 10나노 이하 로직칩 생산 비중이 2032년까지 28%로 증가할 것이라고 낙관적으로 전망하였다(이에 반해 한국은 9%로 하락)[2]. 그러나 보조금 지급의 비효율성 문제 등 미국 칩스법의 경제적 효과에 대한 우려스러운 시각도 존재한다.

2. TSMC에 의한 지배력 강화와 반독점 규제 리스크

앞서 표 1에 나타난 바와 같이 글로벌 파운드리 시장에서 TSMC의 시장점유율은 이미 60%를 넘고 있다. 또한, 2024년 3분기 매출은 235억USD로서 AI칩 수요 증가 등으로 인해 전년 동기 대비 약 36% 증가하였는데 이러한 큰 폭의 매출 증가는 7나노 이하 선단 공정 특히 3나노 공정 독식에 따른 결과인 것으로 보여진다11)(3나노 공정이 TSMC 공정별 매출에서 차지하는 비중은 2023년 3분기에 6%였으며 2024년 3분기에는 20%로 증가12)[22]).

가격 책정 방식을 살펴보면 TSMC는 고객사와 특정 기간 동안의 가격을 책정하되, 시장 상황 및 기타 요인을 고려하여 해당 기간 중에 조정하기도 한다[8]. 즉, 애플이나 NVIDIA와 같이 대량으로 위탁 생산을 주문하는 고객은 보다 유리한 가격으로 파운드리 서비스를 제공받을 수 있다13). 이는 독과점 기업이 자사 이익을 극대화하기 위하여 대량 고객이나 장기고객에 대해 가격할인을 제공하는 것으로 판단할 수 있다14). TSMC는 2025년에 3나노 및 5나노 공정의 가격을 8%만큼 인상하겠다는 계획을 고객사들에 통보하였다고 알려지고 있다[23]. 이 계획이 독점 이윤을 극대화하기 위한 행동인지, 전기료 인상 등 원가 상승을 반영한 불가피한 조치인지 검토가 필요해 보인다.

한편, 미국 블룸버그 통신은 TSMC가 경쟁사들과의 시장점유율 격차를 더욱 벌려 나가면서 반독점 규제(Antitrust Regulation) 리스크가 수면 위로 떠오르기 시작하고 있다는 기사를 게시하였다[24]. 이 기사에 따르면, TSMC의 2024년 3분기 실적 발표회에서 웨이저자(C.C. Wei) 최고경영자는 반독점 규제 리스크 대응 방안에 대한 질문을 받았으며 이에 대해 그는 TSMC의 ‘파운드리 2.0’15) 개념을 소개하면서 “TSMC는 아직 지배적이지 않으며(TSMC is not dominant yet) 반독점 우려 사항도 아니다(it’s not a kind of antitrust concern)”라고 말했다는 것이다.

최근 들어 TSMC는 중국 화웨이에 공급하기 위한 AI 칩을 생산해 미국의 대중 수출 제재를 위반했는지에 대해 상무부로부터 조사받고 있다. 이 조사가 진행되는 과정에서 자칫 반독점 규제로까지 확대될 가능성도 있다. 반독점 규제는 글로벌 계약 칩 시장의 50% 이상을 꾸준히 장악해온 TSMC도 신경 쓰지 않을 수 없는 중요한 리스크다16).

3. 2나노 경쟁의 도래와 준비

2025년은 주요 파운드리 기업들이 2나노 경쟁을 본격화하는 첫해가 될 것으로 전망되고 있다. 선두 기업인 TSMC는 2나노 공정 기술 개발이 순조롭게 진행되고 있어 2025년부터 양산을 시작할 예정이다. 바오산에 위치한 팹 20과 가오슝에 위치한 팹 22가 2나노 공정을 제공하는 핵심 시설이 될 전망이다(애리조나 팹 21의 2공장은 2028년부터 2나노 공정 제공 예상).

2나노 공정(N2) 시험생산은 바오산 팹에서 2024년 중에 이루어졌으며 수율이 60%를 넘는 것으로 알려져 있다. N2 공정은 나노 시트(Nanosheet) 트랜지스터 기술을 적용했다는 특징이 있으며 밀도와 에너지 효율성 측면에서 가장 진보된 기술로 평가받는다. 주요 고객사들이 2나노 IP 설계를 이미 완료하였고 실리콘 검증을 시작한 것으로 알려져 있다[25].

또한, TSMC 측이 ‘IEDM 2024’에서 발표한 논문에 따르면 동일한 면적과 동일한 전력하에서, 3나노 대비 2나노 칩은 속도가 최대 15%, 성능은 최대 35% 개선된 것으로 알려졌다. 2나노에 적용된 주요 공정 기술로는 하이브리드 본딩 접합 배선 간격 축소, 중간 배선 공정에서의 새로운 시도, SRAM의 업그레이드 등이 꼽히고 있다[26].

외신들은 TSMC의 2나노 공정 웨이퍼 가격이 장당 3만USD를 초과하여 3나노 공정 웨이퍼의 장당 가격에 비해 50% 이상 비쌀 것으로 보고 있다. 이에 따라 2나노 공정의 첫 고객이 될 것으로 예상되어 왔던 애플은 아이폰 17시리즈에 탑재될 AP19 칩셋 생산을 N3P 공정으로 돌리게 되고, 아이폰 18시리즈에 탑재될 AP20 칩셋 생산은, 2나노 생산능력이 8배(웨이퍼 8만 장/월)로 증가하게 되는 2026년에 맡길 것으로 예상되고 있다[27]. 즉, 2나노 공정 생산 능력의 한계로 인한 높은 비용이 대형 고객들의 선택을 주저하게 만들고 있다. TSMC는 이를 해소하기 위한 목적으로 2024년 12월에 가오슝 팹의 확장(P4 및 P5) 계획을 발표한 바 있다.

삼성전자는 3나노 공정을 제공하던 화성 캠퍼스 S3 라인을 2나노 공정으로 전환하는 작업을 진행하고 있다. 당초 4나노 공정 제공을 목표로 건설을 시작했던 미국 테일러 팹도 2나노 공정 제공으로 계획을 변경하는 등 최첨단 2나노 공정에 파운드리 사업부의 역량을 집중하고 있다. 3나노 공정에서 세계 최초로 도입했던 GAA 기술에서 쌓은 노하우를 토대로 2나노 공정에서 충분한 수율을 확보하겠다는 전략이다[28].

삼성전자는 2025년 상반기에 2나노 공정을 시험 생산하고 하반기부터 양산에 들어갈 것으로 예상되고 있다. 업계에서는 삼성전자의 2나노 공정 테스트 수율이 상당히 올라왔다고 보고 있지만, 어느 정도인지 밝혀진 바가 없다. 삼성은 AI 스타트업 PFN(일본)과 자율주행 칩 설계 기업 암바렐라(미국)를 2나노 고객으로 확보했으나, 아직까지 대형 고객은 확보하지 못하고 있다. 그러나 TSMC 등 경쟁사들도 안정적인 대량생산 체제를 갖추고 있지 못하기 때문에 기회의 문은 충분히 열려 있다.

인텔은 2024년 상반기에 ‘인텔 20A’(2나노급) 양산을 목표로 하였으나, 이를 백지화하고 2025년 하반기부터 시작될 ‘인텔 18A’(1.8나노급) 양산에 집중하는 것으로 계획을 변경하였다. 인텔은 네덜란드 ASML로부터 차세대 EUV 장비(High-NA EUV)를 가장 먼저 확보하여 설치를 완료(2024년 4월)했으며, 애리조나주(팹 52 및 팹 62)와 오하이오주에 ‘인텔 18A’ 공정 제공 등을 목표로 한 첨단 반도체 시설을 건설하고 있다. 참고로 2024년에 경영 위기를 겪은 인텔은 파운드리 사업을 분사하기로 최종결정했는데, 막대한 보조금을 제공받는 대가로 지분 매각 제한 조건 등을 적용받게 된다.

한편, 일본의 대표기업 8개 사가 공동 출자하여 2022년도에 설립된 파운드리 기업 라피더스는 2027년에 2나노 공정 양산을 목표를 하고 있다(홋카이도 치토세에 IIM-1 팹 건설 중). 라피더스는 2024년 12월에 EUV 노광 장비를 반입하는 등 2나노 생산 준비에 박차를 가하고 있으며 반도체 스타트업들을 중심으로 고객 확보 전략을 전개하고 있다. 일본 니혼게이자이 신문에 의하면 2025년 4월부터 2나노 공정에서 반도체 시제품을 생산해 6월에 미국 기업 브로드컴에 공급할 예정이라고 한다[29].

Ⅴ. 결론

반도체 가치사슬에서 제조 단계를 담당하는 파운드리 기업을 둘러싼 거시적 환경변화로 인해 발생하는 여러 이슈에 대하여 업체들의 준비와 대응이 중요한 관심사로 떠오르고 있다. 이에 본고는 글로벌 파운드리 주요 기업들에 대한 현황 분석과 함께 3가지 이슈(보조금 정책과 생산시설의 확대, TSMC에 의한 지배력 강화와 반독점 규제 리스크, 2나노 경쟁의 도래와 준비)에 대하여 최근 동향을 조사하고 정리하였다.

글로벌 파운드리 10대 기업 현황을 살펴보면, 순수 플레이 파운드리 유형이 시장에서 대세를 형성하고 있다. 1위 사업자인 TSMC의 시장점유율이 60%를 넘는 등 지배력이 공고화되고 있으며 SMIC를 제외한 나머지 기업들은 시장점유율이 감소하고 있다. TSMC는 3나노 등 선단 공정 매출 증가에 힘입어 시장점유율을 확대하고 있지만, 삼성전자는 3나노의 낮은 수율과 레거시 공정의 부족으로 어려움을 겪고 있다. SMIC는 미국의 제재에도 불구하고 중국 정부의 막대한 지원에 힘입어 레거시 공정 중심의 파운드리 서비스에 주력하고 있고 시장점유율을 조금씩 늘려나가고 있다.

각국의 반도체 칩 제조 보조금 정책 시행에 발맞추어 주요 파운드리 기업들은 생산시설을 확대하고 있다. 그중에서도 특히 TSMC는 자국뿐만 아니라 해외(미국, 일본, 독일)에도 많은 생산시설을 건설하고 있다. 이 생산시설들이 성공적으로 건설되고 가동된다면 향후 TSMC의 시장점유율이 더 높아질 가능성이 있다. 이외에 대만 PSMC, 한국 삼성전자, 중국 SMIC의 생산시설 확대 움직임도 주목할 만하다.

TSMC의 지배력 강화는 시장점유율 증가추세뿐만 아니라 가격 책정 관행에서도 확인된다. 따라서 각국 경쟁 당국으로부터 반독점 조사나 규제에 직면할 리스크를 안고 있다. 이에 Foundry 2.0이라는 개념을 소개하면서 지배력 강화에 따른 독점 우려를 불식시키려고도 했다. 2나노 경쟁 시대의 도래로 인해 향후 일본 라피더스의 시장 진입, 한국 삼성전자의 절치부심이 함께 맞물린다면 경쟁이 더 치열해지고 집중도가 완화되어 각국 정부의 규제 개입이 불필요해질 가능성도 있다.

2나노 경쟁이 본격화되기 직전인 2025년 1월 현재, 기술개발과 제조시설 건설 양 측면 모두에서 TSMC가 가장 앞서 있는 것으로 판단된다. 그러나, TSMC도 아직까지 안정적인 대량생산 체제를 완비하지 못했기 때문에 경쟁기업들에도 이를 만회할 수 있는 기회가 충분히 남아있다. 안정적인 수율 확보를 통해 다양한 고객을 조기에 많이 확보하는 것이 성공을 위한 중요 관건이 될 것이다.

반도체 파운드리 주요 기업에 대한 현황 분석과 함께 이슈별 최근 동향에 대하여 정리한 본고는 이와 관련된 국내 반도체 정책, 특히 비메모리반도체 산업 육성 정책 마련에 있어 기초자료로 참고할 만 하다고 사료된다. 비메모리반도체 산업의 육성을 위해서는 생태계에서 중추적인 역할을 담당하는 파운드리 기업들의 위상 제고가 팹리스 기업의 성장과 함께 이루어져야 할 것이다. 제조시설 유치를 위한 각국의 정책을 참고하고 국내외 파운드리, 팹리스 기업들의 전략 및 동향에 대한 관찰을 잘 조합한다면 합리적인 산업 육성 방안을 마련할 수 있을 것이다.

약어 정리

ALD

Atomic Layer Deposition

ATP

Assembly, Test and Packaging

BiMOS

Bipolar Complementary Metal Oxide Semiconductor

CVD

Chemical Vapor Deposition

DMA

Digital Market Act

EAR

Export Administration Regulation

EDA

Electronic Design Automation

EDS

Electronic Die Sorting

EUV

Extreme Ultraviolet

GAA

Gate All Around

HPC

High Performance Computing

IDM

Integrated Device Manufacturer

OIP

Open Innovation Platform

OSAT

Outsouced Semiconductor Assembly and Test

PDK

Process Design Kit

PVD

Physical Vapor Deposition

SAFE

Samsung Advanced Foundry Ecosystem

각주

본고에서는 대만 PSMC를 IDM이 아닌 순수 플레이 파운드리 기업으로 분류함. PSMC가 제공하는 설계 서비스는 자체 설계 제품에 대한 것이 아니며 타사의 설계를 지원하는 서비스에 가까움

“TSMC 3DFabric”은 TSMC가 개발한 3D 및 2.5D 첨단 패키징 기술의 포괄적인 제품군을 지칭. TSMC 3DFabric은 프론트엔드 기술(SoIC 기술 제품군 포함)과 백엔드 기술(CoWos 및 InFO 패키징 기술 제품군 포함)로 구성됨

이외에도 자회사들을 통해 여러 개의 팹을 보유하고 있음. 특히 SMSC(Semiconductor Manufacturing China Corporation)를 통해 중국 내 최고 수준의 첨단 팹(상하이에 위치)을 보유하고 있으며, 이를 통해 핀펫 기술을 사용한 첨단 노드 공정 개발에 주력하고 있음(미국의 제재를 의식하여 14나노 핀펫 공정 서비스의 제공과 이 팹에 대한 정보는 SMIC 홈페이지에서 삭제됨). 즉, 화웨이의 프리미엄 스마트폰 AP(7나노 칩 ‘기린 9000S’)는 SMSC 팹의 7나노 공정(N+2)을 통해 생산된 것으로 알려짐

팹의 확장은 단계(Phase)별로 이루어지므로 P1, P2, P3 등으로 표현하며 숫자가 높을수록 공장의 확장 또는 신규 라인 추가를 의미함. 툴인은 공장의 가동을 위해 생산 장비를 반입하여 설치하고 테스트하는 것을 의미함. 팹 23의 P1에 대한 보조금으로 TSMC는 투자비의 약 절반에 해당하는 4,760억 엔을 일본 정부로부터 지원받음

테일러 팹에 대한 삼성전자의 투자 규모가 당초 계획보다 축소되면서 미국 정부로부터 받게 되는 보조금 규모는 64억USD에서 47.5억USD로 하향되었음. 이 보조금은 TSMC의 애리조나주 팹 21 건설에 따른 보조금 66억USD(+50억USD 대출)보다는 규모가 작으나 투자금액 대비 보조금 비중은 더 높은 편임

A. Thadani and G.C. Allen, "Mapping the Semiconductor Supply Chain," CSIS Briefs, May. 30th, 2023.

R. Varadarajan et al., "Emerging Resilience in the Semiconductor Supply Chain," Boston Consulting Group and Semiconductor Industry Association, May. 2024.

M. Ruberti, "The chip manufacturing industry: Environmental impacts and eco-efficiency analysis," Sci. of Total Environ., vol. 858, 2023.

정인성, "[반도체 전공정 2편] 반도체 공정 개괄과 산화," SK 하이닉스 뉴스룸, 2022. 9. 22. https://news.skhynix.co.kr/post/jeonginseong-column-oxidation

삼성전자 반도체, "[반도체 백과사전] 반도체 8대 공정 한눈에 보기!," 2020. 1. 16. https://semiconductor.samsung.com/kr/support/tools-resources/fabrication-process/semiconductor-encyclopedia-the-eight-essential-semiconductor-fabrication-processes-at-a-glance/

전병수, "[단독] 삼성전자, 파운드리 생산라인 줄줄이 ‘셧다운’…설비투자도 보류," 조선비즈, 2024. 9. 27. https://biz.chosun.com/it-science/ict/2024/09/27/N6JYB4I535BYHDUSXNZBBSCN5E/

이진솔, "삼성 파운드리 ‘약점’ 설계자산…TSMC와 10배 격차 좁힐까," BLOTER, 2023. 6. 18. https://www.bloter.net/news/articleView.html?idxno=602758

최유식, ""화웨이는 돈 태우는 블랙홀"…中 SMIC, 물량대다 ‘실적 쇼크’," 조선일보, 2024. 5. 19. https://www.chosun.com/international/china/2024/05/19/KFIUVQRYZRFYPFUGZNDRCQ2TNA/

Taipei Representative Office in Singapore, "Taiwan and the Global Semiconductor Supply Chain-Europe’s Semiconductor Industry," Sep. 2024.

Taipei Representative Office in Singapore, "Taiwan and the Global Semiconductor Supply Chain-Japan’s Semiconductor Industry," Jul. 2024.

Taipei Representative Office in Singapore, "Taiwan and the Global Semiconductor Supply Chain: 2023 in Review," May. 2024.

TrendForce, "China’s Wafer Fabs Hits with Future Expansion 32, Mainly Targeting on The Mature Process," Nov. 14th, 2023, https://www.trendforce.com/news/2023/11/14/a-closer-look-at-chinas-dynamicwafer-foundry-landscape-current-44-with-futureexpansion-of-32/

김철문, "‘주문 폭주’ 대만 TSMC, 주력 3나노·5나노 가격 8%씩 인상," 연합뉴스, 2024. 8. 8. https://www.yna.co.kr/view/AKR20240808074100009

D. Wu, "TSMC’s Dominance is Starting to Worry More Than Just Rivals," Bloomberg, Oct. 21th, 2024. https://www.bloomberg.com/news/newsletters/2024-10-21/tsmc-s-dominance-is-starting-to-worry-morethan-just-rivals

강해령, "TSMC, 니가 그렇게 2나노를 잘해? [강해령의 하이엔드 테크]," 서울경제, 2024. 12. 31. & 2025. 1. 2. https://m.sedaily.com/NewsView/2DIC2NV3Z0#cb

TrendForce, "Apple may delay adopting TSMC’s 2nm node until its capacity grows eightfold in 2026," Dec. 30th, 2024. https://www.trendforce.com/news/2024/12/30/news-apple-may-delay-adoptingtsmcs-2nm-node-until-its-capacity-grows-eightfoldin-2026/

이나리, "삼성전자-TSMC, 25년 2나노 시대 개막…수율이 핵심," ZDNET Korea, 2024. 12. 29. https://zdnet.co.kr/view/?no=20241224192536

최인준, "日 반도체 라피더스 2나노 전쟁 뛰어드나…美 브로드컴에 시제품 칩 공급하기로," 조선일보, 2025. 1. 10. https://www.chosun.com/economy/tech_it/2025/01/09/XHREFEGEPVD6FHXSL25BTG6EB4/

표 1 글로벌 파운드리 10대 업체의 매출 및 시장점유율

주) 순위는 2024년 3분기 기준, 매출 단위는 백만USD, ( )는 시장점유율

출처 Reproduced with permission from https://datatrack.trendforce.com/Chart/content/95/global-foundries-revenue

표 2 주요국의 칩 제조를 위한 인센티브 정책 요약

- Sign Up

- 전자통신동향분석 이메일 전자저널 구독을 원하시는 경우 정확한 이메일 주소를 입력하시기 바랍니다.