정승호 (Jung S.H.)

강도욱 (Kang D.W.)

문성빈 (Moon S.B.)

박성천 (Park S.C.)

I. 서론

이론적으로 대두되던 하드웨어 공급망에 대한 공격이 현실화되어 일상을 위협하고 있다.

2025년 5월, 로이터는 보도[1]를 통하여 중국에서 납품된 풍력발전기들에 문서에는 없는 통신 장비가 존재하고, 이들이 킬스위치로 작용할 수 있다는 것을 보도하였다. 또한, 이스라엘의 정보특수작 전국은 헤즈볼라를 상대로 HW 공급망을 탈취하고 본인들의 폭발물을 심은 호출기들을 배포함으로써 심각한 인명피해를 일으키는 테러를 2024년도에 감행하였다[2,3]. 이러한 세태로 인하여, 하드웨어 공급망 보안의 중요성은 크게 대두되고 있다.

그중에서도 반도체는 다양한 응용 분야에서 핵심적인 역할을 하기 때문에 공급망 전반에서 안전성을 확보하는 것이 필수적이다. 그러나, 반도체 공급망은 설계에서 제조에 이르는 밸류체인이 분업화되어 있고, 글로벌 분산으로 인해 공급망 보안 위협이 증가하고 있다. 특히, 하드웨어 트로이목마(HT: Hardware Trojan)는 악의적인 목적으로 은닉되어 하드웨어 공급망 보안에 매우 치명적인 위협이 되고 있다.

반도체에 삽입된 HT는 특정 조건에서 활성화되며, 전력 소모, 면적 등의 물리적 특성을 거의 변화시키지 않기 때문에 전통적인 테스트나 품질 검사로는 탐지하기 어렵다[4-6]. 이로 인해 반도체에 삽입된 HT는 단순한 불량 칩의 문제가 아닌 공급망 전체의 보안 결함 차원으로 확대된다.

반도체 생산 과정에서 제3자 IP(3PIP: Third-party Intellectual Property), 설계, 제조 테스트, 조립 등의 분절된 다양한 단계에서 공격자가 개입할 수 있는 점에서, 단계 내부 공격자, 단계 전후 공격자와 같은 각기 다른 공격 모델이 존재하고 이러한 위협에 대응하기 위해 반도체의 HT 탐지 방법에 대한 연구 필요성이 높아졌다[4,7,8].

반도체 HT의 탐지 방법은 크게 두 가지 범주로 구분된다. 반도체 제조 이후 단계에서 탐지하는 포스트-실리콘(Post-Silicon) 탐지 방법과 제조 이전 단계에서 탐지하는 프리-실리콘(Pre-Silicon) 탐지 방법이다[9]. 포스트-실리콘 탐지 방법은 제조된 반도체를 대상으로 HT의 존재 여부만을 탐지하는 방법으로 탐지된 HT를 제거하거나 보안 패치하는 것이 불가능하여 재설계해야 하는 막대한 손실이 발생한다. 따라서 제조 이후가 아닌 설계 단계에서부터 적용할 수 있는 프리-실리콘 탐지 방법이 주목받고 있다[10,11].

프리-실리콘 탐지 방법의 장점은 반도체를 제조하지 않고 설계 과정에서 HT를 탐지하므로 회로 수정이 가능하다는 것이다. 해당 특징은 HT 탐지 및 방지를 동시에 가능하게 만들어 보안상 큰 이점을 제공한다. 이러한 이유로 최근 연구들은 반도체의 논리 회로 수준에서 HT를 탐지하는 기법 연구에 관심이 증가하고 있다. 또한, 머신러닝, 정적 분석, 그래프 기반 모델 등의 분석 기술을 프리-실리콘 탐지 방법에 적용하는 연구가 활발하다[12-14].

본고에서는 프리-실리콘 단계에서의 하드웨어 트로이목마 탐지 기술 동향을 고찰하고자 한다. Ⅱ장에서는 반도체 공급망 전반에서 발생할 수 있는 공격 시나리오와 보안 위협을 분석하고, Ⅲ장에서는 프리-실리콘 단계에서 HT 탐지 기술에 대한 최근 연구 동향을 소개하고, Ⅳ장에서는 연구 방향성을 제시한다. 마지막으로 Ⅴ장에서 결론을 다룬다.

II. 반도체 공급망 공격 사례 및 시나리오

1. 반도체 공급망 공격 사례

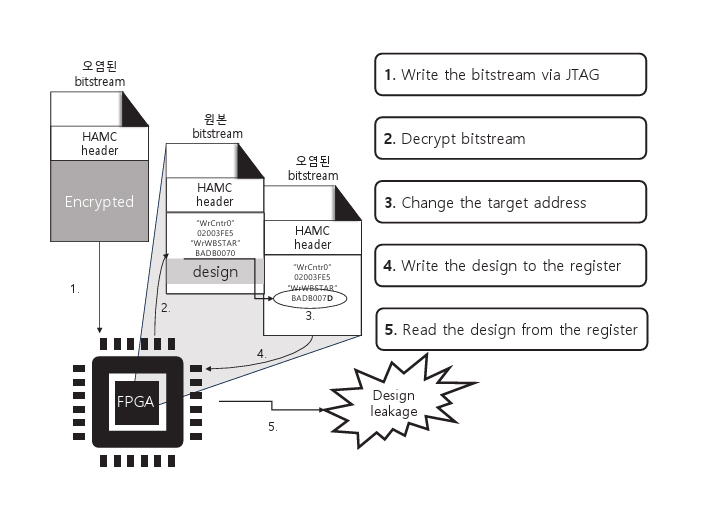

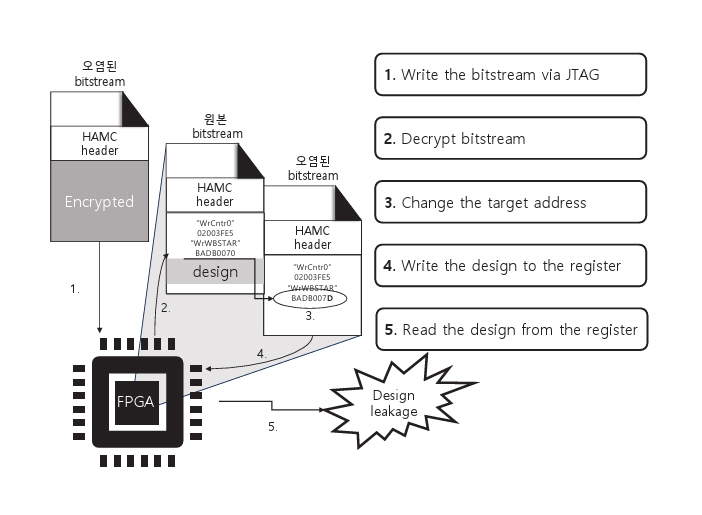

연구자들은 2022년, ECO(Engineering Change Order) 기법을 활용하여 칩이 제조 공정에 들어가기 이전의 설계 단계에서 HT를 삽입하는 공격이 가능함을 실험적으로 입증하였다[15]. 또한, 2018년도에 열린 Black Hat에서는 VIA C3 칩의 문서에는 존재하지 않는 루트 권한을 탈취하는 백도어가 있는 것이 밝혀졌다[16]. 같은 해 보도된 “The Big Hack” 사건[17]은 중국 제조 공장에서 Supermicro 서버 메인보드에 정보 유출을 목적으로 하는 초소형 칩이 은밀히 실장되었으며, 해당 제품이 애플과 아마존 등 주요 기업에 납품되었다는 내용을 담고 있다. 이처럼 반도체 공급망을 악용한 공격은 단순한 이론적 가능성을 넘어서 현실적인 위협으로 대두되고 있으며, 그 범위 또한 설계 단계에서부터 최종 제품 유통에 이르기까지 전 과정을 포괄한다. 이러한 반도체 공급망 기반 공격 사례 중 하나로 Starbleed[18]가 있으며, 광범위하게 유통된 FPGA(Field Programmable Gate Array) 제품을 대상으로 비트스트림 변조를 통해 암호화된 설계 로직을 복호화하고, 프로그래밍된 디자인을 유출하였다.

공격자는 Xilinx 7 시리즈 FPGA의 JTAG(Joint Test Action Group) 인터페이스를 통해 조작된 비트스트림을 FPGA에 주입함으로써 공격을 수행한다. 비트스트림은 AES-CBC-256 방식으로 암호화되지만, 공격자는 복호화 과정 중 특정 위치의 값을 의도적으로 플립(Flip)시키기 위해 연산에 값을 추가함으로써 명령어의 동작을 제어한다. 변조된 비트스트림의 헤더는 시스템이 재부팅되더라도 지워지지 않는 레지스터에 복호화된 상태로 기록되도록 하며, 이후에 레지스터를 읽어 들이도록 비트스트림을 만들어 원본에 해당하는 비트스트림을 복호화된 상태로 획득하게 된다(그림 1).

사례를 통해 반도체 공급망 측면에서 시사하는 바는 두 가지로 정리할 수 있다.

첫째, 반도체를 설계하는 과정은 설계 도구 사의 제품 및 시뮬레이션 도구를 활용하는 것이 강제되지만, 이러한 타사의 제품들이 설계자의 디자인에 대한 보호 및 기밀성을 담보하지 않는다.

둘째, 반도체를 설계하는 과정에서 IP를 수급해 통합하여 비트스트림을 전달한 경우, Starbleed와 같은 공격으로 인하여 반도체의 핵심 자원이 의도하지 않게 외부로 유출될 가능성이 존재하고 이는 설계 단계에서부터 정보 보안 위협이 발생할 수 있음을 의미한다.

설계 단계에서 직면할 수 있는 대표적 위협은 3PIP를 도입하고 통합하는 과정에서 사용자가 인지하지 못한 채 HT가 은밀히 삽입되는 경우이다. 일반적으로 3PIP 수급 과정에서 암호화된 RTL(Register Transfer Level)코드가 전달되기 때문에, 3PIP 사용자 입장에서는 코드 수준에서 HT 여부를 검증할 방법이 없다. 이러한 3PIP의 블랙박스 특성은 IP들을 통합하는 단계에서 인지하지 못한 HT가 삽입될 여지를 남긴 채로 제품화된다는 심각한 문제점이 있다. 반도체 공급망을 대상으로 하는 공격은 설계 초기 단계에서부터 HT를 삽입하는 것으로 공격면이 확장되고 있어서 HT 탐지 방법 또한 방어면을 확장하여 연구할 필요가 있다.

2. 반도체 공급망 공격 시나리오

공격자는 반도체를 설계에서 제조에 이르는 과정에서 악의적인 수정을 하는 HT를 삽입함으로써, 반도체의 기능 변조, 성능 저하, 정보 유출, 서비스 거부 등의 악성행위를 유도할 수 있다.

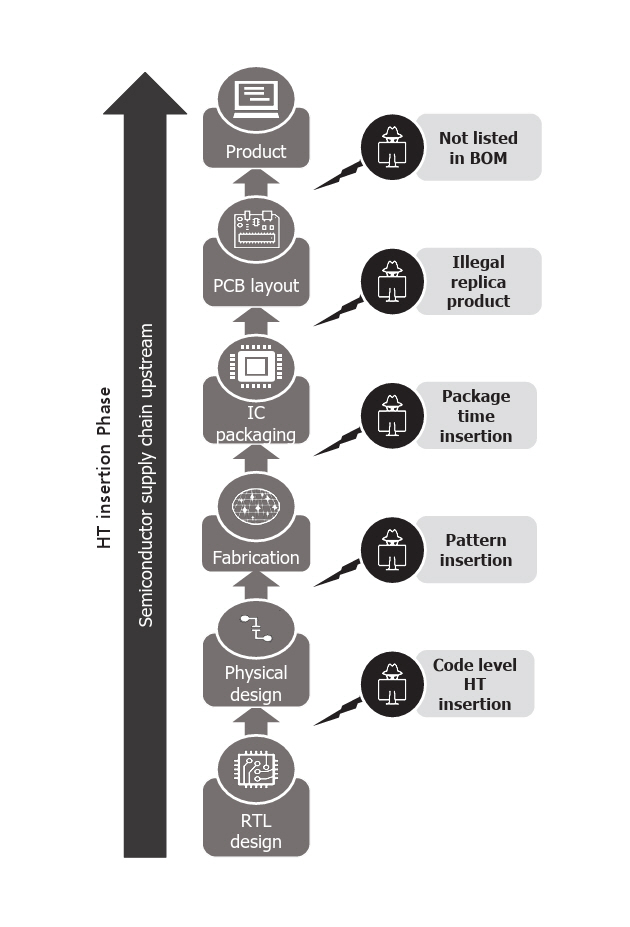

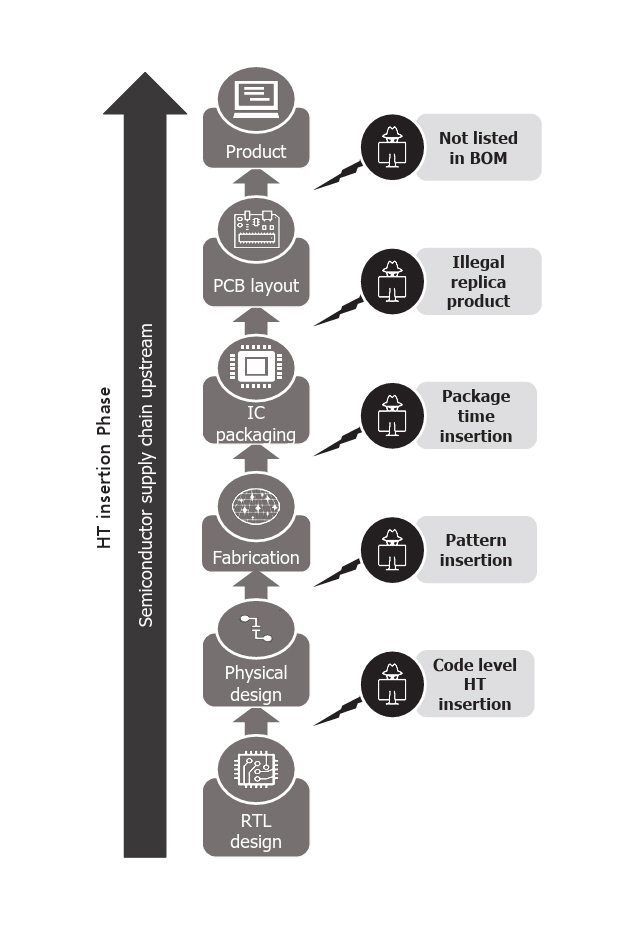

그림 2와 같이 반도체 설계(Design)단계는 HT가 삽입될 수 있는 핵심 구간으로, 시스템 수준 요구사항이 구체적인 회로 구조로 구현되는 과정이다. 이 단계에서는 3PIP, 자체 구현 HDL코드, 논리 회로 합성 및 시뮬레이션 도구 등이 사용되어 공격자는 HT를 삽입할 수 있는 공격면이 넓다.

내부자 위협(Insider Threat)은 조직 내부에서 권한을 가진 인원이 의도적으로 악의적인 행위를 수행하는 경우를 말한다[19]. 반도체 기업의 내부자가 위협을 행사하게 되면, 설계 초기 단계부터 HT를 삽입할 수 있으며, 이는 Cyber Security 관점에서 코드 삭제, 악의적인 코드 삽입, 취약 코드로의 업데이트 등 소프트웨어에서 행해지는 공격들과 유사한 개념으로 이해될 수 있다[19]. 반도체 설계 단계에서 HT의 삽입은 프로토콜 변경, 제약 조건 수정, 논리 게이트 추가 또는 수정 등 다양한 방식으로 이루어질 수 있으며, 이는 추상화 수준에 따라 시스템 레벨, RTL, 게이트 레벨, 배치 배선 레벨까지 광범위하게 발생할 수 있다. 반도체 설계 및 제조 과정을 단계별로 살펴보면 다음과 같다(그림 2).

1. RTL Design 단계: RTL 설계를 진행하고, 시뮬레이션 기반의 기능 검증

2. Physical Design 단계: PPA(Power, Performance, Area) 등의 제약을 고려하여 P&R(Place & Routing)을 통해 로직 게이트를 GDS II 파일 포맷의 물리적 패턴화

3. Fabrication 단계: 물리적 패턴 데이터를 파운드리에서 실리콘 웨이퍼로 제작

4. Packaging 단계: 웨이퍼를 절단하고 절단된 개별 다이들을 패키지의 I/O 핀에 연결하여 밀봉

5. PCB 조립 단계: 제작된 반도체 칩을 PCB에 탑재

반도체 공급망의 분절된 전체 과정에서 각 분절에서 내부 공격으로 분화할 수 있는 공격자에 의한 HT 삽입 가능성은 그림2와 같이 분포하며 분절마다 가능한 공격 시나리오는 표 1과 같이 존재한다.

표 1 반도체 개발 단계별 HT 삽입 시나리오

| 단계 | 가능한 공격 기법 |

|---|---|

| RTL design | • IP 설계자 혹은 통합자에 의한 악의적인 행위의 RTL HT 삽입[10,12,22-27] |

| Physical design | • 패턴 삽입 기법인 ECO를 이용한 물리적 패턴 HT 삽입[15] |

| Fabrication | • Package-time insertion 등을 통한 HT 삽입 |

| • chiplet 구조 변형 및 비인가된 초소형 칩 병합[20] | |

| Packaging | • 미승인한 과생산 및 복제품을 통한 공급망 공격 |

| PCB 조립 | • PCB에 실장하는 과정에서는 BOM(Bill of Materials)에 명시되지 않은 반도체 탑재[17] |

단계별 공격 위협에 따라, HT를 탐지하고 방지하기 위한 다양한 연구가 진행되어 왔다[10,12,20,22-27]. 그러나, 대부분의 기존 탐지 방법은 반도체가 제조된 이후인 Fabrication 단계부터 탐지에 초점을 맞추고 있어서, 반도체 설계 단계의 새로운 HT에 대해 유연하게 대응하기 어렵다는 한계가 있다. 이에 따라, 칩 설계 초기 단계에서 HT를 탐지할 수 있는 기법의 중요성이 대두되고 있으며, Ⅲ장에서는 반도체 설계 단계에서 HT 탐지 방법들을 고찰해 본다.

III. 설계 단계에서 HT 탐지 기술

1. 스위칭 기반 부채널 탐지 방법

설계 단계에서부터 실제로 전류를 흘려보내 전력을 측정하는 것은 불가능하다. 그러나, 스위칭 활동량은 실제 회로에서의 전력 소비와 비례 관계가 있기 때문에 설계 단계에서 의미가 있는 추정 지표가 될 수 있다. Huang 등[21]은 넷리스트 단계에서 부채널 분석을 사용하여 HT 탐지를 위한 테스트 벡터를 생성하는 프레임워크인 MERS(Multiple Excitation of Rare Switching)를 제안한다. HT 회로는 일반적으로 희귀한 조건에서만 활성화되기 때문에, 이를 유도하는 테스트 벡터 없이는 부채널 기반 탐지가 어렵다. MERS는 회로 내에서 희귀하게 스위칭되는 내부 노드인 희귀 노드를 찾고, 이 노드들의 스위칭을 반복적으로 유도할 수 있는 테스트 벡터를 자동으로 생성한다. 희귀 노드가 일정 횟수 이상 스위칭되도록 통계적 기법을 사용해 벡터를 구성하며, 생성된 벡터는 불필요한 스위칭을 줄이기 위해 해밍 거리 기반(MERS-h) 또는 시뮬레이션 기반(MERS-s)으로 재배열한다. 이를 통해 희귀 노드에서 발생하는 HT 유발 스위칭 신호의 강도를 높인다. 이 방식은 HT의 위치나 구조에 대한 정보 없이도 적용 가능하며, 랜덤 대비 탐지 민감도 향상을 보였다.

또한 사전 설계 단계에서 보안 취약성을 탐지하도록 RTL 수준에서 탐지 방법을 제안한 논문도 발표되었다[10,11,22].

Zhang 등[10]은 RTL에서 전력 부채널 누출을 효율적으로 평가하기 위한 PSC-TG(Power Side-Channel Leakage Assessment with Test Pattern Generation) 프레임워크를 제안하여 포스트-실리콘 이전 단계에서 보안 취약성을 초기에 진단하고자 한다. IFT(Information Flow Tracking)를 통해 키와 데이터가 어떤 회로에 영향을 주는지 식별하고, 포멀 검증을 통해 입력 조합 중 HT의 전력 흔적이 가장 뚜렷하게 나타나는 두 가지 경우를 찾아낸다. 이 두 벡터만으로 최대 전력 차이를 유도할 수 있다. 생성된 벡터를 통해 회로 내 신호들의 스위칭 활동을 계산하고 SCV(Side-Channel Vulnerability) 지표로 정량적 평가를 수행한다. 모든 단계는 자동화되어 있어 부채널 지식이 없는 설계자도 활용할 수 있도록 설계되었다. 다양한 암호 회로에 적용한 결과, 게이트 레벨 및 FPGA 결과와 높은 상관관계를 보였다.

2. AI 기반 탐지 방법

Pan 등[23]은 HT 회로를 활성화되도록 만드는 트리거 찾는 방식에 대하여 기존 방식이 희귀 노드에 의존해서 탐색하는 것을 문제점으로 제기한다. 트리거를 활성화하는 조건을 찾기 위하여 수백만 건의 랜덤한 테스트 패턴을 만드는 것은 시간이 굉장히 오래 걸리는 것뿐만 아니라 HT를 활성화하는 것을 보장하기 어렵다. 또한, 기존의 기법들은 드물게 발생하는 신호를 기반으로 활성화되는 트리거들에 대하여 주로 탐색한다. 이러한 탐색의 문제점은 트리거가 되는 희귀한 테스트 벡터에 대한 노드에 의존하여 탐색을 진행하기 때문에 희귀하지만 HT가 아닌 노드에 대한 오탐색, 희귀하지 않은 노드에 심어진 HT에 대해서는 검출하지 못하는 문제가 발생하게 된다. 따라서 논문의 저자들은 신호 기반 탐지 모델인 SCOAP(Sandia Controllability/Observability Analysis Program)를 제시한다.

SCOAP도 희귀 노드에 대한 식별을 진행하는데 Bias를 설정하여 트리거가 되는 노드의 출력이 Bias보다 낮은 경우를 희귀 노드로 분류한다. 이러한 희귀 노드 설정은 수백만 건의 테스트 케이스에 대하여 Brute Force로 전부 대응하지 않더라도 노드의 성격을 규정하는 데 도움이 된다. 또한, 로직 게이트의 입력 및 출력 신호에 대하 모델링하고 이를 기반으로 점수체계를 마련한다.

SCOAP는 테스트벡터에 대하여 희귀 노드 판별 및 모델링을 활용하여 점수를 매기고 이를 강화학습을 통한 확률 기반으로 테스트벡터를 재생성하게 된다. 이러한 접근을 통하여 SCOAP는 기존보다 더 적은 테스트벡터를 요구하며, 신호 기반 탐지 기법을 통하여 희귀 노드 탐지 기반에서는 찾아내기 힘들었던 오탐색 문제를 해결한다.

Re-Pen[12] 역시 강화학습을 활용하여 RTL 디자인을 검증한다. 기본적인 접근 방식인 테스트벡터로 검증을 하고 이에 대한 판단을 한 뒤, 테스트벡터를 업데이트하는 일련의 과정은 앞서 소개한 SCOAP와 유사하다. Re-Pen은 CWE(Common Weakness Enumeration) 데이터베이스를 기반으로 한 보안 정책에 대한 DB를 마련하여, 이를 수식화하여 Cost Function을 만든다. 테스트벡터를 DUT에서 검증하고 이에 대한 신호들을 모니터링하여 나온 값들을 통해 Cost Function에 대입하여 테스트 벡터를 거쳐 나온 값에 대하여 평가를 하고 강화학습을 진행하게 된다. 강화학습 결과는 BPSO(Binary Particle Swarm Optimization)를 위한 여러 변수들로 처리되어 BPSO에 반영되고, 연산을 거쳐 새로운 테스트벡터가 생성되게 된다.

3. 심볼릭 실행 기반 탐지 방법

일부 논문들에서는 희귀 노드를 활성화시키기위한 방법으로 심볼릭 실행(Symbolic Execution)을 활용한다. 그중에서 SymbA[24]는 희귀한 조건에서만 활성화되는 HT를 활성화하기 위한 테스트 벡터를 생성하기 위해 RTL 설계를 C++로 변환한 후 소프트웨어 수준의 심볼릭 실행 엔진(KLEE)을 활용하는 방식을 제안한다. 먼저 RTL 코드에 실행 추적용 구문을 삽입하고, 이를 C++ 코드로 자동 변환한 후, 추적 구문을 삽입한다. 무작위 시뮬레이션을 통해 커버되지 않는 희귀 분기를 찾는다. 해당 희귀 조건들은 어서션으로 표현되어 심볼릭 엔진의 목표로 설정되고, SMT solver로 목표에 대한 해를 찾고, 도달 지점에 대한 입력 벡터가 생성된다. 이 과정을 반복하면서 트리거 조건에 해당하는 희귀 경로를 순차적으로 커버해 나간다. 이 방식은 C++ 수준의 추상화를 통해 시뮬레이션 속도를 높이고 심볼릭 실행을 통해 실행 경로를 확장하여 탐색 효율성을 높였다. 실험 결과 기존 콘콜릭 기법 및 모델 검사 기법 대비 더 많은 트리거 활성화 분기를 커버하며, 메모리 사용량과 실행 시간 면에서도 더 뛰어난 확장성을 보였다.

Ahmed 등[25]은 RTL 수준에서 HT를 효과적으로 활성화하기 위한 테스트 생성 기법으로 콘콜릭테스팅(Concolic Testing)을 제안한다. 이 방법은 콘크리트 시뮬레이션(Concrete Simulation)과 심볼릭 실행을 교차 반복하여 트리거 조건이 희귀한 HT를 탐지할 수 있게 한다. 설계에 추적용 코드를 추가하고, 랜덤 입력값을 넣어 실행 빈도가 낮은 희귀 분기와 할당문을 식별한다. 이후 타겟 중 하나가 선택되어 BFS(Breadth-First Search)를 실행하여 평가되며, 경로 제약 Solver를 통해 각 타겟 분기로 도달 가능한 테스트 벡터를 생성한다. 이 방식은 하나의 실행 경로만 탐색하므로 상태 공간 폭발 문제를 회피할 수 있고 설계 크기와 관계없이 적용 가능하다.

4. 정보 흐름 기반 탐지 방법

Nahiyan 등[26]은 자산(암호 키 등)을 SA0(Stuck at 0) 모델로 가정하고 ATPG(Automatic Test Pattern Generation) 기반의 정보 흐름 추적을 통해 HT를 탐지한다. 자산이 관측되거나 제어되면 안 되는 위치에서 정보 흐름이 확인되면 해당 경로가 HT 의심 경로로 표시된다. 비정상적인 정보 흐름을 통해 정상 경로를 우회하거나 완전히 분리된 경로를 따르는 HT를 모두 탐지할 수 있도록 설계되었다. Trust-Hub[7] 벤치마크 실험에서 높은 탐지율과 트리거 조건 역추적 정확도를 입증한다.

Farzana 등[27]은 SoC(System on Chip) 설계 내에서 보호가 필요한 2차 자산을 자동으로 식별하는 프레임워크인 SAIF(Security Asset IdentiFication)를 제안한다. 기존 방식은 암호 키와 같은 1차 자산만 보호했지만, SAIF는 1차 자산과 연관된 내부 회로 요소들도 공격 벡터가 될 수 있음을 전제로 보다 넓은 보안 커버리지를 확보한다. 먼저 자산 정보 흐름을 포괄적으로 잠적 위치를 추적하고, 1차 자산의 영향을 받는 후보 컴포넌트 목록을 추출한다. 마지막으로 Pruning과 검증을 진행하여 모든 조건을 만족하는 후보만 2차 자산으로 최종 식별된다. 이 과정을 통해 보안 검증 대상 범위를 정밀하게 확장하여 실험에서 SoC 설계에서 높은 확장성을 입증한다.

5. 기호 대수 기반 탐지 방법

Farahmandi 등[28]은 HT 탐지뿐만 아니라 위치 정보까지 탐지 가능한 방법을 제안한다. 이 방법은 게이트 레벨 IP들에서 다항식 추출을 기반으로 하는데, 회로의 골든 모델(사양)의 다항식 세트와 수정된 모델(구현)의 다항식 세트를 도출한 후 Grobner Basis 연산을 통해 두 세트 사이의 동등성을 확인한다. 만약 특정 구현 영역의 다항식이 사양 다항식과 같지 않다면, 해당 영역은 HT 존재 가능성이 있는 의심 영역으로 간주된다. 이후 동등함이 확인된 게이트들을 제외하고 나머지 의심 게이트들을 분류하여 HT 탐지 범위를 줄인다. 이렇게 분류된 소수의 게이트에 대해 ATPG 기법을 적용해 HT를 실제로 활성화할 수 있는 입력 벡터를 생성한다. 이 방법으로 기존 기법[29]보다 False Positive는 줄고 탐지 효율은 향상되었음을 보여주었다.

IV. 연구내용 소개

2024년도에 시작한 “HW 공급망의 안전성을 보장하기 위한 칩 무결성 및 시스템 보안 검증 기술 개발”은 반도체 설계의 분절화로 인하여 산개되어 있는 탐지 기술들에 대하여 일원화하여 시스템화하는 것과 정립되지 않은 HW 공급망 보안 전체 관리 체계를 수립하는 것을 목표로 시작되었다. 기존의 HW 공급망 보안 현황은 포스트-실리콘에 집중하고, 설계 단계에서의 HT 탐지 기술들은 산발적으로 존재하였다.

한국전자통신연구원에서 진행하고 있는 해당 과제는 설계–제작–조립–유통 전반에 대하여 공격 시나리오를 정의하고, 산개되어 있는 탐지 기술들을 공격 시나리오와 맞춤으로써 HW 공급망 전반에 대해서 무결성 및 시스템 검증이 매끄럽게 동작하도록 시스템화하고 있다. 이를 통해 뚜렷하게 정의되지 않은 HW 공급망 보안 체계에 대해서 포괄적으로 커버할 수 있는 기초 토대를 마련하고 후속 연구들에 대한 개념을 제공하고자 한다.

V. 결론

본고에서는 반도체 공급망에서 3PIP에서부터 통합설계와 제조로 이어지는 밸류체인 전반에 대한 분절에서의 HT 삽입 시나리오를 제시함과 동시에 최근 새로운 공격 유형에 속하는 반도체 설계 단계에서의 HT 삽입을 탐지하는 기술들에 대한 동향을 분석해 보았다.

살펴본 바와 같이 반도체 설계 단계에서의 HT 탐지 방법에 대한 연구는 아직 초기 단계로 보인다. 그러므로 설계 단계의 반도체 공급망에 은닉된 HT를 탐지 및 방지하는 실용적인 솔루션이 부재하여 사실상 HT 삽입 공격에 무방비 상태이다.

따라서 반도체 공급망의 분절들 각각에 대해서도 HT를 탐지하는 기술들은 더욱 고도화해야 하고 새로운 위협이 되는 설계 단계에서의 HT를 탐지하는 방법에 대한 연구는 물론 반도체 전반의 공급망 관점에서 안전한 3PIP 수급에서 통합 및 제조에 이르는 반도체 공급망의 무결성을 검증할 통합 솔루션과 함께 검증된 공급물을 체계적으로 관리할 수 있도록 HBOM[30,31]과 연계한 연구로 발전시키는 것이 중요하다.

용어해설

공급망 원재료의 조달부터 제품이 최종 소비자에게 도달하기까지 전체 생산 및 유통 과정을 포함하는 복합적인 흐름의 연결 구조

GDS II 집적회로(IC)의 물리적 설계 정보를 표현하기 위해 사용되는 이진 파일 형식

심볼릭 실행 프로그램의 입력값을 구체적인 수치가 아닌 추상적인 기호 형태로 대입하여 가능한 경로들을 분석하는 테스트 기법

콘크리트 시뮬레이션 실제 값(실수, 정수 등)을 입력으로 사용해 시스템이나 프로그램이 실제 상황에서 어떻게 작동하는지를 모의 실행하는 방식

밸류체인 하나의 제품이나 서비스가 만들어지고 제공되기까지 참여 기업이나 단계별 활동들이 부가가치를 더해가는 일련의 연계 과정

참고문헌

그림 1

그림 2