AI 데이터센터를 위한 CPO용 광통신부품기술 동향

Optical Component Technologies for Co-Packaged Optics in AI Data Centers

- 저자

-

이서영광통신부품연구실 sylee84@etri.re.kr 윤석준광통신부품연구실 yunseokjun@etri.re.kr 김영훈광통신부품연구실 yhk1125@etri.re.kr 안신모광통신부품연구실 shinmo.an@etri.re.kr 김덕준광통신부품연구실 djkim@etri.re.kr 김종회광통신부품연구실 djonghoi@etri.re.kr 이동훈광통신부품연구실 dhlee@etri.re.kr 한영탁광통신부품연구실 frenclin@etri.re.kr 한원석광통신부품연구실 wshan@etri.re.kr

- 권호

- 41권 1호 (통권 218)

- 논문구분

- AI 고속도로를 위한 입체통신 기술

- 페이지

- 45-59

- 발행일자

- 2026.02.02

- DOI

- 10.22648/ETRI.2026.J.410105

본 저작물은 공공누리 제4유형: 출처표시 + 상업적이용금지 + 변경금지 조건에 따라 이용할 수 있습니다.

본 저작물은 공공누리 제4유형: 출처표시 + 상업적이용금지 + 변경금지 조건에 따라 이용할 수 있습니다.- 초록

- AI data centers are experiencing explosive growth in data processing demands and power consumption, driven by large-scale AI models and machine learning workloads. Co-packaged optics (CPO), which integrates switch ASICs (Application-Specific Integrated Circuit) chips and optical engines within a single package, is emerging as a promising approach forto alleviate these challenges. By reducing the electrical–optical interconnect length, the CPO can increase the the panel port density and aggregate bandwidth while significantly reducing the the link latency and energy consumption, thereby enabling the ultra-high-speed, low-power optical interconnects required for next-generation AI data centers. This study reviews the architectural characteristics of CPO-based AI data centers in comparison with pluggable optics, LPO (Linear Pluggable Optics)/OBO (On-Board Optics) solutions, and survey keys.

Share

I. 서론

인공지능(AI)과 머신러닝(ML) 워크로드가 급증하고 대규모 모델의 훈련과 추론을 위한 전력 소모와 데이터량이 폭증함에 따라 데이터센터 네트워크의 대역폭, 시간지연 및 전력 효율 한계에 도달하였다. 최근 데이터센터는 수만 개에 이르는 GPU 및 AI ASIC이 수평적으로 연결되는 스케일아웃(Scale-Out) 네트워크 구조를 채택하면서, 컴퓨팅 간(East-West 간) 실시간 트래픽이 급격히 증가되고 있으며, 전체 트래픽 중 70~80% 이상이 데이터센터 내부, 특히 노드 간 통신에 집중되고 있다[1].

이러한 거대 클러스터 환경에서 대역폭 부족과 각 링크 간 지연, 그리고 큰 전력 소모는 서비스 품질과 경제성, 지속 가능성에 직접적인 영향을 미친다. 기존의 플러그어블 광모듈 방식을 사용한 경우, 패널 포트 밀도, 전력 효율, 시스템 설계 등 물리적 한계로 더 이상의 성능 향상이 어렵다. 따라서 데이터센터 네트워크의 확장과 최적화를 위해서는 새로운 광접속 기술과 네트워크 구조 혁신이 요구된다.

특히, 400G/800G/1.6Tbps급 고대역폭 단일 포트와 수백~수천 포트 동시 집적이 필수적인 AI 데이터센터에서, 전통적 모듈 방식은 패널 공간의 제약과 SerDes~패널부 링크의 전력 소모/지연 증가, 관리 복잡성 등으로 인해 성능 구현에 제약을 주고 있다. 이에 대한 근본적 해결 대안으로 CPO(Co-Packaged Optics) 기술이 주목받고 있다.

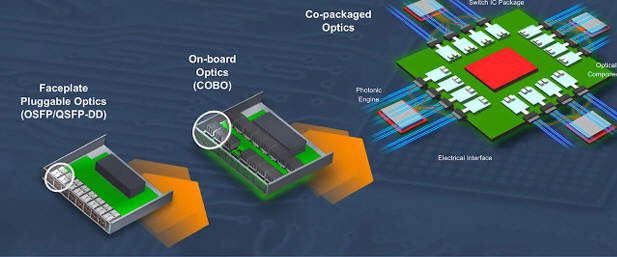

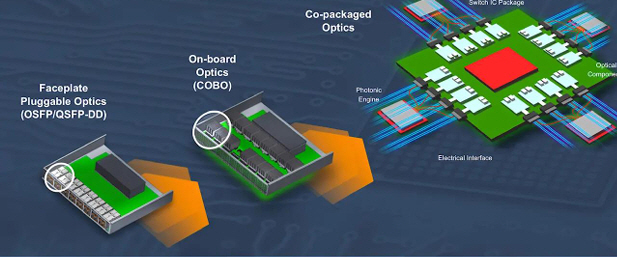

그림 1과 같이 CPO는 AI 스위치 ASIC과 광통신 엔진을 동일 패키지에 집적하여 전기-광 인터커넥트 구간을 최소화함으로써 채널 손실과 전력 소비를 획기적으로 줄이고, 패널 포트 수와 시스템 공간 사용을 크게 개선 가능하다. 실제로 CPO 기반 시스템은 플러그어블 광모듈 대비 에너지 효율이 50% 이상 향상(5~10pJ/bit), 고집적화, 저지연 구조, 중장거리 대규모 클러스터 지원 등의 다양한 부분에서 이점을 제공한다[2]. 또한, 스위치-서버-NIC 네트워크 아키텍처가 DPU, Chiplet, 다이투다이(Die-to-Die) 인터페이스 중심으로 진화하면서 CPO의 활용 범위도 다방면으로 확장되고 있다.

그림 1

플러그어블에서 CPO까지 진화

출처 ETRI Webzine, “빛을 이용한 초고속 통신의 시대를 열다,” 2023. 2. 7. https://blog.naver.com/etripr/222996077089

이러한 변화의 중심에는 IEEE의 Ethernet, OIF, COBO, UEC, UCIe, UALink 등 주요 표준화 협의체들의 활발한 활동이 있다. 특히 OIF는 2023년부터 AI 및 고성능 컴퓨팅에 특화된 Energy Efficient Interface(EEI), 3.2Tbps CPO 모듈, ELSFP(External Laser Small Form Factor Pluggable) 등 일련의 표준화 프로젝트를 진행 중이다. UEC, UCIe, UALink 등의 신생 산업 컨소시엄들도 AI/ML 트래픽 증가, 차세대 Scale-Out 트래픽 요구와 클러스터 확장성 및 시스템 범용성 측면에서 인터커넥트와 광통신 표준 개발 및 검토에 적극적으로 나서고 있다.

CPO 시장은 2025년 약 9억 5,500만 달러에서 2035년 약 12억 달러 규모로 성장할 것으로 예상되며, 연평균 성장률(CAGR)은 30%에 달한다. 네트워크 스위치 모듈 수요 확대와 함께 CPO 솔루션이 빠르게 시장을 확장할 전망이다[3]. 특히 AI 광인터커 넥트 분야가 이 성장을 주도할 것이며, 미래 데이터 센터와 고성능 컴퓨팅 분야에서도 CPO 채택이 증가할 것으로 기대된다.

이와 같은 글로벌 동향과 기술 혁신 속에서, CPO 및 관련 광부품 기술은 미래 AI 데이터센터 네트워크 경쟁력을 결정하는 핵심 요소이며, 산업 생태계 전반의 표준화와 아키텍처 혁신을 견인할 기술로 부상되고 있다.

CPO 구현에 필수적인 핵심 광부품에는 외부 광원 및 온칩 광원, 실리콘 포토닉스 기반 변조기, 고속 광검출기, 그리고 차세대 2.5D 및 3D 집적‧패키징 기술이 포함된다. 이러한 광부품은 CPO의 핵심 요소이며 데이터 전송 속도, 신뢰성, 에너지 효율성에 결정적인 역할을 하며, 궁극적으로 AI 데이터 센터 내 저전력‧초고속 광통신 구현에 있어 핵심 요소이다. 본고에서는 광부품 기술의 최신 동향과 연구 개발 현황을 집중 조명하여 AI 데이터센터 네트워크 성능 향상을 위한 기술적 토대를 마련하고자 한다[4].

II. CPO 구현을 위한 광통신 부품 기술

1. AI 데이터센터용 광모듈 기술

AI 데이터센터 광모듈 시장에서는 플러그어블 광트랜시버가 주류를 이루고 있으나, 최근 고밀도, 저지연 연결의 필요성이 높아짐에 따라 CPO 모듈이 새로운 대안으로 부상하고 있다.

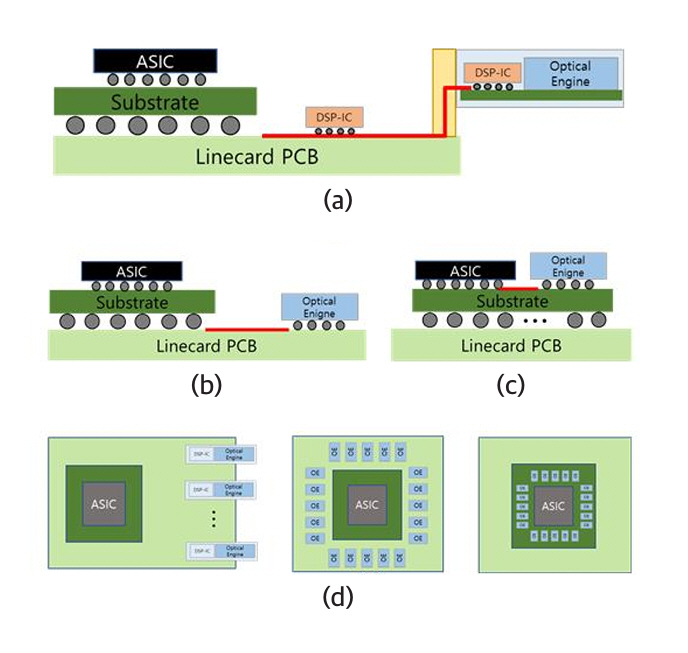

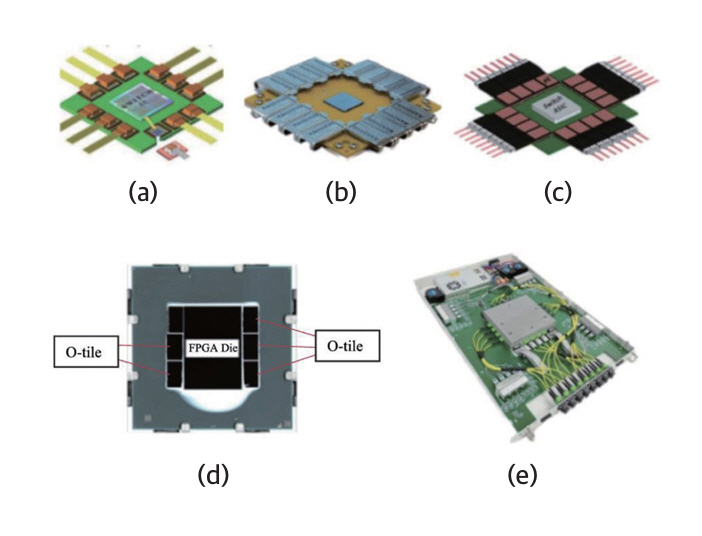

그림 2는 플러그어블 광트랜시버, OBO(On-Board Optics), CPO 모듈의 개념과 라인카드 배치를 보여준다. 기존 플러그어블 광트랜시버는 라인카드 전면에 장착되며, PCB 배선의 RF 손실을 보상하기 위해 모듈 내에 DSP 칩이 포함된다. 하지만 대역폭 증가에 따라 RF 손실이 커져 전송속도 향상 시 DSP 전력 소모도 증가한다. 이를 개선하기 위하여 스위치 ASIC 주변에 근접 배치되는 OBO 모듈이 제안되었으나, 일정 거리 이상 떨어지면 전기 신호 손실 보상을 위해 CDR이 필요하다.

그림 2

도 및 (d) 각 모듈별 라인카드 배치 (c) (d)그림 2 (a) 플러그어블 광트랜시버, (b) OBO, (c) CPO 모듈 개념도, (d) 각 모듈별 라인카드 배치 형태

CPO는 스위치 ASIC과 광모듈을 동일 기판에 패키징해 RF 손실을 최소화한다. 이로 인해 DSP 칩을 제거해 제작 비용과 소모전력을 크게 줄이고 저지연 특성을 확보한다. 플러그어블 광트랜시버 대비 소모전력이 약 50% 감소하며, 1.6Tbps CPO는 60%까지 줄어드는 것으로 예상된다.

한편, CPO 기술을 적용한 경우 광모듈이 스위치 ASIC의 가장자리에 일렬로 배치되어야 하므로, 동일 면적 내에서 목표 전송용량을 확보하기 위해 모듈당 요구 전송 속도가 매우 높아지는 특징이 있다. 이로 인해 고밀도 집적이 가능한 실리콘 포토닉스 플랫폼(1Tbps/mm 이상의 대역폭 밀도)이 CPO 모듈 구현의 핵심 기술로 자리 잡고 있다.

Broadcom에서는 2024년 업계 최초로 실리콘 포토닉스 기반 6.4Tbps CPO 모듈을 적용한 51.2Tbps급 스위치를 출시하였으며[5], 최근에는 200Gbps SerDes를 적용한 CPO 호환 102.4Tbps급 스위치를 개발한 바 있다. Ayar Labs에서는 5pJ/bit 수준의 전력 효율과 5ns 수준의 저지연 특성을 갖는 양방향 2Tbps급 CPO 모듈을 개발하여 발표한 바 있다[6]. 향후, 채널당 400Gbps 기반 CPO의 경우 변조 속도 한계로 기존 실리콘 포토닉스 기술만으로는 구현이 어려울 것으로 예상된다. Arista와 같은 몇몇 네트워크 장비 업체들은 향후에도 플러그어블 광트랜시버가 시장에서 우위를 점할 것으로 예측하는 한편, 채널당 400Gbps 기반 초고속 광모듈의 경우 집적도와 고속 동작 특성을 동시에 확보하기 위해 InP 기반 고속 변조기와 실리콘 플랫폼의 이종 집적을 활용하는 InP-on-Si 구조의 CPO 기술이 유력한 해결책이 될 수 있다고 전망하였다.

CPO의 구조적 특징으로 인한 서비스성 및 교체성의 한계를 극복하기 위한 대안으로 LPO(Linear Pluggable Optics)가 주목받고 있다. LPO는 기존 DSP 기반 광트랜시버와 동일한 폼팩터를 적용하여 Face-Plate 장착 방식으로 라인카드에 배치되지만, 광트랜시버 내부의 DSP 칩을 제거하고 스위치 ASIC의 SerDes를 통해 모듈 내부의 광소자를 직접 구동하는 구조를 채택한다. 모듈 내부에 DSP 칩이 내장되지 않으므로 소모전력이 크게 절감되며, 지연시간 또한 1/10~1/20 수준으로 크게 낮출 수 있어 GPU 간 고속 연결에 유리하다.

그러나, 채널당 200Gbps 기반 LPO 모듈의 경우 선형 전자소자의 대역폭 한계로 인해 송신부에 한해서 DSP 기능을 활용하는 LRO(Linear Receiver Optics) 모듈이 절충안으로 제시되고 있다. 2025년 주요 광트랜시버 업체를 통해 채널당 200Gbps 기반 800Gbps 및 1.6Tbps 전송용 LPO 광트랜시버의 상용 시제품이 출시된 상태이다. 1.6Tbps를 기준으로 플러그어블 광트랜시버의 예상 소모전력은 25W 수준인 반면, LRO는 16W, LPO는 10W의 소모전력을 보일 것으로 예상된다. 광부품 시장조사 기관인 LightCounting에서는 2028년경 800Gbps 및 1.6Tbps 광모듈 시장에서 LPO 및 CPO 모듈이 전체의 30% 이상 점유할 것으로 전망하였다[7]. 특히, LPO 및 LRO의 경우 CPO에 비해 유지보수 용이성과 교체성 측면에서 상대적인 장점을 가지므로 향후 AI 데이터센터용 광모듈 시장에서 CPO와 경쟁 구도를 형성할 것으로 전망된다.

2. CPO 광원 기술 동향

CPO 광원은 전력 효율, 신뢰성, 집적도, 비용에 큰 영향을 미치는 핵심 요소로, 다양한 광원 구조가 연구 개발되고 있다. 기존 InP 기반 DFB/EML 광원을 패키지 내부나 근접 기판에 어레이로 배치할 경우, 채널 수가 수백 개 이상일 때 패키지 면적, 열 관리, 조립 복잡도, 비용에서 한계가 뚜렷하다. 이에 따라 CPO 구조에서는 이런 한계를 극복할 새로운 광원 기술이 필요하며, 대안으로 패키지 외부에 레이저를 분리하는 ELS(External Laser Source)와 Si 포토닉스 칩과 레이저 칩을 단계적으로 통합하는 이중 집적 레이저 구조가 제안되고 있다.

2.1 ELS 광원

최근 Lumentum, Ayar Labs, Furukawa Electric, Sumitomo Electric 등은 다수 채널에 분배 가능한 고출력 CW 광원과 온도 변화 및 패키지 내부 열 환경에 대한 높은 신뢰성, 랙‧보드 단위에서의 교체 용이성 등을 강점으로 하는 CPO 기반 ELS 솔루션을 잇달아 발표하였다[8].

Lumentum은 소자 출력 880mW의 1,310nm DFB 레이저를 사용하여, 50℃에서 Ex-Fiber 580mW를 제공하는 CPO용 고출력 ELS를 시연하였다. 낮은 광구속 계수를 갖는 양자우물 구조를 적용하여 포화 출력과 광결합 효율을 동시에 향상시키고, 4mm 길이의 긴 캐비티와 고반사(HR) 코팅 설계를 통해 고출력‧고효율 특성을 구현하였다.

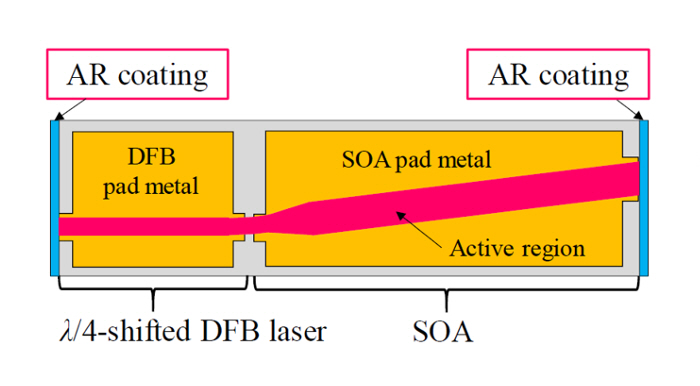

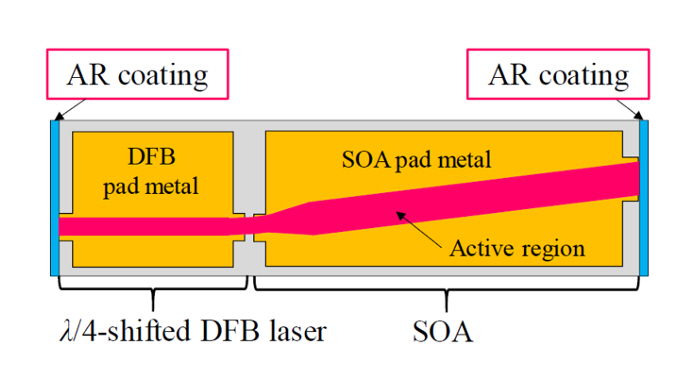

고출력‧저전력 동작을 위해 출력단에 SOA를 단일 집적하는 방식은 통신용 광원에서 널리 사용되는 기술이다. Sumitomo는 동일한 양자우물을 사용하는 DFB와 SOA를 단일 집적하고, pn 전류 차단층 구조를 적용한 1.31μm 고출력 레이저를 개발하였다[9]. λ/4 Phase-Shift 격자 구조와 양면 AR 코팅을 적용하여 안정적인 단일모드 동작을 확보하였으며, AR 코팅으로 인한 낮은 PCE는 SOA와 DFB 레이저의 길이 및 전력 분담을 최적화함으로써 출력을 향상시킬 수 있는 구조를 사용하였다.

CPO용 ELS는 스위치 ASIC 주변 및 랙 환경의 높은 온도에서 동작해야 하므로, TEC 없이도 안정적으로 구동 가능한 무냉각 레이저가 핵심 요구 사항이다. 최근에는 레이저 칩의 광결합 구조, 패키지 열 경로, 구동 조건을 최적화하여, 50℃ 이상의 동작 온도에서 수백 mW급 광출력과 높은 전기-광 변환 효율(PCE)을 동시에 만족하는 ELS가 활발히 보고되고 있다.

그림 3의 Sumitomo사 SOA 집적 DFB 레이저는 0~75℃ 범위에서 SMSR > 50dB의 단일모드를 유지하면서, 50℃와 70℃에서 각각 300mW, 200mW의 광출력과 약 23%의 PCE를 달성하여, 무냉각 고출력 ELS에 적용 가능한 광원 소자를 구현하였다. Furukawa는 CPO용 QSFP 폼팩터 ELS에서 하우징 온도 55℃ 조건에서 채널당 100mW를 상회하는(총 20dBm 수준) 파이버 결합 출력과 14.3% PCE를 달성한 무냉각 8채널 광원 구조를 발표하였다.

그림 3

SOA 집적 1.3μm 고출력 DFB 레이저(Sumitomo)

출처 Reproduced from W. Tian et al., “Progress in Research on Co-Packaged Optics,” Micromachines, vol. 15, no. 10, 2024, pp. 1–24.

Ayar Labs는 CW-WDM MSA가 정의한 O-band 파장 그리드(8/16/32λ) 규격을 준수하는 최초의 CPO/ELS용 다파장 O-band 광원을 상용화하였다. CW-WDM MSA 규격에 따라 설계된 16파장 CW 광원으로, CPO 시스템에서 요구되는 수백 채널급 데이터 전송에 필요한 광원을 단일 모듈로 공급할 수 있도록 구성되어 있다.

2.2 실리콘포토닉스용 광원

현재 상용화된 다수의 CPO 및 NPO 솔루션은 패키지 내부 실리콘 포토닉스 엔진에서 변조기와 수광 소자를 중심으로 기능을 구성하며, 레이저는 주로 외부 ELS 모듈에서 공급받는 구조를 채택하고 있다. 그러나 중장기적으로는 광원을 CPO 패키지 근처나 내부로 단계적으로 통합하는 방향으로 발전할 것으로 예상된다.

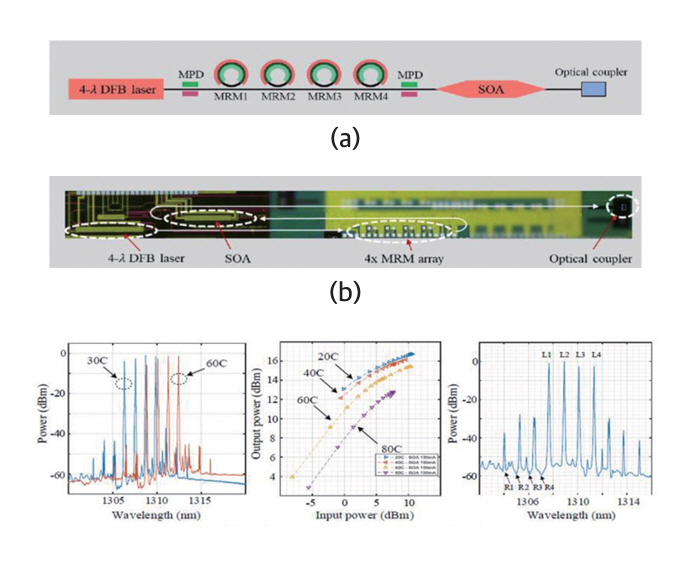

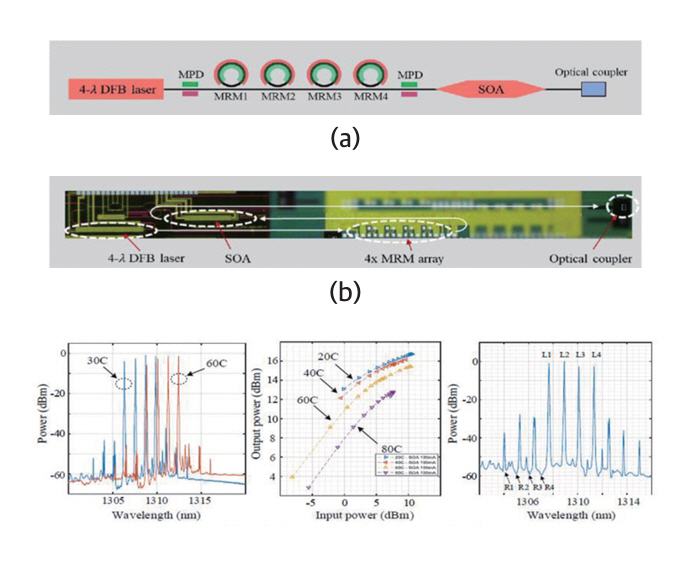

그림 4와 같이 인텔은 최근 대량생산용 300mm 실리콘 포토닉스 제조 공정을 통해 제작한 DWDM 4파장 DFB 레이저와 SOA를 실리콘 포토닉스 상에 이종 집적한 온칩 레이저 기술을 보고하였다[10]. 하나의 공진기에서 다중 파장을 생성하는 레이저 구조와 SOA를 집적하는 구조를 사용하여 고효율/초소형의 대량생산이 가능한 실리콘 포토닉스 광원 구현의 가능성을 제시하였다.

그림 4

SOA 집적 4파장 DFB 레이저 집적 SiPh 광송신기 PIC(Intel)

출처 Reprinted with permission from S. Liu et al., “Silicon photonics DWDM transmitter with heterogeneously integrated multiwavelength DFB laser and SOA,” J. Lightwave Technol. 43, 2025, pp. 1855-1860.

OpenLight는 Tower 파운드리 공정 PH18DA를 기반으로 하는 8인치 SOI III-V on Si 플랫폼에서 DFB 레이저와 EAM을 이종 집적한 광원 기술을 제안하였다[11]. 특히 DFB 레이저 양단의 대칭 출력을 활용하여 하나의 DFB로 2개 Lane을 구동함으로써 레이저 개수를 최소화하는 PIC 구조를 구현하였다. 이 레이저는 80℃에서 양 포트 각각 20mW 수준의 출력과 안정적인 단일모드 동작을 보였으며, 높은 수율을 통해 양산 가능성을 입증하였다.

3. 변조기·송신부 기술

실리콘 포토닉스는 실리콘 웨이퍼를 기반으로 광학 소자를 집적화하는 기술로, 데이터센터, AI, 5G/6G 통신 등 고속 데이터 전송 분야에서 핵심 역할을 하고 있다. 특히 광변조기는 빛의 위상, 강도, 편광 등을 전기 신호로 제어하는 장치로서, 실리콘 포토닉스 플랫폼에서 CMOS 호환성과 저비용 생산이 가능한 장점이 있어 많은 연구가 진행되고 있다. 최근 실리콘 포토닉스 기반의 광변조기 기술은 데이터센터와 AI, 통신인프라의 고속화 수요에 힘입어 매우 빠르게 발전하고 있으며[12,13], 100Gbps를 넘어 400Gbps, 800Gbps, 1.6Tbps까지 지원 가능한 초고속 광변조기까지 보고되고 있다[14]. 또한, 효율 및 소형화에서 꾸준히 기술 발전이 이뤄지고 있어, 광변조기와 드라이버, 광원, 광검출기를 단일 칩 또는 패키지로 집적하는 추세가 강화되고 있다[15].

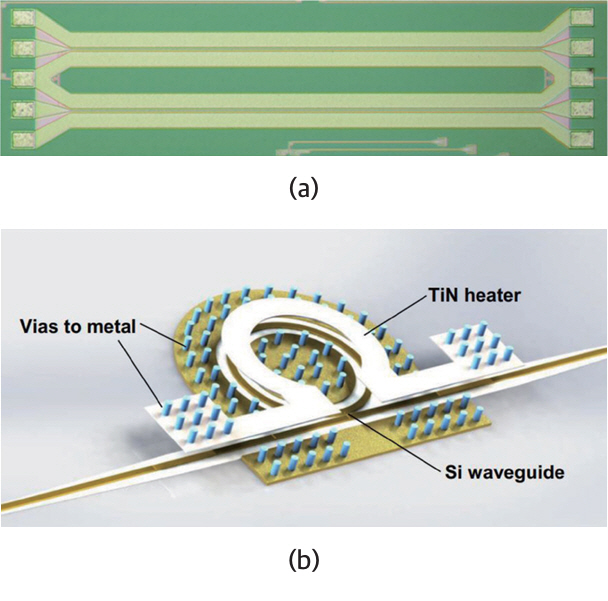

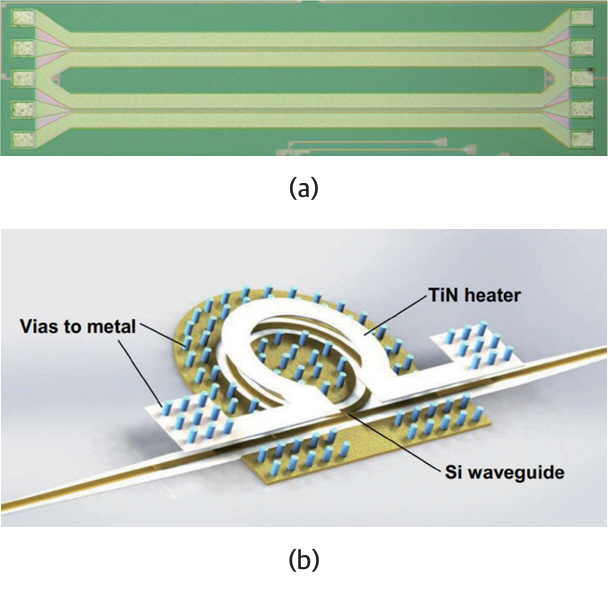

실리콘 포토닉스 기반의 광변조기는 대표적으로 그림 5(a)는 Mach-Zehnder 간섭계 구조의 광변조기(MZM)와 그림 5(b)의 마이크로 링 공진기 구조의 광변조기(MRM)로 분류될 수 있다. MZM은 넓은 파장 대역, 선형성, 저왜곡, 열적 안정성, 공정 민감도 낮은 반면, 크기가 수 mm이며 구동전압 및 소모전력이 상대적으로 높은 특성을 가지고 있어, 광대역 코히어런트 광통신에서 요구되는 선형 변조(예: QAM)에 적합하다[16]. MRM은 초소형이고, 공명 증폭으로 유효광 경로 길이가 증가하므로 고효율이며, 낮은 구동 전압과 작은 칩 면적의 강점이 있는 반면, 좁은 동작 파장과 온도 및 공정에 민감하여 안정성이 상대적으로 낮고, 고밀도 WDM 및 저전력 집적 Tx, 단일 파장 고속 링크에 적합하다[17]. 대표적으로, 실리콘의 플라즈마 분산 효과 한계를 극복하기 위해 결합 공진기 광도파로 구조를 채택하여 AI 기반 신경망(ANN) 이퀄라이저를 결합해 비선형 왜곡과 공정 변동을 보상함으로써 8채널 WDM 칩으로 1.6Tb/s/mm² 데이터 밀도의 3.2Tbps 용량을 발표하였다[18].

그림 5

실리콘 포토닉스 기반의 광변조기: (a) Mach-Zehnder 간섭계 기반 광변조기, (b) 마이크로 링 공진기 기반 광변조기

high-speed communications and photonic signal processing,” npj Nanophoton., vol. 1, no. 27, 2024.

(b) Reprinted with permission from D.W.U. Chan et al., “C-band 67 GHz silicon photonic microring modulator for dispersion-uncompensated 100 Gbaud PAM-4,” Opt. Lett. vol. 47, no. 11, 2022, pp. 2935–2938. © Optica Publishing Group

향후 실리콘 포토닉스 변조기는 AI/뉴로모픽 컴퓨팅 LIDAR, AR/VR, 양자 정보 처리 등의 분야로 확대될 전망이고, 신소재 도입과 AI 최적화로 다양한 분야에 활용될 것으로 기대하고 있다[19]. 신소재 측면에서 살펴보면, 박막 리튬 니오베이트(TFLN/LNOI)는 포켈스 효과로 광대역 응답(67GHz 이상)과 저손실(2.2V half-wave voltage)을 제공할 수 있어 데이터 센터 백본에 적합하다. 전기광학 폴리머(EO Polymers)는 1,000pm/V 이상의 EO 계수로 Vπ < 0.5V이고 2mm 소형 장치에서 400Gbps 이상(최대 3.2Tbps) 지원 가능할 것으로 전망된다. 또한, 바륨티타네이트(BTO)는 높은 EO 계수와 CMOS 호환성으로 초고속 상호 연결을 지원하기 위한 실리콘 포토닉스 광변조기에 도입하기 위한 연구가 진행되고 있다.

레이저 광원이 집적된 구조로서 EML은 데이터 센터용 IM-DD(직접 변조) 광링크에서 100G/lane 이상의 성능을 달성하려는 요구와 맞물려 연구 및 상용화가 활발하다. 전통적인 InP 기반 EML은 비용, 패키징, 열관리, 확장성을 개선하기 위하여 집적화와 실리콘 포토닉스 기판 위에 EML 칩을 결합하는 이종 집적화 연구가 진행되고 있다. 표 1과 같이 최근 90GHz의 3dB 전기-광학 대역폭을 갖는 초고대역폭 EML을 이용하여 PAM-4(320Gbits/s), PAM-6(413Gbits/s) 및 PAM-8(480Gbits/s) Back-to-Back 성능을 달성하고, 160GBaud PAM4에서 채널 1270(CD -2.25ps/nm) 및 1330(CD +1.21ps/nm)을 사용한 500m 광섬유 전송을 성공적으로 시연하여 차세대 3.2T 400G/lane의 단거리 IM-DD에 활용될 것으로 기대된다[20].

4. 수신부·광검출기

미국의 Macom, Coherent, 스위스의 Albis 등 주요 광부품 업체들은 50m 이하 단거리 통신용으로 850nm 파장 대역용 VCSEL 광원과 GaAs계 광검출기 소자를 개발하고 있다.

AI 데이터센터에 사용되는 CPO 기반 광트랜시버 개발 선두그룹인 미국 Broadcom사는 2023년 ECOC 학회에서 PAM4 변조 방식으로 레인당 200Gbps 전송이 가능한 EML 기반 4채널 800Gbps 및 8채널 1.6Tbps CWDM 광트랜시버를 전시하였는데, 이 EML 기반 광트랜시버에는 표면입사형 4채널 광검출기 소자 칩이 실장되어 있다. 이 광검출기 소자 칩의 제반 특성은 현재 Broadcom사에서 판매 중인 모델명이 118Lx인 칩 후면에 InP 볼록렌즈가 집적된 112Gbaud InGaAs 광검출기 소자 칩 제품군과 유사하다. 참고로 118LX 광검출기 소자의 3dB 대역폭은 2V의 역전압 인가 시 50GHz 정도이고, 1,310nm 파장에서의 광 응답도는 0.7A/W인 것으로 알려져 있다.

Broadcom사는 2024년 OFC 학회에서 광신호 변조 시 최적화된 FEC 코드를 적용하여 현재 50m 이내의 850nm 파장 다중모드 광노드에 대량 적용되고 있는 자사 PAM4 100Gbps GaAs VCSEL 소자의 전송거리를 100m까지 확장시키거나 전송용량을 200Gbps로 증가시킨 연구결과를 발표하였다[21]. 이때 사용된 4채널 VCSEL 기반 광트랜시버에는 Broadcom의 4채널 전면입사형 InGaAs PD(AFCD-P84HS와 외형 동일)가 사용되었으며, 이 소자는 15Ω 부하에서 3dB 대역폭이 36GHz이고, 광축 정렬 용이성을 위해 수광부 직경이 30μm 이상으로 설계되었다.

한편, 광통신용 광검출기 소자 칩을 전문적으로 생산하는 일반적인 업체들이 850nm 파장 대역용 광검출기 소자의 제작을 위해 GaAs 광흡수 물질을 사용하는 것과 달리 Broadcom사는 InGaAs 광흡수 물질을 사용하고 있다. 이는 800G/1.6T 광트랜시버의 안정적인 동작 및 설계를 위해서는 광검출기 소자의 큰 3dB 대역폭 이외에도 큰 응답도도 중요하기 때문이다.

CPO 기반 광학엔진 설계/제작 시 광원, 광변조기 및 광검출기와 같은 능동 광소자를 광파장 및 편광 다중화/역다중화 소자와 같은 수동 광소자와 단일집적하는 것이 광학엔진의 소형화 및 대량생산 그리고 가격 측면에서 하이브리드 집적에 비해 유리할 것으로 기대된다. 현재는 광원 소자를 단일집적할 수는 없지만 다른 능동 광소자들의 단일집적이 가능한 실리콘포토닉스 플랫폼이 CPO 기반 광학엔진을 위한 광 플랫폼으로 선호된다.

AI 데이터센터가 주요 수요처인 Broadcom사 역시 실리콘포토닉스 플랫폼을 사용하고 있지만 EML 및 광검출기 소자는 실리콘포토닉스 플랫폼상에 단일집적이 아닌 하이브리드 집적 방식으로 실장되고 있다. 반면, AI 및 고성능 컴퓨팅(HPC) 분야에서 미국 NVIDIA사와 협력관계인 대만 TSMC사는 광변조기 및 광검출기 소자가 단일집적되는 COUPE(Compact Universal Photonic Engine)라는 명칭의 실리콘 포토닉스 플랫폼을 자사의 CPO 기반 광학엔진으로 사용하고 있다. 실리콘포토닉스 플랫폼에 광검출기 소자를 단일집적하기 위해서는 반드시 실리콘 또는 SOI 기판상에 Ge 광흡수층 물질의 에피층이 성장되어야 한다. 그리고, 단일집적 Ge 광검출기 소자의 광입사 구조로는 광파장 및 편광 다중화/역다중화 소자를 구성하는 광도파로와의 광연결뿐만 아니라 서로 Tradeoff 관계인 3dB 대역폭과 응답도를 동시에 향상시킬 수 있는 광도파로형이 선호된다.

5. 고속 광검출기 R&D 현황

Ge 광검출기 소자가 적용된 실리콘포토닉스 광집적소자는 1,310nm 파장 대역의 광신호를 사용하는 것이 광검출기 응답도 측면에서 유리하다. 그러나 1,550nm 파장에서 동작하는 Ge 광검출기 소자에 관한 최근의 연구[22]는 측면 pin 구조 개선 및 CMP 공정 도입을 통해 100GHz의 매우 큰 3dB 대역폭뿐만 아니라 1V의 역전압 인가 시 7nA로의 매우 작은 암전류(누설전류)와 1.05A/W의 매우 큰 응답도를 동시에 얻을 수 있다는 우수한 결과를 제시하고 있다.

향후 CPO 기반 광학엔진은 PAM4 변조 방식으로 레인당 400Gbps 전송이 가능할 수 있도록 개발될 것으로 예상된다. 이러한 PAM4 400Gbps 전송에 적용할 광검출기 소자의 3dB 대역폭은 Nyquist 주파수인 100GHz 이상인 것이 바람직하다. 현재 중국과 일본의 여러 대학 또는 연구기관에서 3dB 대역폭이 100GHz 이상인 Ge 또는 InGaAs 광검출기 소자에 관한 많은 연구결과를 발표한 것으로 파악된다. 국내에서는 67GHz 이상의 큰 3dB 대역폭을 달성한 한국전자통신연구원(ETRI)의 후면 InP 렌즈 집적 InGaAs 광검출기 소자를 개발하였다[23].

III. CPO 패키징 및 광원 집적 기술

1. 실리콘 포토닉스 플랫폼 현황

실리콘 포토닉스는 대규모 집적, CMOS 공정 호환성, 대량생산을 강점으로 광송수신 모듈에 적용되는 광집적회로(PIC)의 핵심 기술로 자리 잡고 있다. 특히, AI 데이터센터의 저전력화를 위한 CPO 광송수신 소자의 경우 전자소자와 집적하여 초소형 저전력 광모듈을 제작하는데 매우 큰 장점이 있는 실리콘 포토닉스 기술을 주로 사용한다.

그러나, 실리콘은 간접천이 밴드갭(Indirect Bandgap) 을 가지고 있어 전자가 광자로 변환되는 효율이 낮고 레이저 공진기 내에서 증폭이 충분하지 않아 광원을 형성하지 못할 뿐만 아니라, 100Gbaud 이상급 초고속 광변조기의 구현도 어려운 단점이 있다. 실리콘 포토닉스 기반 광변조기는 일반적으로 p-n/p-i/n 구조를 이용하여 플라즈마 분산효과(Carrier Plasma Dispersion)를 발생시켜 굴절률을 변조하는데, 이는 변조 효율이 낮아 한계가 있다. 마하젠더 구조의 실리콘 포토닉스 광변조기는 낮은 변조 효율을 보상하기 위하여 칩 길이가 길어져 저전력, 초고속 동작이 어렵고, 링 구조의 실리콘 포토닉스 변조기는 초고속으로 동작하기 위한 품질계수(Q-Factor)와 변조 효율, 구동 전압이 상충(Trade-Off) 관계가 있어 초고속 동작을 위한 최적화 난이도가 높다.

위와 같은 단점을 극복하기 위하여 표 2와 같이 실리콘 포토닉스 플랫폼에 다양한 장점이 있는 이종의 재료를 집적하는 노력이 진행되고 있다. SiN 재료는 낮은 도파 손실, 높은 온도 안정성, 큰 도파 모드의 장점을 가지고 있어, 길이가 긴 수동 광소자 구현과 광섬유와 광결합(Edge Coupling)에 유리하다. LN(LiNbO3)는 매우 강한 포켈스 효과(Pockels Effect)로 인하여 작은 전압으로 굴절률을 선형적으로 변화시킬 수 있어, 이를 바탕으로 저전력‧고속 동작‧선형성‧안정성을 동시에 달성 가능하다. 폴리머 재료는 저비용, 대면적, 유연 소자 공정이 용이한 장점을 갖는다. III-V(InP, GaAs) 재료는 직접천이 밴드갭(Direct Bandgap)을 가지고 있어 다양한 능동소자(LD, SOA. PD)의 효율적인 구현이 가능하다. 특히, 광통신에 필수적인 광원(LD)을 실리콘 포토닉스 플랫폼 내에 집적할 수 있는 점이 매우 중요하다.

표 2 광소자 플랫폼 장/단점 및 특징 비교 표

2. 광원 집적 구현 기술

CPO에서 광원 집적 구현 기술은 차세대 AI 및 고성능 컴퓨팅 데이터센터가 요구하는 저전력, 고속 네트워크 환경을 실현하는 핵심 기술이다. 광원 집적 방식에서는 기존의 전통적 Off-Chip 광원과 차세대 On-Chip 집적 기술이 병행 발전 중이며, 각 방식이 시스템 성능, 전력 소모, 공정 비용 등에 미치는 영향이 매우 크다.

Off-Chip 광원 방식은 실리콘 포토닉스(SOI, InP 등)를 활용하여 모듈 외부에서 레이저 광원을 공급하며 기술 성숙도가 높고 다양한 시스템 적용 사례가 있지만, 생산 및 조립 비용이 많이 들고 결합 손실(2~8dB)도 커서 효율 개선에 한계가 있고, 외부 레이저 광원을 별도로 필요한 단점이 있다.

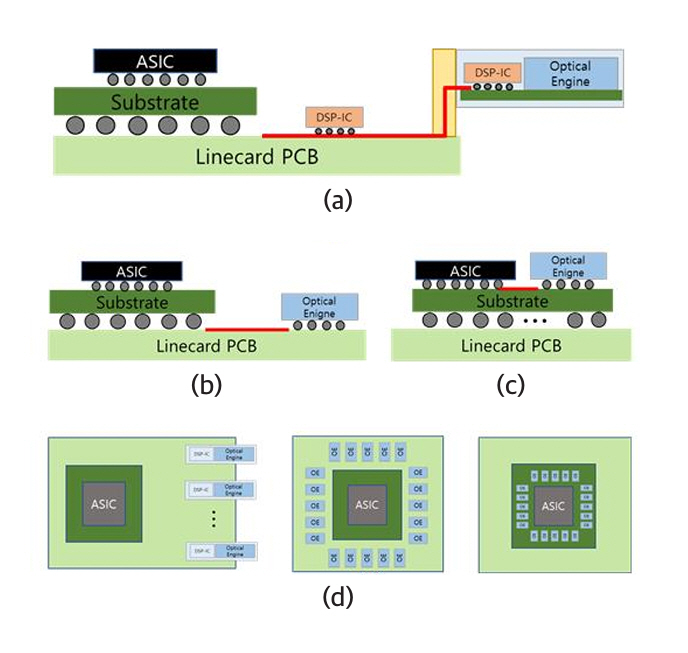

이에 비해 Heterogeneous Integration(이종 집적) 방식은 SOI 기판 위에 III-V 반도체 레이저, 광증폭기(SOA), 광검출기(PD) 등 다양한 광소자를 집적할 수 있다[4]. 이 방식은 결합 손실과 비용 측면에서 개선 효과가 있지만, 소자 간 열저항 문제 등 설계와 운영에서 한계가 있다. 그림 6과 같이 Intel과 Ayar Labs 같은 글로벌 선도 업체들이 실리콘 포토닉스에 III-V 반도체 레이저를 하이브리드 집적 방식으로 구현하고 있다. 특히 Ayar Labs는 업계 최고 수준(5pJ/bit)의 에너지 효율, 1Tbps/mm 이상의 대역폭 밀도를 달성하여 CPU와 광엔진의 통합 패키지 상용화에 성공하였다. Broadcom 역시 실리콘 포토닉스 기반 EML 모듈을 활용해 800G, 1.6T급 고속 광통신 시스템을 개발하며, PAM4 및 WDM 기술을 통해 에너지 효율과 집적도를 높였다.

그림 6

CPO 광원: (a) IBM&II-VI, (b) Ranovus, (c) Intel, (d) Ayar-labs, (e) Hengtong Rockley

출처 Reprinted from M. Tan et al., “Co-packaged optics (CPO): status, challenges, and solutions,” Front. Optoelectron., vol. 16, no. 1, 2023, pp. 1–40.

Direct Epitaxial Growth on Si 방식은 III-V 반도체 소재를 실리콘 기판에 직접 에피택셜 성장시키는 기술로서 결합 손실(0.1dB)이 극히 낮고 제조비용도 상대적으로 저렴한 장점이 있다. 그러나 실리콘과 III-V 소자의 결함, 공정 호환성, 대면적 균일 성장 등 기술적 과제가 남아 있어 상용화까지 추가 개발이 필요한 단계이다.

Wafer Bonding + Regrowth 방식은 실리콘 기판에 III-V 반도체 웨이퍼를 본딩한 뒤 레이저를 재성장하는 구조이다. 이 방식은 결합 손실과 광효율을 동시에 크게 개선하며, 높은 집적도와 수율을 실현할 수 있는 장점을 가지고 있다. IBM과 II-VI는 V-groove 및 패시브 얼라인먼트 기술을 적용해 광원과 스위치 칩 간 거리를 극소화하고, 결합 손실을 0.4dB로 낮추는 데 성공한다. Ranovus와 IBM이 공동 개발한 51.2Tbps 광학엔진 역시 이런 본딩‧재성장 구조이다.

Remote Epitaxy + Coupon Transfer 방식은 2D 소재(예: 그래핀 등)를 기반으로 한 III-V 쿠폰을 실리콘 위에 전사하는 방식으로, 이 방식은 매우 저렴한 제조비용, 낮은 결합 손실, 실리콘 호환성, 고집적 구성 등 다양한 장점을 동시에 제공하며, 미래 AI 데이터센터 실현에 가장 혁신적인 광원 집적 기술로 주목받고 있다.

이처럼 CPO의 광원 집적 기술은 시스템 성숙도, 비용, 결합 손실, 집적도 등 다양한 측면에서 끊임없이 진화하고 있으며, 각 방식별 대표적인 상용‧산업 사례를 계속 구현하고 있다.

3. CPO 2.5/3D 패키징 기술

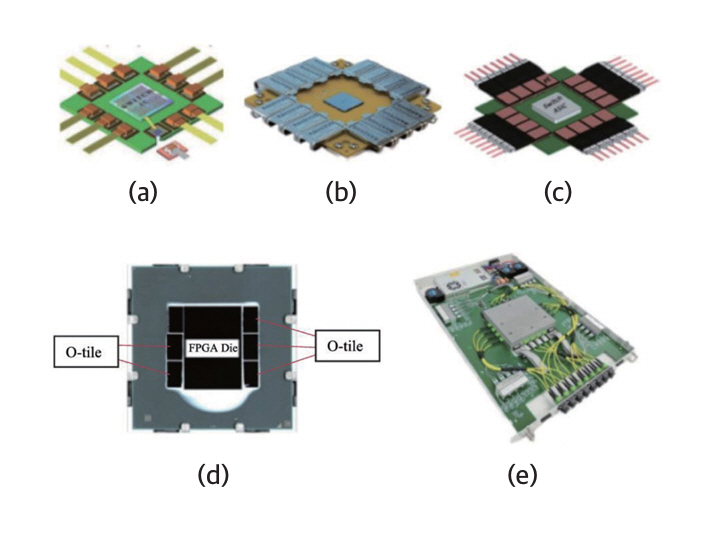

CPO에서 전자소자(EIC; ASIC/GPU/CPU)와 광소자(PIC)를 단일 패키지 안에 최단거리로 집적하기 위해서는 2.5D/3D 패키징 기술이 핵심 역할을 한다.

2.5D 패키징에는 다수의 EIC/PIC를 상하부에 집적할 수 있는 연결 구조물인 인터포저가 핵심 역할을 수행한다. 실리콘 인터포저는 CMOS 공정 기반 미세 배선과 다층 금속을 이용하여 수 μm급 피치의 고밀도 라우팅을 가능하게 하여, 다수의 칩을 높은 I/O 집적도로 연결한다. 유리 인터포저는 상대적으로 낮은 유전율과 우수한 평탄성을 기반으로 고주파 특성과 대형 기판 구현 측면에서 장점을 가지고 있지만, 낮은 방열 특성으로 인해 열방출에 불리하다.

인텔에서는 전체 영역에 인터포저를 사용하는 대신 고속 RF 배선이 필요한 영역(ASIC과 광학 엔진 칩 사이)에만 국부적으로 소형 실리콘 브리지를 삽입하는 EMIB 기술을 개발하였다[24]. 이 기술은 실리콘 인터포저의 미세 배선과 고대역폭 링크를 사용함에도 불구하고 대면적 인터포저의 비용을 낮출 수 있고, 브리지의 위치와 개수를 유연하게 설계할 수 있어, 채널 배분과 신호 무결성(SI) 설계 측면에서 유리하다.

ETRI에서는 그림 7과 같이 실리콘 기반의 Cu TSV 집적형 인터포저를 이용하여 2.5D 광모듈 패키징을 연구 개발하고 있다. 50GHz 이상의 RF 전송로와 NiCr 박막 저항을 실리콘 인터포저에 집적하였고, Cu TSV를 통해 기판 상하부의 RF 배선(Signal & GND)을 연결해 고밀도 라우팅이 가능하다.

2.5D 패키징이 동일 평면상의 다이(Die)들을 인터포저를 통해 연결하는 구조인 반면, 3D 패키징은 다이를 수직으로 적층하여 면적을 줄이고 신호 경로를 더 감소시키는 패키징 방법이다. 광원 구동/수신부 증폭/온도 및 전원관리와 같은 EIC와 광/전 변환을 수행하는 PIC를 적층하여 패키징할 수 있다[25]. 또한, 스위치 ASIC 칩과 메모리 칩 등 모든 EIC 칩 간의 통신을 하부의 PIC 기판을 통해 통신하는 방법도 제시되고 있다[26]. 3D 집적은 I/O 밀도와 속도를 해결할 수 있는 유망한 기술이지만, 복잡한 전기 배선의 배열/정렬/접합하는 기술, 고속 통신을 위한 TSV, 층 간 열방출 및 신뢰성 확보 등 아직 해결해야 할 과제가 많다.

IV. 기업 동향 및 생태계

1. 스위치 ASIC 기업 동향

채널당 100Gbps 이상의 전송속도를 갖는 광트랜시버와 광학 칩렛(엔진)의 신호처리를 위하여 라인카드 내에 초고속 스위치 ASIC 칩이 적용된다. 100Gbps/lane PAM4 신호를 처리할 수 있는 51.2T ASIC 칩은 2022년에 이미 상용화되었으며, 최근 Broadcom, Arista, Juniper, Delta 등의 시스템 업체에서는 채널당 200Gbps PAM4 신호를 수용할 수 있는 ASIC 칩을 개발 중이다. 특히, Broadcom사에서는 200Gbps/lane 기반 102.4T ASIC 칩인 토마호크 6를 2025년 6월 출시하여 채널당 200Gbps PAM4 기반 800G/1.6T 광트랜시버 및 광학 칩렛(엔진)에 적용하고 있다. Broadcom사 내부 로드맵에는 토마호크 6의 후속인 204.8T급 ASIC인 토마호크 7 개발을 명시하였으며, 그림 8의 Cisco 발표에 의하면 400Gbps/lane 신호를 수용할 수 있는 409.6T급 ASIC 스위치 출시를 예상하고 있어 채널 당 200Gbps & 400Gbps CPO 기술이 급속도로 발전할 수 있는 전기가 마련되고 있다.

Broadcom사 CPO 로드맵에 의하면 2025년 4월 세계 최초로 200G/lane 기반의 3세대인 6.4T/xPC-CPO 모듈 개발결과를 발표하였으며, 2028년 4세대 400G/lane CPO 모듈 개발을 계획하고 있다. 200G/lane CPO 모듈의 광원으로 Broadcom에서 자체 개발한 200G VCSEL이 사용되었으며, 400G/lane CPO 모듈에는 400G EML (Electro-absorption Modulator-integrated Laser) 또는 400G TFLN(Thin-Film Lithium Niobate) 광변조기가 적용될 것으로 추정된다.

현재, 채널당 100Gbps 및 200Gbps PAM4 기반의 광원 및 광검출기 구동용 전자소자는 이미 상용화되었으며, OFC 2025 전시회에서 일부 업체는 채널당 400Gbps PAM4 광원 구동을 위한 Driver 시제품을 출시하였고, 2026년에는 다수의 업체에서 400Gbps PAM4/PAM6 신호처리용 전자소자를 출시할 것으로 전망된다.

2. 국내 기업·기관 R&D 현황 및 공급망

AI 데이터센터에 사용되는 광트랜시버 및 광학 엔진(칩렛)용 광소자/부품의 경우, 국내 기업에서는 생산 규모 및 수율 등의 문제로 아직 상용화하지 못한 상태이며 주로 연구 개발 수준에 머물러 있다. 반면, 삼성이나 한화마이크론 등의 국내 기업은 최근 기술 동향에 발맞추어 CPO 기술 분야에 본격적인 투자와 연구 개발을 활발하게 진행하고 있다.

CPO 기반 핵심 연구 개발은 2025년부터 연구소를 중심으로 국내 기업이 참여하는 형태로 진행 중이다. 전자부품연구원(KETI)은 채널당 200Gbps PAM4 기반 3.2Tbps 이더넷용 CPO 광학엔진 및 채널당 128Gbps 기반 1Tbps PCIe 7.0용 CPO 광학엔진 개발에 착수하였다. 한국전자통신연구원(ETRI)은 채널당 100Gbps 실리콘 포토닉스 링변조기 기반 3.2Tbps 이더넷 CPO 광학 칩렛 개발을 진행 중이다.

향후, CPO 광학 엔진(칩렛) 개발에 참여한 국내 기업을 중심으로 채널당 100Gbps뿐만 아니라 200Gbps 기반 광소자/광부품 공급망이 형성되고, 이를 기반으로 800G/1.6T/3.2T 광모듈이 상용화될 것으로 전망된다.

3. ETRI 광통신부품연구실 연구성과 및 계획

ETRI 광통신부품연구실에서는 AI 데이터센터용 200Gbps 이상급 광원과 광검출기를 개발 중이며, 실리카 광도파로와 다채널로 광결합할 수 있는 3D 나노프린팅 기반 포토닉 와이어본딩 기술을 개발하고 있다.

그림 9는 ETRI에서 개발한 전계흡수변조광원(EML)의 E/O(Electrical/Optical) 응답 특성을 보여준다. 전계흡수변조광원의 3dB 변조대역폭은 25~75℃에서 70GHz 이상을 뛰어넘는 매우 우수한 특성을 보였다. 특히, 등가회로 분석에 의한 3dB 변조대역폭은 45℃에서 약 92GHz로 추정되어[27] 200Gbps/lane PAM4뿐만 아니라 400Gbps/lane PAM6 신호 전송도 가능할 것으로 기대된다. 그림 9 안의 삽입 이미지는 전계흡수변조광원을 25~70℃ 온도에서 224Gbps PAM4 전기신호로 변조했을 때, BtB(Back-to-Back) 및 2km 광전송한 특성을 보여준다. 70℃ 고온에서 2km 전송 시 Outer ER(Extinction Ratio)은 4.2dB, TDECQ 특성은 2.1dB의 양호한 특성을 보여 224Gbps PAM4 광신호를 2km 전송 가능함을 확인하였다.

그림 10은 ETRI에서 개발한 렌즈 집적 InGaAs 광검출기와 수광부 직경에 따른 O/E(Optical/Electrical) 응답을 보여준다. 수광부 10μm 직경에서 3dB 대역폭은 66GHz, 광반응도는 0.8A/W 이상이며, 6μm와 8μm 직경에서 3dB 대역폭은 70GHz 이상[28], 등가회로 분석 시 약 80GHz로 예측된다. 광검출기의 흡수층 두께와 직경 감소, 정전용량 및 직렬저항 최적화로 3dB 대역폭을 더 증가할 것으로 기대된다.

그림 11(a)는 2.5%-△ 실리카 광도파로 수직 단면 및 표면 입사형 200Gbps 광검출기(Top SI-PD: Surface-Illuminated Photo-Diode) 표면에 3D 나노프린팅 기반 다중모드 포토닉 와이어를 90°로 굽혀서 형성한 결과이다. 다중모드 포토닉 와이어로 연결한 후의 광수신 모듈의 광결합 손실은 0.1dB 이하로 세계 최고 수준을 보였다. 그림 11(b)는 2.5%-△ 실리카 광도파로와 광흡수변조광원(EML) 단면에 3D 나노프린팅 단일모드 포토닉 와이어를 수평 형성한 결과이다. 단일모드 포토닉 와이어로 연결한 4채널 광송신 모듈은 100mA에서 약 10dBm 광출력을 보였고, 광결합 손실은 약 2.58dB로 세계적 수준이다. 최근 8채널 다채널 광송신‧수신 모듈에도 이 기술을 적용 중이다.

향후, ETRI에서 개발한 200Gbps급 광소자의 성능 개선 및 400Gbps PAM4 광신호 전송을 위해 전계흡수변조광원 및 광검출기의 3dB 대역폭을 100GHz 이상으로 증가시킬 예정이다. 또한, Si/SiN PIC 플랫폼에 InP 기반의 EAM 및 DFB-LD 광원을 이종 집적하고, 포토닉 와이어본딩 기반 다채널 광결합 기술을 적용하여 채널당 400Gbps PAM4/PAM6 기반 3.2Tbps 이상급 CPO 광학 엔진(칩렛) 모듈 개발 시, AI 데이터센터 시장에 조기 진입이 가능할 것으로 기대된다.

V. 결론

CPO 광통신 부품은 AI 데이터센터 내 초고속‧저전력 데이터 전송 실현을 위한 핵심 기술로, 스위 ASIC과 광통신 엔진을 단일 패키지에 집적하여 전기 신호 경로를 단축함으로써 전력 소모와 신호 지연을 최소화하고 AI 워크로드 처리에 최적화된 고속 저전력 광통신을 가능하게 할 것으로 생각된다.

최근 1.6Tbps 이상 초고속 광모듈 수요 증가로 기존 PCB 기반 전기 인터페이스 한계에 도달하면서 CPO 기술은 데이터센터 네트워크 아키텍처의 대안으로 주목받고 있다. 국내에서도 데이터센터를 위한 광통신 시장 진입을 위해 실리콘 포토닉스 기반 광소자, 고속 수신기, 고밀도 집적 및 패키징 기 술 연구 개발에 주력하고 있지만, 인프라 부족과 전문인력 부족으로 선진 그룹에 비해 아직 초기 단계이다. CPO를 위한 실리콘 포토닉스 분야의 글로벌 경쟁력 확보를 위해서는 광소자 제작부터 집적, 패키징, 평가 인증까지 전 주기적 인프라 구축이 필수적이다.

앞으로 국내 연구 개발은 저전력 고속 광소자와 성능 개선 기술 개발에 집중하고, 국제 표준화 참여 확대와 산학연 협력 강화, 공급망 안정성 확보 및 산업 생태계 조성이 병행되어야 한다. 이와 같은 국내 광산업 생태계를 구축하고 중장기 전략 추진을 통해 글로벌 차세대 광통신 시장에서 주도권을 확보할 수 있을 것이다.

용어해설

DFB 주기적인 브래그 격자를 두어 특정 파장만 선택적으로 공진·증폭시키는 분포 피드백 구조

EML DFB 레이저와 EA 흡수변조기를 한 칩에 집적해, 외부 변조 방식으로 고속 광신호를 만들어내는 광원

ELS 외부에 있는 레이저 광원이 생성한 빛을 파이버·도파로를 통해 PIC 등에 공급하는 방식

PAM4 기존 2-level 대비 4-level 광세기 변조 방식으로 심볼 당 2-bit를 전송하는 방법

PIC 실리카, InP, 폴리머, 실리콘, 실리콘 나이트라드 기판 등에 광도파로 및 광원/광검출기가 이종 또는 단일 집적된 광집적회로

SiPh 실리콘 기반 도파로와 수동·능동 광소자를 CMOS 공정으로 집적하는 광집적회로 기술

G. Chen et al., "Electronic Chip Package and Co-Packaged Optics (CPO) Technology for Modern AI Era: A Review," Micromachines, vol. 16, no. 4, 2025, pp. 1–21.

W. Tian et al., "Progress in Research on Co-Packaged Optics," Micromachines, vol. 15, no. 10, 2024, pp. 1–24.

IDTechEx website. http://www.IDTechEx.com

M. Tan et al., "Co‑packaged optics (CPO): status, challenges, and solutions," Front. Optoelectron., vol. 16, no. 1, 2023, pp. 1–40.

Broadcom, "Broadcom Delivers Industry’s First 51.2-Tbps Co-Packaged Optics Ethernet Switch Platform for Scalable AI Systems." https://www.broadcom.com/company/news/product-releases/61946

AyarLabs website. https://ayarlabs.com/teraphy/

B. Wheeler and V. Kozlov, "Highlights from the 1st virtual conference on Co-Packaged Optics (CPO)," 2025. 7. 22. https://www.lightcounting.com/newsletter/en/july-2025-highlights-from-the-1st-virtual-conference-on-co-packaged-optics-cpo-406

W. Zhou et al., "High power CW laser for co-packaged optics," in Proc. Conf. Lasers Electro-Opt., (San Jose, CA, USA), May. 2022, pp, 1–2.

D. Inoue et al., "High-power and stable operation of 1.31μ mλ/4-shifted DFB laser integrated with semiconductor optical amplifier," in Proc. Int. Semicond. Laser Conf., (Orlando, FL, USA), Sep. 2024.

S. Liu et al. "Silicon photonics DWDM transmitter with heterogeneously integrated multiwavelength DFB laser and SOA," J. Lightwave Technol. 43, 2025, pp. 1855-1860.

E. Norberg et al., "Silicon photonics platform with heterogeneously integrated lasers and EAMs for 1.6/3.2 T," in Proc. Opt. Fiber Commun. Conf., (San Francisco, CA, USA), no. M3K.3, Mar. 2025.

MRA , "Exploring Innovations in Silicon Photonic Modulator: Marke t Dynamics 2025-2033," 2024. https://marketreportanalytics.com/reports/silicon-photonic-modulator-383215

B. Tossoun et al., "Large-Scale Integrated Photonic Device Platform for Energy-Efficient AI/ML Accelerators," IEEE J. Sel. Top. Quantum Electron., vol. 13, no. 3, 2025, pp. 1–26.

Y. Li et al., "Silicon-Organic Hybrid Modulators Based on a Coupled One-Dimensional hotonic Crystal Slot Resonator Waveguide," IEEE Photon. J., vol. 17, no. 3, 2025, pp. 1–7.

S. Shekhar et al., "Roadmapping the next generation of silicon photonics," Nat. Commun., vol. 15, no. 751, 2024.

X. Zhou et al., "Silicon photonics for high-speed communications and photonic signal processing," npj Nanophoton., vol. 1, no. 27, 2024.

D.W.U. Chan et al., "C-band 67 GHz silicon photonic microring modulator for dispersion-uncompensated 100 Gbaud PAM-4," Opt. Lett. vol. 47, no. 11, 2022, pp. 2935–2938.

Y. Yuan et al., "A 5 × 200 Gbps microring modulator silicon chip empowered by two-segment Z-shape junctions," Nat. Commun., vol, 15, no. 918, 2024.

C. Han et al,. "Exploring 400 Gbps/λ and beyond with AI-accelerated silicon photonic slow-light technology," Nat. Commun., vol. 16, no. 6574, 2025.

P. Bhasker et al., "413 Gbits/s PAM-6 O-band CWDM Electroabsorption Modulated Lasers for 400G per lane IM-DD Applications," in Proc. Opt. Fiber Commun. Conf., (San Francisco, CA, USA), no. Tu2J.2, Mar. 2025.

M.V.R. Murty et al., "Towards 200G per Lane VCSEL-based Multimode Links," in Proc. Opt. Fiber Commun. Conf., (San Diego, CA, USA), no. M2D.3, Mar. 2024.

X. Wang et al., "100GHz Ultra-thin Germanium Photodetector with 1.05A/W Responsivity at 1550nm," in Proc. Opt. Fiber Commun. Conf., (San Francisco, CA, USA), no. M4K.2, Mar. 2025.

D.-J. Kim et al., "3-dB Bandwidth Enlargement of an InGaAs Photodiode by Inductive Signal Electrode," in Proc. OptoElectron. Commun. Conf. and Int. Conf. Photon. Switching Comput., (Sapporo, Japan), June, 2025, pp. 1–3.

R. Mahajan et al., "EMIB-A High Density, High Bandwidth Packaging Interconnect," in Proc. IEEE Electron. Compon. Technol. Conf., (Las Vegas, NV, USA), May. 2016, pp, 557–565.

S. Daudlin et al., "Three-dimensional photonic integration for ultra-low-energy, high-bandwidth interchip data links," Nat. Photon., vol. 19, 2025, pp. 502-509. doi: 10.1038/s41566-025-01633-0

C. Batten et al., "Building Manycore Processor- to- DRAM Networks with Monolithic Silicon Photonics," in Proc. IEEE Symp. High Perform. Interconnects, (Stanford, CA, USA), Aug. 2008, pp. 21–30. doi: 1109/HOTI.2008.11

S.-J. Yun et al., "Enhancement of RF performance of 128-Gbaud lumped-EML submodule utilizing LC resonance with capacitive wire-bonding pad," in Proc. Opt. Fiber Commun. Conf., (San Francisco, CA, USA), no. W2A.2, Mar. 2025.

그림 1

플러그어블에서 CPO까지 진화

출처 ETRI Webzine, “빛을 이용한 초고속 통신의 시대를 열다,” 2023. 2. 7. https://blog.naver.com/etripr/222996077089

그림 2

도 및 (d) 각 모듈별 라인카드 배치 (c) (d)그림 2 (a) 플러그어블 광트랜시버, (b) OBO, (c) CPO 모듈 개념도, (d) 각 모듈별 라인카드 배치 형태

그림 3

SOA 집적 1.3μm 고출력 DFB 레이저(Sumitomo)

출처 Reproduced from W. Tian et al., “Progress in Research on Co-Packaged Optics,” Micromachines, vol. 15, no. 10, 2024, pp. 1–24.

그림 4

SOA 집적 4파장 DFB 레이저 집적 SiPh 광송신기 PIC(Intel)

출처 Reprinted with permission from S. Liu et al., “Silicon photonics DWDM transmitter with heterogeneously integrated multiwavelength DFB laser and SOA,” J. Lightwave Technol. 43, 2025, pp. 1855-1860.

그림 5

실리콘 포토닉스 기반의 광변조기: (a) Mach-Zehnder 간섭계 기반 광변조기, (b) 마이크로 링 공진기 기반 광변조기

high-speed communications and photonic signal processing,” npj Nanophoton., vol. 1, no. 27, 2024.

(b) Reprinted with permission from D.W.U. Chan et al., “C-band 67 GHz silicon photonic microring modulator for dispersion-uncompensated 100 Gbaud PAM-4,” Opt. Lett. vol. 47, no. 11, 2022, pp. 2935–2938. © Optica Publishing Group

그림 6

CPO 광원: (a) IBM&II-VI, (b) Ranovus, (c) Intel, (d) Ayar-labs, (e) Hengtong Rockley

출처 Reprinted from M. Tan et al., “Co-packaged optics (CPO): status, challenges, and solutions,” Front. Optoelectron., vol. 16, no. 1, 2023, pp. 1–40.

표 1 최근 실리콘 포토닉스 기반 광변조기 성능 지표

| 지표 | 성능 수준 |

|---|---|

| 전기광학 대역폭 | 90GHz @ 3V bias |

| 변조 효율(V·cm) | 0.82V·cm |

| 데이터 전송 속도 | 400Gbps/λ(PAM-4), 3.2Tbps(8ch) |

| 파장 대역폭 | 7nm(1,550nm 중심, 50dB rejection) |

| Cross-talk | -30dB(60GHz), -20dB(90GHz) |

| 소비 전력 | 기존 GPU 대비 10배 효율 |

표 2 광소자 플랫폼 장/단점 및 특징 비교 표

- Sign Up

- 전자통신동향분석 이메일 전자저널 구독을 원하시는 경우 정확한 이메일 주소를 입력하시기 바랍니다.